# FPGA提供了什么价值？

## ——“FPGA五问五答”系列报告——

2023年4月17日

看好/维持

电子

行业报告

分析师

李美贤 电话: 13718969817 邮箱: limx\_yjs@dxzq.net.cn

执业证书编号: S1480521080004

### 投资摘要:

**FPGA** (可编程逻辑门阵列) 又称“万能芯片”，美国禁运后，作为最“卡脖子”的芯片之一而家喻户晓。虽然全球市场规模只有 80 亿美元，FPGA 这个不大不小的市场却撑起了龙头赛灵思近 500 亿美元的市值（英特尔平均市值在 2000 亿美元上下，所在市场规模是 FPGA 的 10 倍）。目前，全球 90% 的市场份额由美国 FPGA 厂商垄断，国产替代必要性不言而明。美国禁运后，国产 FPGA 厂商迎来发展的历史性机遇。FPGA 究竟有什么价值？什么在驱动它的未来的成长？龙头为什么能有这么高的市场份额？护城河在哪里？本土厂商又要如何培育自己的竞争优势？针对这些问题，我们复盘了 FPGA 三大厂商：赛灵思、Altera 和 Lattice 的发展历程，总结出了核心规律，并在 FPGA 五问五答系列报告中逐一为投资者解答。

作为我们 FPGA 五问五答第一篇，在这篇报告中，我们首先回答一个最关键的问题——FPGA 提供了什么价值？

为了回答这个问题，我们仔细研究了 FPGA 和其他处理器的架构演变和历史，回答如下：FPGA 无可比拟的灵活性，以及确定性的低时延优势，是 FPGA 难以被替代的原因，也是 FPGA 为客户提供的一无二的价值。

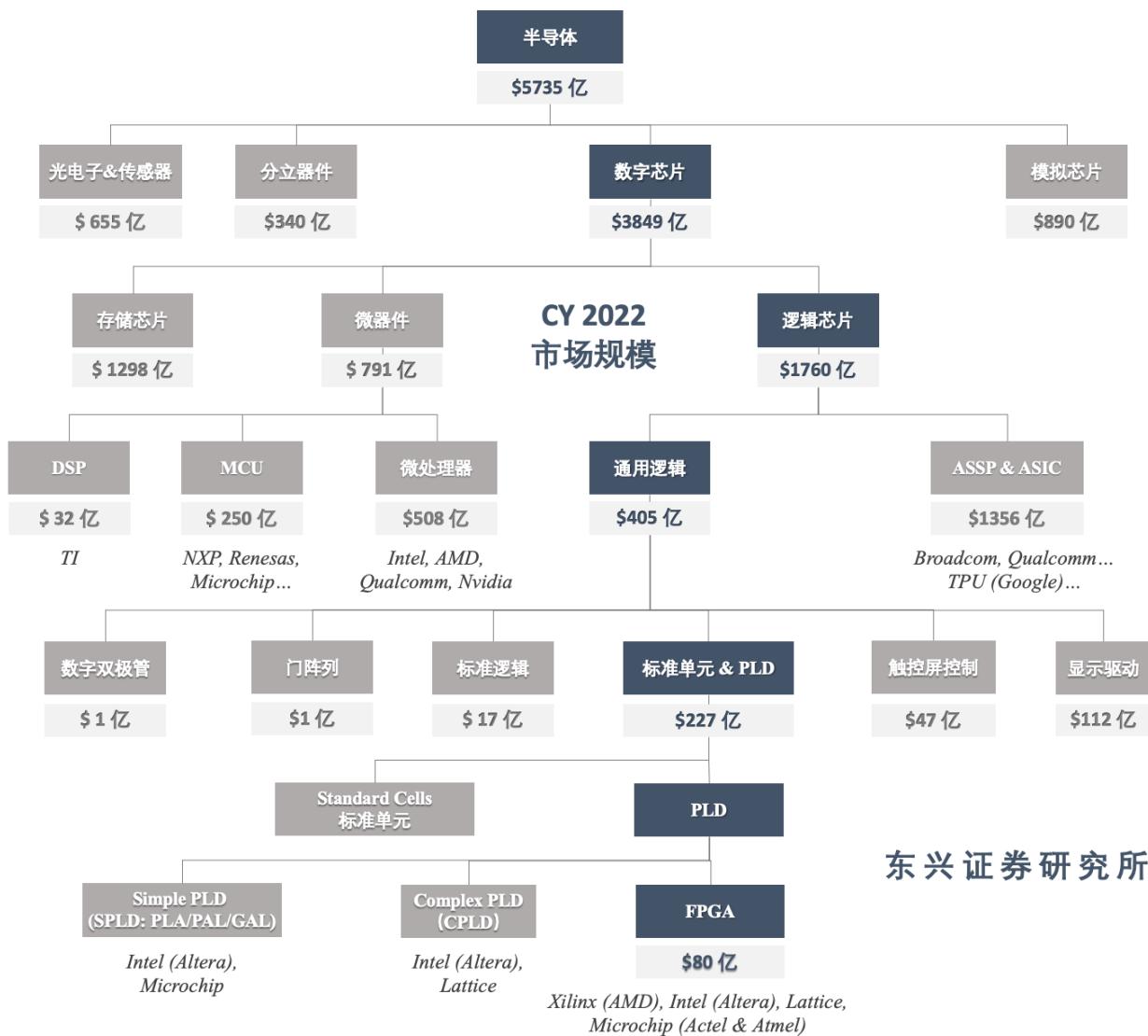

**FPGA 是什么？在半导体产业链中的位置？** 芯片分为模拟芯片和数字芯片，数字芯片负责处理数字信号，分为处理器、逻辑、存储三大类。FPGA 是可编程的逻辑芯片，和其它逻辑芯片的不同之处在于，用户可以随时定义其硬件功能。虽然 FPGA 市场仅占逻辑芯片的 5%，市场规模仅有微处理器的大约十分之一，但在许多领域是不可或缺的。

**FPGA 为什么在历史上脱颖而出？** PLD 诞生的动因来自于 ASIC 和 ASSP 的不足，通过可编程来满足降低芯片设计风险的需求。FPGA 并不是第一个被创造出来的可编程逻辑器件，但由于 FPGA 的架构弥补了 PLD 和 ASIC/ASSP 的缺环，能够满足下游不断增长的容量和速度的需求，在发明后的 10 年开始飞速替代 SPLD 和 CPLD，成为独占鳌头的可编程逻辑器件。

**FPGA 如何做到“万能”？** 数字电路有两大类：组合电路和时序电路，时序电路即“组合电路+存储”。所有组合电路都有对应的真值表，FPGA 的可编程逻辑块中的 LUT，本质上是一个对应真值表输出的查找表，可以完成任意组合电路的功能。通过改变 LUT4 里面的 16 位掩码，就能灵活地对应不同的组合电路，再结合寄存器等存储单元，可以完成时序电路的功能，从而实现任意电路的“可编程”。

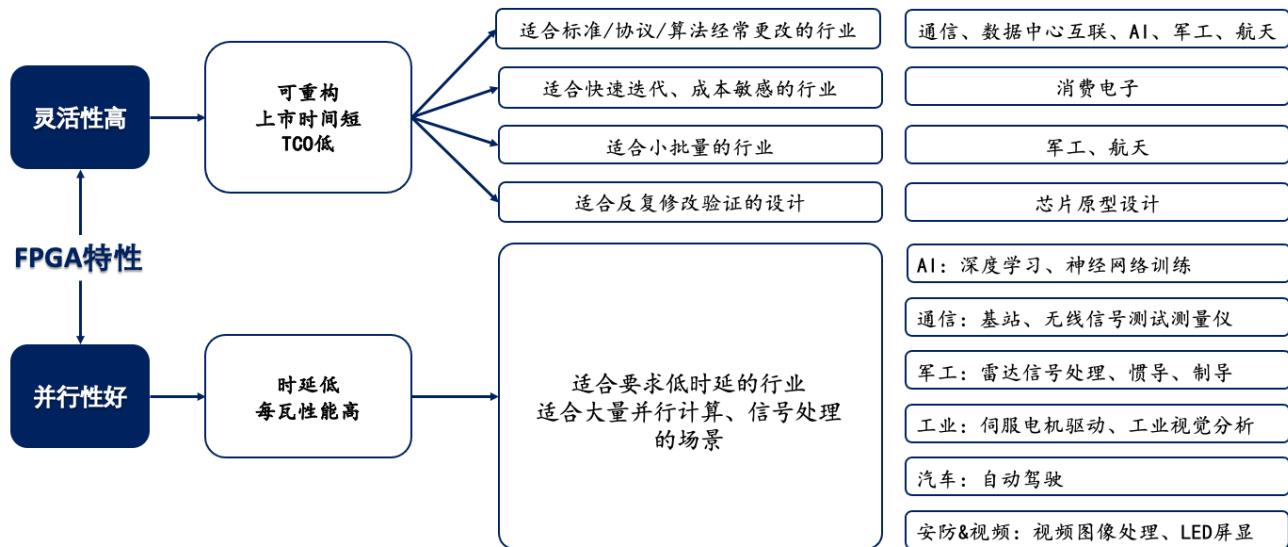

**FPGA 独一无二的价值在哪里？** 1) 灵活性高，适合高速迭代的场景（能“经常改”）：FPGA 可以实现任何电路功能，其耗时甚至不超过一秒，修改不限次数，这一特性尤其适合以下 4 种场景：标准/协议/算法经常更改的行业，快速迭代、成本敏感的行业，小批量的行业，以及反复修改验证的设计；2) 并行性好，适合要求低时延和大量并行计算的场景（“算得快”）：FPGA 内部数十万个 CLB 可以同时独立工作，实现大规模的并行计算耗时极短，由于不存在线程或者资源冲突的问题，FPGA 的时延是确定的低时延，特别适合低时延的场景。

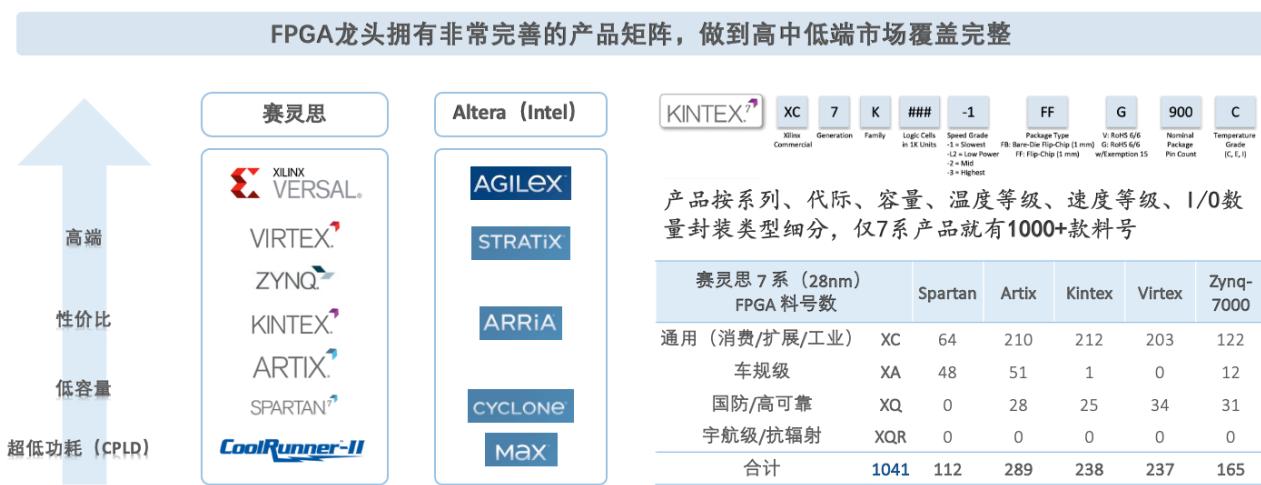

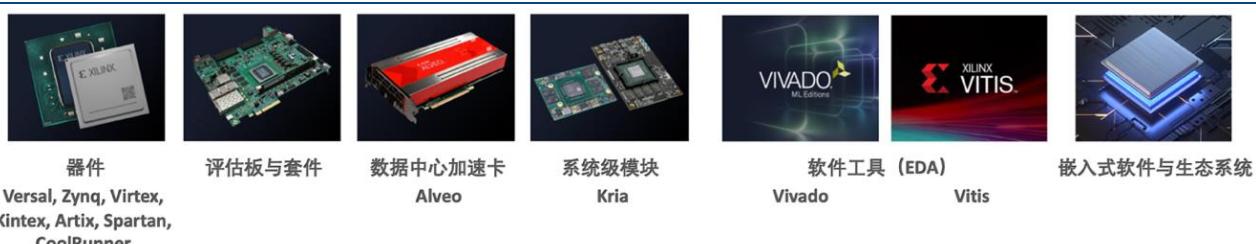

**什么是“好”的 FPGA？** 一般来说，FPGA 的制程越先进、逻辑单元数越多、固化功能越复杂，能构造的电路就越大、越复杂，FPGA 越“好”。尽管如此，一块“好”的 FPGA 并不一定是能力上的最优，而是最贴近使用者的需求，因此，龙头对市场做了非常高的细分。以龙头赛灵思为例，其拥有高端的 Virtex，性价比的 Kintex，低容量的 Spartan，超低功耗的 CoolRunner，再加上温度、速度等级等的区别，仅 7 系产品就有高达 1000+ 的料号，产品矩阵非常完备。

**特别地，我们回答了市场对于宇航级 FPGA 的疑惑：**

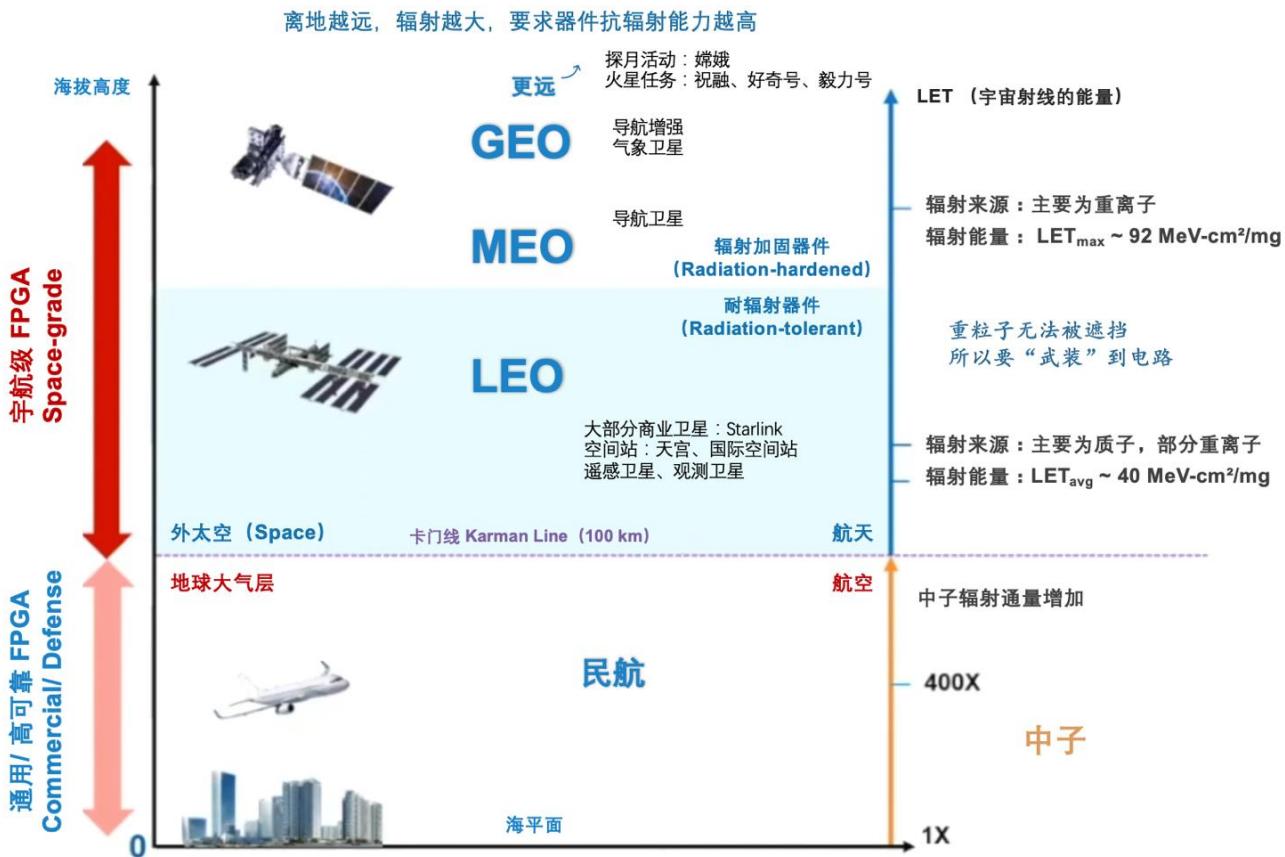

在卡门线以上（海拔高度 100km）运行的电子系统需要使用宇航级 FPGA，由于外太空的航天器接受的辐射量是地面的百倍甚至千倍以上，严重的可致器件损坏，导致在轨任务的失败，航天器需要具备电路级的抗辐射能力。FPGA 的抗辐射能力和航行高度挂钩：在 LEO 高度，使用耐辐射（Radiation Tolerant）FPGA 即可；进入 MEO 或者 GEO 高度，需要使用辐

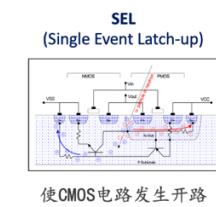

射加固 (Radiation Hardened) FPGA。宇航级 FPGA 主要考虑对总剂量效应和单粒子事件的防护能力，具体指标有 TID 耐性、SEL 阈值、SEFI 发生率和 SEU 发生率。宇航级 FPGA 需要额外使用许多技术，制造的成本高，做到辐射加固级更是需要从设计到制造封测的一系列流程改变，因此价格通常非常昂贵，目前，全球有能力提供宇航级 FPGA 公司屈指可数。过去，星载 FPGA 处理能力落后于商业级 10-15 年，现在已经和商业级接近，背后是不断增长的提升卫星处理能力的需求。

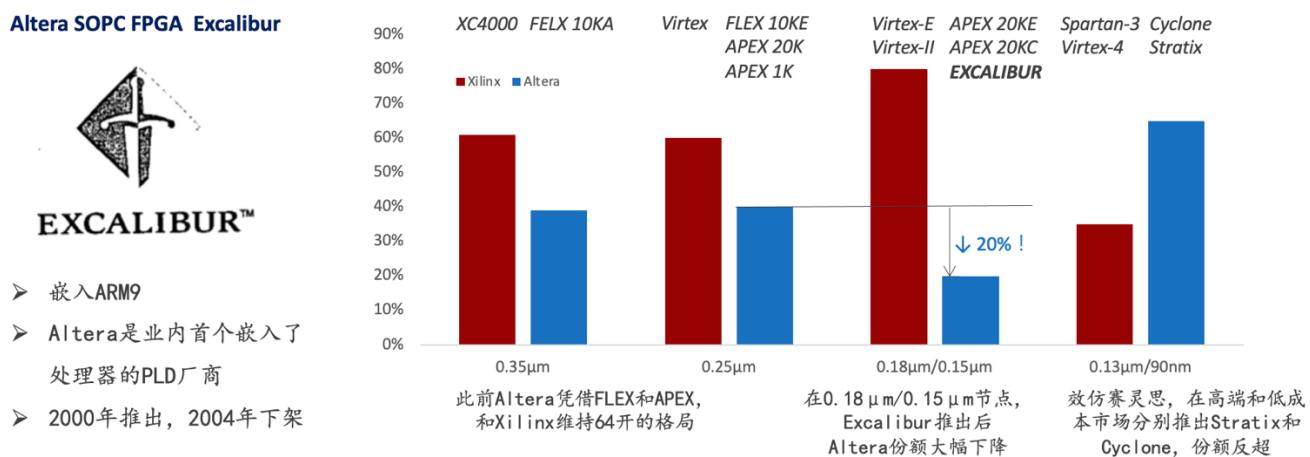

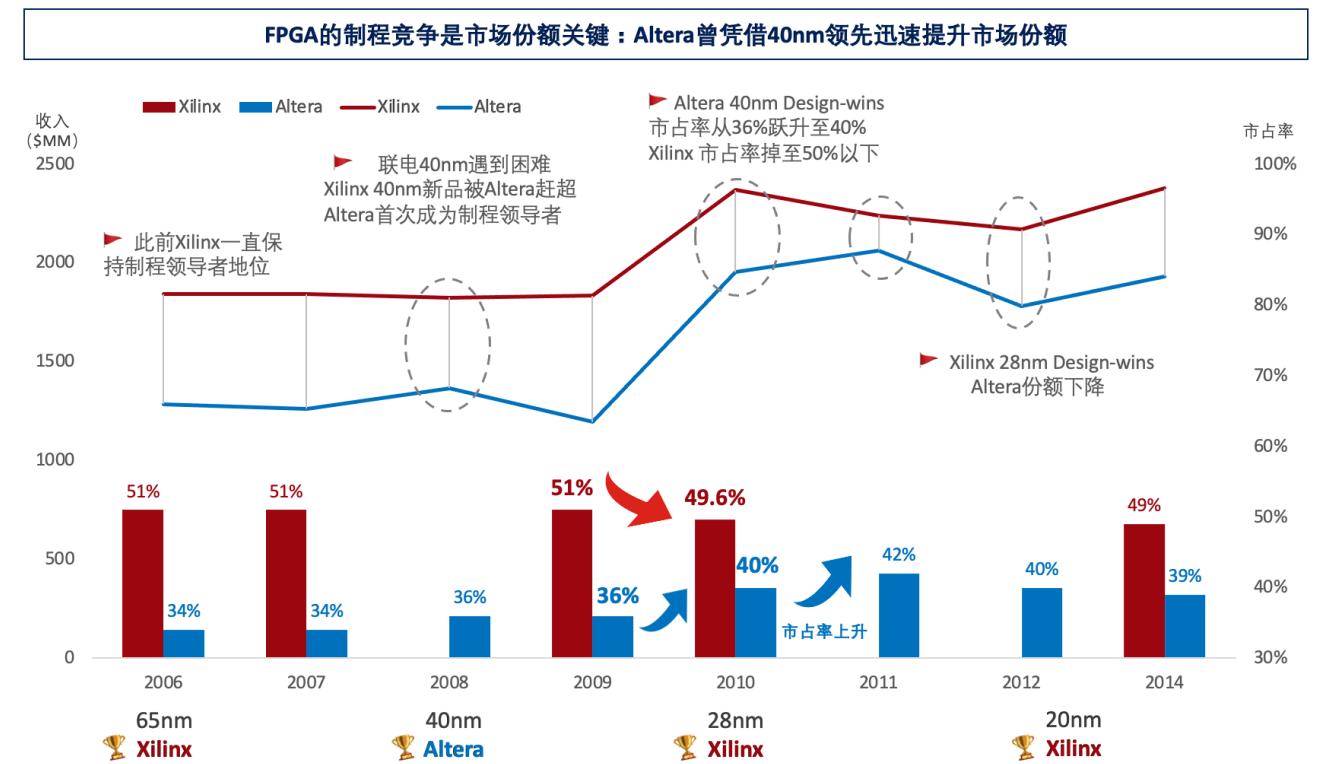

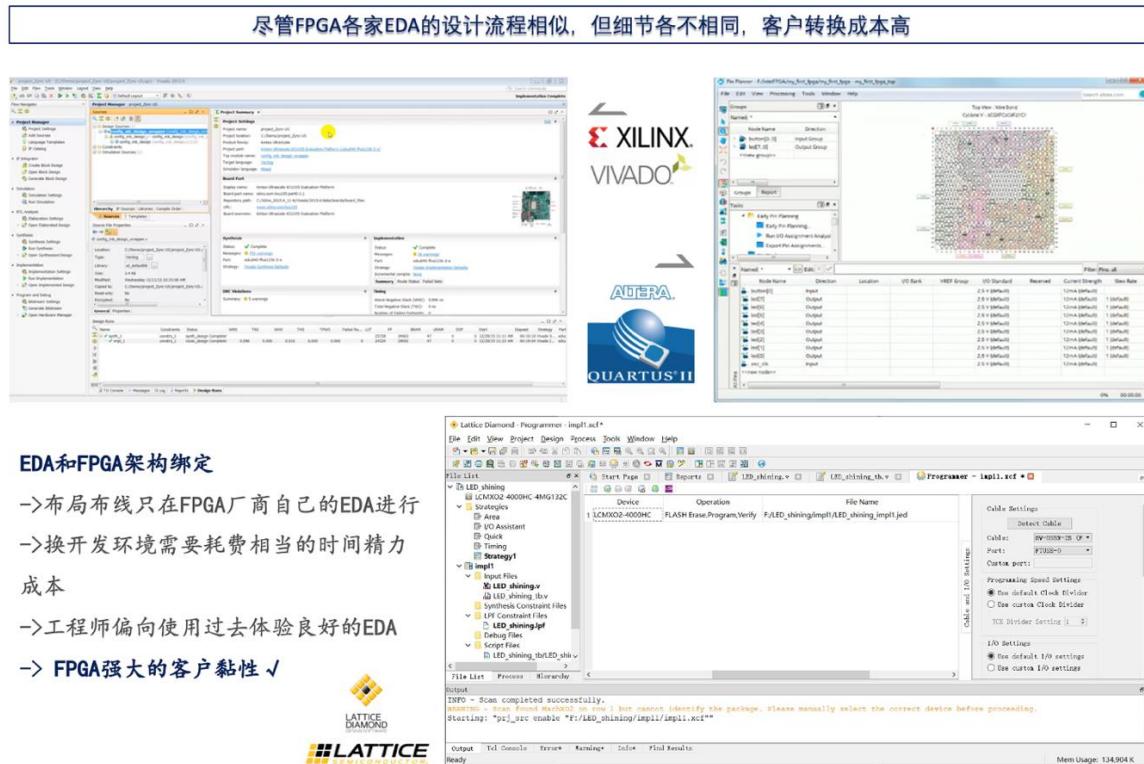

**为什么 FPGA 这么难？**我们认为，**一是产品定义上，FPGA 设计者必须平衡市场上各个需求**，难度在于如何平衡可编程功能和固化功能，需要对客户需求有非常好的了解。我们回顾了 Altera 历史上在 Excalibur 的失败，说明了产品定义和需求匹配的重要性。**二是从技术上，体现在 FPGA 必须跟上最新的制程。**制程领先是 FPGA 市场份额最直接的决定因素。从 Altera 在 40nm 对赛灵思的赶超，可以看出制程领先对 FPGA 的重要性。FPGA 设计不是简单地堆叠逻辑单元，如何排布逻辑单元和各固化单元，来平衡性能提升和面积、时延、功耗之间的矛盾，是非常重要的问题，需要设计者考虑架构的先进性和针对性。**三是 FPGA 硬件和设计工具绑定的特点，使得 EDA 和硬件必须做到并重开发。**FPGA 软件最核心的地方在于布局布线，虽然仿真等工作已经可以由第三方 EDA 完成，但由于架构不公开，并不存在通用的 FPGA 布局布线工具，历史上赛灵思和 Altera 都曾与第三方的 EDA 公司合作优化仿真以及综合的流程，但 布局布线从来只在自家的 EDA 上进行。因此，FPGA 的容量每上一个台阶，就必须更新配套的“映射-包装-布局布线”三大算法。这种硬件和软件高绑定的特点，使得 FPGA 新进厂商在攻克了硬件的诸多技术难点外，还要完成配套软件和复杂的工具包开发，这是 FPGA 的设计难于其它类型芯片的原因，亦是 FPGA 的进入壁垒如此之高的原因之一。

**风险提示：**下游需求不及预期，中美贸易战超预期。

## 目 录

|                                      |    |

|--------------------------------------|----|

| 1. FPGA 在半导体中的位置？如何在历史迭代中脱颖而出？ ..... | 5  |

| 2. FPGA 如何工作？ .....                  | 8  |

| 3. FPGA 特点是能“经常改”和“算得快” .....        | 14 |

| 4. 什么是“好”的 FPGA？ .....               | 16 |

| 5. 设计“好”的 FPGA，难点在哪里？ .....          | 26 |

| 风险提示 .....                           | 31 |

## 插图目录

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| 图 1：FPGA 的特征在于硬件可编程 .....                                             | 5  |

| 图 2：FPGA 实物图（从左到右依次为 Xilinx、Altera、Altera、Actel 的 FPGA/CPLD 芯片） ..... | 5  |

| 图 3：全球半导体市场图谱（2022），FPGA 属于逻辑芯片中的可编程逻辑器件 .....                        | 6  |

| 图 4：FPGA 发明初衷是弥补当时 PLD 和 ASIC 之间的缺环 .....                             | 7  |

| 图 5：自 1985 年发明以来，FPGA 在容量和集成度上不断进化 .....                              | 7  |

| 图 6：SPLD 大多基于与阵列和或阵列，缺点在于在容量扩展时系统极易变得冗余 .....                         | 8  |

| 图 7：FPGA 由可编程逻辑块、可编程连线、及可编程 IO 三部分构成，最重要的“积木”是 LUT 和寄存器 .....         | 9  |

| 图 8：LUT 的 SRAM 的对应真值表的输出，通过配置 SRAM，LUT 可以实现不同的组合电路功能 .....            | 10 |

| 图 9：FPGA 厂商的 EDA 最主要负责将用户描述的电路映射到可编程逻辑块上，并在布局布线上满足时序约束 .....          | 11 |

| 图 10：可编程 IO 负责 FPGA 对外交互，同样是非常重要的部分（以赛灵思 Virtex-7 为例） .....           | 12 |

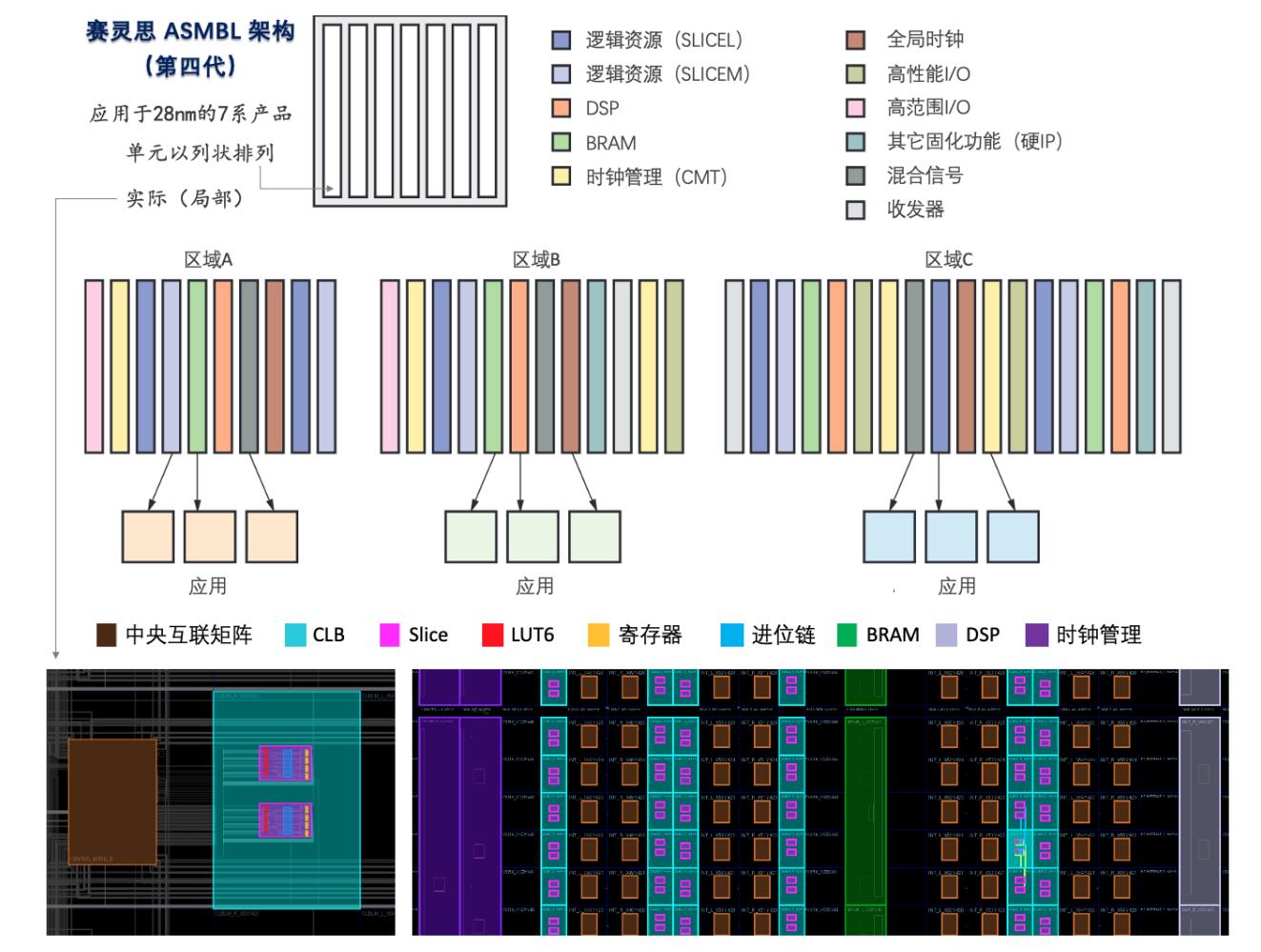

| 图 11：赛灵思 7 系 FPGA 的架构 ASMBL（第四代），典型特点是以列排布 CLB、BRAM、DSP 等的资源 .....    | 13 |

| 图 12：FPGA 灵活性高、并行性好的特点，使其特别适合小批量、时延要求低、变化快的场景 .....                   | 14 |

| 图 13：FPGA 产品大多以“产品组合+制程”的形式命名（下图以赛灵思 FPGA 产品矩阵为例） .....               | 17 |

| 图 14：90 年代，FPGA 厂商在门级规模数上展开竞争，巨头赛灵思和 Altera 均在 90 年代末完成百万门级的跨越 .....  | 18 |

| 图 15：赛灵思和 Altera 的产品矩阵，高中低端市场覆盖完整 .....                               | 20 |

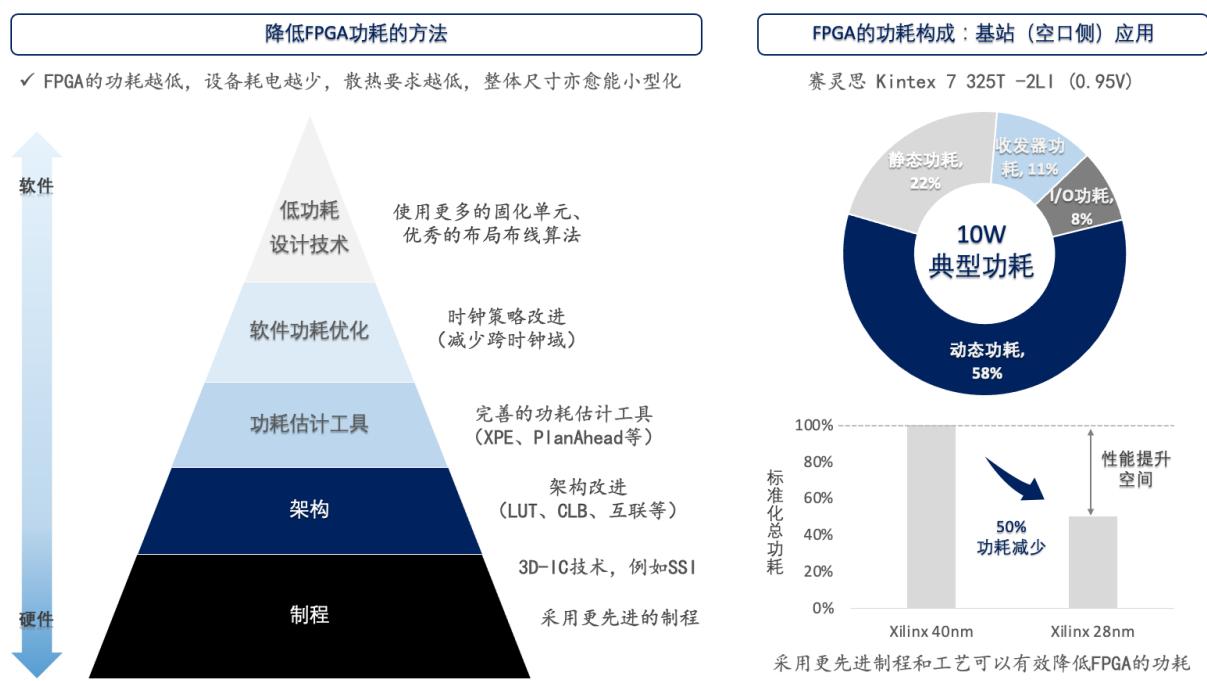

| 图 16：FPGA 的功耗拆分，从硬件上降功耗最为有效 .....                                     | 22 |

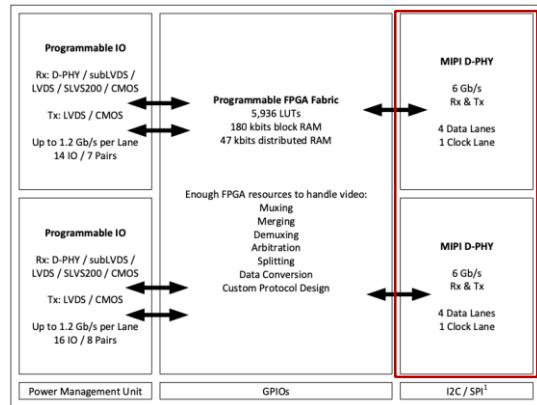

| 图 17：Lattice 的 FPGA CrossLink 嵌入了性能优异的 MIPI 硬核，在安防行业特别受欢迎 .....       | 22 |

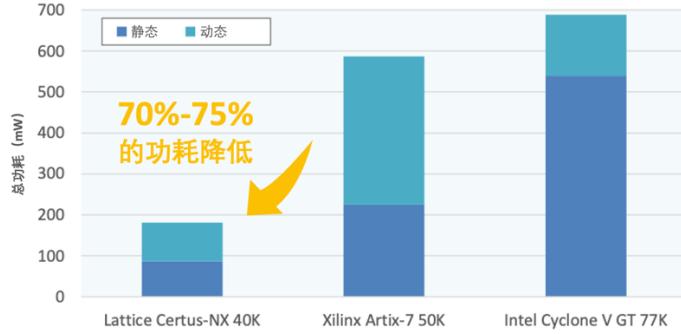

| 图 18：Lattice 在低功耗上的优势明显，在低容量做到功耗比竞品低 70%-75% .....                    | 22 |

| 图 19：外太空环境需要使用宇航级 FPGA，其抗辐射能力和航行高度直接挂钩 .....                          | 23 |

| 图 20：宇宙射线导致的单粒子效应是航天器发生故障的最重要原因 .....                                 | 24 |

| 图 21：离地球越远，FPGA 的抗辐射能力要求越高，使用到的辐射加固技术就越多 .....                        | 25 |

| 图 22：Altera 曾经因为 Excalibur 丢失了大部分市场份额 .....                           | 27 |

| 图 23：FPGA 在最新制程的推出速度，基本可以预测 2 年后的市场份额 .....                           | 28 |

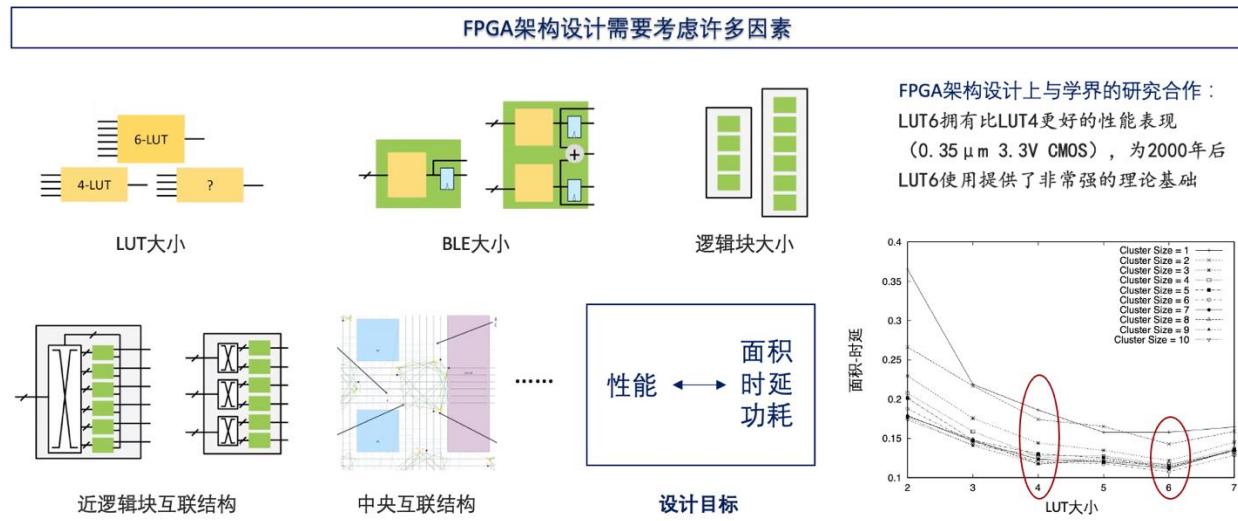

| 图 24：FPGA 的架构设计需要考虑非常多的的因素，赛灵思等巨头与学界紧密合作 .....                        | 28 |

| 图 25：FPGA 和软件绑定的特点，使得 EDA 和硬件同等重要 .....                               | 29 |

| 图 26：全球前三 FPGA 公司的研发费率常年保持 20% 以上 .....                               | 30 |

| 图 27：除了 FPGA 和配套的 EDA，如今的 FPGA 厂商还提供了板级的解决方案，以实现客户快速开发的目的 .....       | 30 |

## 表格目录

|                                                              |    |

|--------------------------------------------------------------|----|

| 表 1：与其它 PLD 不同，FPGA 主要基于 SRAM 技术，使得技术节点总能保持最新 .....          | 8  |

| 表 2：FPGA 的本质是高度标准化的逻辑芯片，相比 ASIC 和 ASSP，PLD 的突出优点在于灵活性高 ..... | 15 |

| 表 3：评价 FPGA 性能的指标可分为逻辑资源、IO 和固化单元的指标，主要考虑制程、逻辑单元数 .....      | 16 |

| 表 4：FPGA 高中低端市场的需求来源，各市场定位性能指标典型值、下游需求及龙头产品组合 .....          | 21 |

## 1. FPGA 在半导体中的位置？如何在历史迭代中脱颖而出？

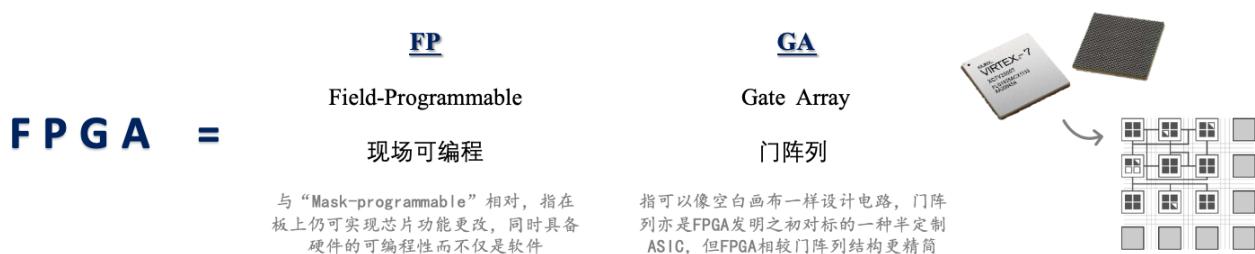

**FPGA** 是一种特殊的逻辑芯片，和其它逻辑芯片的不同之处在于，用户可以随时定义其硬件功能。FPGA 又称现场可编程门阵列（Field-Programmable Gate Array），在 1985 年由赛灵思创始人 Ross Freeman 发明，是在硅片上预先设计实现的具有可编程特性的逻辑芯片。FPGA 的命名反映了诞生时的特征：

- 1) **现场可编程 (Field-Programmable)**: 在 80 年代，芯片的配置大多数保存在掩膜的 ROM 或者 PROM 里，更改芯片功能需要将芯片拆下返回晶圆厂修改，即“Mask-programmable”。而 FPGA 可以使得客户在拿到芯片后，通过本地或者远程配置 FPGA，即在使用的“现场 (Field)”实现。可编程是指 FPGA 底层逻辑运算单元的连线及逻辑布局没有固化，因此可以实现任意数字逻辑功能。虽然 CPU、GPU 都可以实现编程，但这种可编程是指改变其寄存器的配置，用户并不能改变其硬件功能。而 FPGA 可编程的是硬件可编程，内部的逻辑块、连线、I/O 等资源都可以由用户配置，使得同一片 FPGA 既可以在 5G 的基站实现信道编码的功能，也可以在重新配置后放在数控机床中实现电机控制的功能。因此，FPGA 又被称作“万能”芯片。

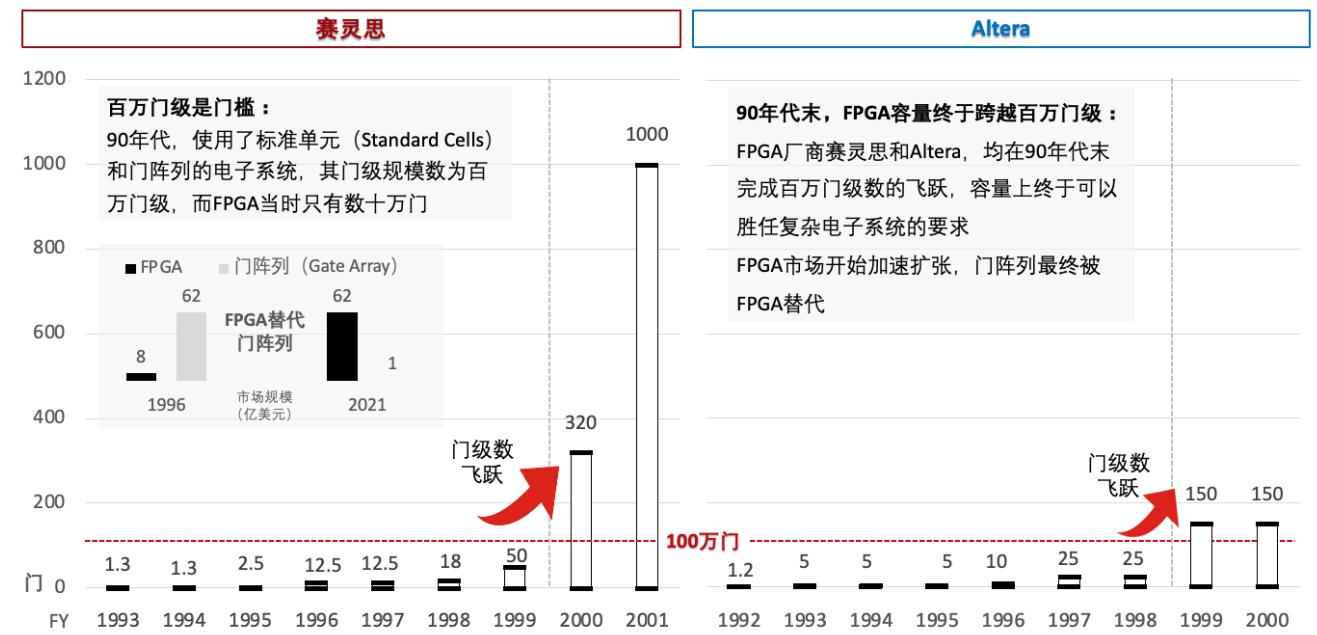

- 2) **门阵列 (Gate Array)**: FPGA 被认为是门 (Gate) 的“阵列 (Array)”，芯片就像一片空白画布一样可以被配置成实现不同功能的电路。同时，门阵列亦是 FPGA 诞生时对标的竞争产品，是一种可定制的 ASIC，但只有布线是可改的，而固化的晶体管是预先放置好的无法更改，而 FPGA 是逻辑单元和布线均可反复更改。门阵列在 90 年代普遍应用在百万门级的复杂电子系统中，而当时 FPGA 的逻辑门数普遍在不超过 25 万门的水平。随着电子系统复杂度提升，门阵列的架构愈发冗余，而基于 LUT 的 FPGA 架构更精简，更能胜任高密度的设计。因此，90 年代末，FPGA 在突破了百万门级的限制后，迅速替代门阵列。

图1: FPGA 的特征在于硬件可编程

资料来源：赛灵思，东兴证券研究所绘制

图2: FPGA 实物图（从左到右依次为 Xilinx、Altera、Altera、Actel 的 FPGA/CPLD 芯片）

资料来源：英特尔，东兴证券研究所

半导体产品可以分为数字芯片、模拟芯片、分立器件、光电子和传感器四大类，数字芯片是最大的市场。其中，光电子&传感器常见产品有激光二极管、压力传感器，2022年全球市场规模为655亿美元；常见的分立器件有IGBT、电容电阻等，2022年全球市场规模340亿美元。在集成电路（IC）中，模拟芯片负责处理时间和幅值都连续的模拟信号，2022年全球市场规模达到890亿美元；而数字芯片负责处理以高低电平代表1-0的数字信号，市场规模3849亿美元，占半导体市场近70%，是半导体中最大的市场。

逻辑芯片是数字电路的主体，负责信号的交互处理。数字芯片主要可以分为三大类：1) 微器件（Microprocessor），即CPU、GPU、MCU、DSP芯片，一般负责控制、计算和信号处理，占数字芯片整体市场规模的20%；2) 逻辑芯片（Logic），负责电子系统内部数字信号的交互和处理，占约45%；3) 存储（Memory），负责存储的指令和数据，占约35%，NAND FLASH、DRAM都是常见的存储芯片。而根据应用范围的不同，逻辑芯片又可分为通用逻辑和特定应用逻辑（ASSP和ASIC）两大类。

FPGA 属于通用逻辑芯片中的可编程器件（PLD），虽然仅占逻辑芯片的5%，但在不少场景中是必须使用的。

图3：全球半导体市场图谱（2022），FPGA 属于逻辑芯片中的可编程逻辑器件

资料来源：WSTS, MarketsandMarkets, 东兴证券研究所整理绘制

例如，在 5G 基站的信号处理、大型芯片的原型仿真等领域会大量使用到 FPGA 芯片。但如今 FPGA 的应用早已脱离出了传统的通信领域，以其独特的高并行高灵活的特性，不断向深度学习拓展渗透，在人工智能时代重要性愈发凸显。尽管 **FPGA** 现在是个相对小众的市场（全球约 80 亿美元），市场规模仅有微处理器的大约十分之一，但以其优越的商业模式，和在人工智能时代的潜力，撑起了龙头赛灵思近 500 亿美元的市值。

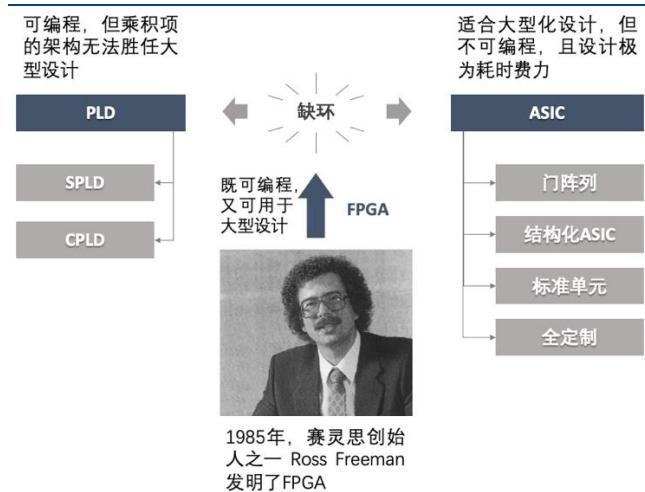

**PLD** 诞生的动因来自于 **ASIC** 和 **ASSP** 的不足，通过可编程，即可“改”，来满足降低芯片设计风险的需求。**PLD** (Programmable Logic Device) 即可编程逻辑器件，在 70 年代 **PLD** 被发明之前，复杂和高性能的电子系统都是由 **ASSP** (Application Specific Standard Product) 或者 **ASIC** (Application Specific Integrated Circuits) 实现的，但 **ASSP** 和 **ASIC** 制造费时且昂贵，制造完成后功能就固定了，一旦出问题便难以更改，因此人们需要一种可以在使用时能更改功能，即“可编程”的器件，以减少设计的时间和风险，**PLD** 应运而生。作为 **PLD** 之一的 **CPLD**，其发明者 **Altera** 公司的名字也体现了这一特点——**Altera** 即“**Alterable**”，指芯片功能是“可更改”的。

图4：FPGA 发明初衷是弥补当时 PLD 和 ASIC 之间的缺环

资料来源：Max Maxfield，东兴证券研究所绘制

图5：自 1985 年发明以来，FPGA 在容量和集成度上不断进化

资料来源：赛灵思，东兴证券研究所绘制

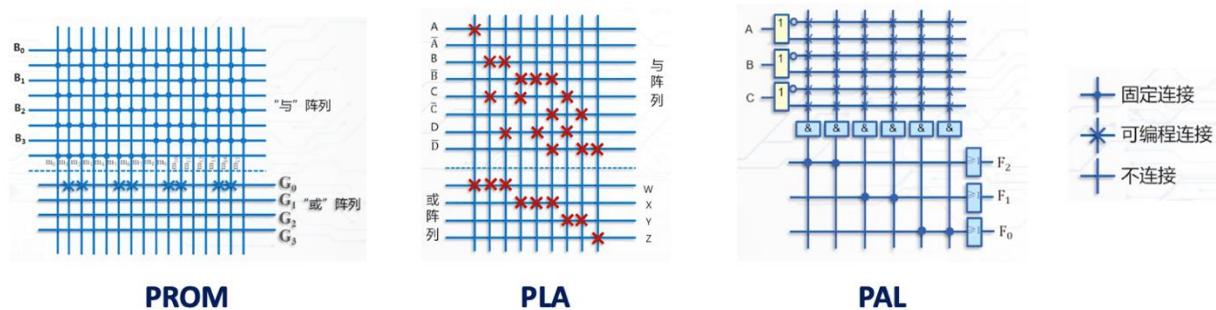

**FPGA** 并不是第一个被创造出来的可编程逻辑器件，但由于其架构能满足不断增长的容量和速度的需求，最终打败了 **SPLD** 等的竞争产品，成为独占鳌头的可编程逻辑器件。1) 第一个 **PLD** 是 **PROM**，诞生于 70 年代，与随后的 **PLA**、**PAL**、**GAL** 架构类似，都是基于“与”和“或”的阵列，因此并称为 **SPLD (Simple PLD)**。其原理是任何逻辑表达式都可简化为“与-或”或者“或-与”的表达形式。优点是编程简便，但阵列式的结构特点，使得输入增加时，芯片体积很快就会变得过大。因此，在 80 年代初，2) **Altera** 发明了 **CPLD (Complex PLD)**，内部用中央连接阵列完成多个 **SPLD (PAL)** 的互联，比全连接节省空间。CPLD 的性能及复杂度要好于 **SPLD**，但由于同样是基于乘积项 (product-term) 的架构，仍无法胜任大型的设计。随后，3) 在 1985 年，赛灵思创始人 **Ross Freeman** 发明的 **FPGA**，在容量和可扩展性上要远好于 **CPLD**，从此弥补了 **PLD** 和 **ASIC/ASSP** 的缺环，即可编程器件在大型系统设计上的缺位，并在发明后的 10 年，即 90 年代后，制造成本大幅降低，开始飞速替代 **SPLD** 和 **CPLD**，现在已几乎成为了 **PLD** 的“代名词”。

发明以来，**FPGA** 不仅逻辑单元数在不断提升，集成度也在不断提高，向异构化发展。世界上第一片 **FPGA** 是赛灵思的 **XC2064**，仅有 64 个逻辑单元，使用 2.5 μm 制程。在摩尔定律加持下，**FPGA** 容量和性能不断提升。如今，赛灵思最先进的产品为 2018 年开始推出的 **Versal** 系列，最高拥有 7532K 的逻辑单元，不仅逻

辑单元数远超第一片 FPGA，形态亦脱离了传统 FPGA 的范畴，包含了 CPU、DSP、AI 引擎等多个单元，是一种包含了 FPGA 的异构计算平台（异构即片上有两种及以上的处理器，一般指集成了 CPU）。

图6：SPLD 大多基于与阵列和或阵列，缺点在于在容量扩展时系统极易变得冗余

### 典型的SPLD (Simple PLD)

原理：基于与阵列和或阵列（乘积项）实现可编程

优点：操作简单

缺点：矩阵式结构，可扩展性差，无法实现大型设计

资料来源：华中科技大学，东兴证券研究所绘制

此外，FPGA 大多基于 SRAM 技术，使其往往容易跟上最新技术节点，最终在 PLD 中脱颖而出。SPLD 大多是基于熔丝 (PROM) 和 EPROM、EEPROM 技术实现可编程，CPLD 大多是基于 EEPROM 或者 Flash，这些技术都往往落后最新节点一代或更多代。而根据配置单元的不同，FPGA 可以分成三类：1) 基于 SRAM 技术的 FPGA，这是 FPGA 的主流技术，虽然 SRAM 易失性的特点使其需要外部的存储来保存配置文件，但由于 SRAM 总在每一代 CMOS 工艺的最前列，SRAM 型的 FPGA 往往能跟上最新的技术节点，这一特点足以抵消需要外部存储的不足；2) 基于反熔丝的 FPGA，最明显的特点是被射线击中后晶体管不易发生“翻转”。但反熔丝资源数少，不适合做复杂的信号处理，因此，在宇航级电子系统中常用于监控和重配置 SRAM 型 FPGA，Actel (现 Microchip 子公司) 的以其反熔丝 FPGA 闻名；3) 基于 EEPROM 或 FLASH 的 FPGA，特点是能立即启动 (Instant-on)，因为他们都是非易失性存储，只要配置过一次就能保持电路状态，但技术节点同样落后 SRAM 一代或更多代。

表1：与其它 PLD 不同，FPGA 主要基于 SRAM 技术，使得技术节点总能保持最新

| 可编程技术           | 相关器件                | 特点                                 |

|-----------------|---------------------|------------------------------------|

| 熔丝/PROM         | SPLD                | 早期的 PLD 技术，现在已经不使用                 |

| 反熔丝 (Anti-fuse) | FPGA                | 抗辐射性强，但无法重新编程，资源数也较少，技术节点落后一代或更多   |

| EPROM           | SPLD、CPLD           | 现在已经很少使用                           |

| EEPROM / Flash  | SPLD、CPLD、部分 FPGA   | 瞬时性高但重编程慢于 SRAM 型，技术节点落后一代或更多      |

| <b>SRAM</b>     | <b>FPGA、部分 CPLD</b> | <b>可扩展性最强，虽然需要外部存储，但技术节点容易保持最新</b> |

资料来源：Max Maxfield，东兴证券研究所

## 2. FPGA 如何工作？

要回答“FPGA 提供了什么价值”的问题，我们需要理解 FPGA 的架构和原理，即 FPGA 是如何工作的？

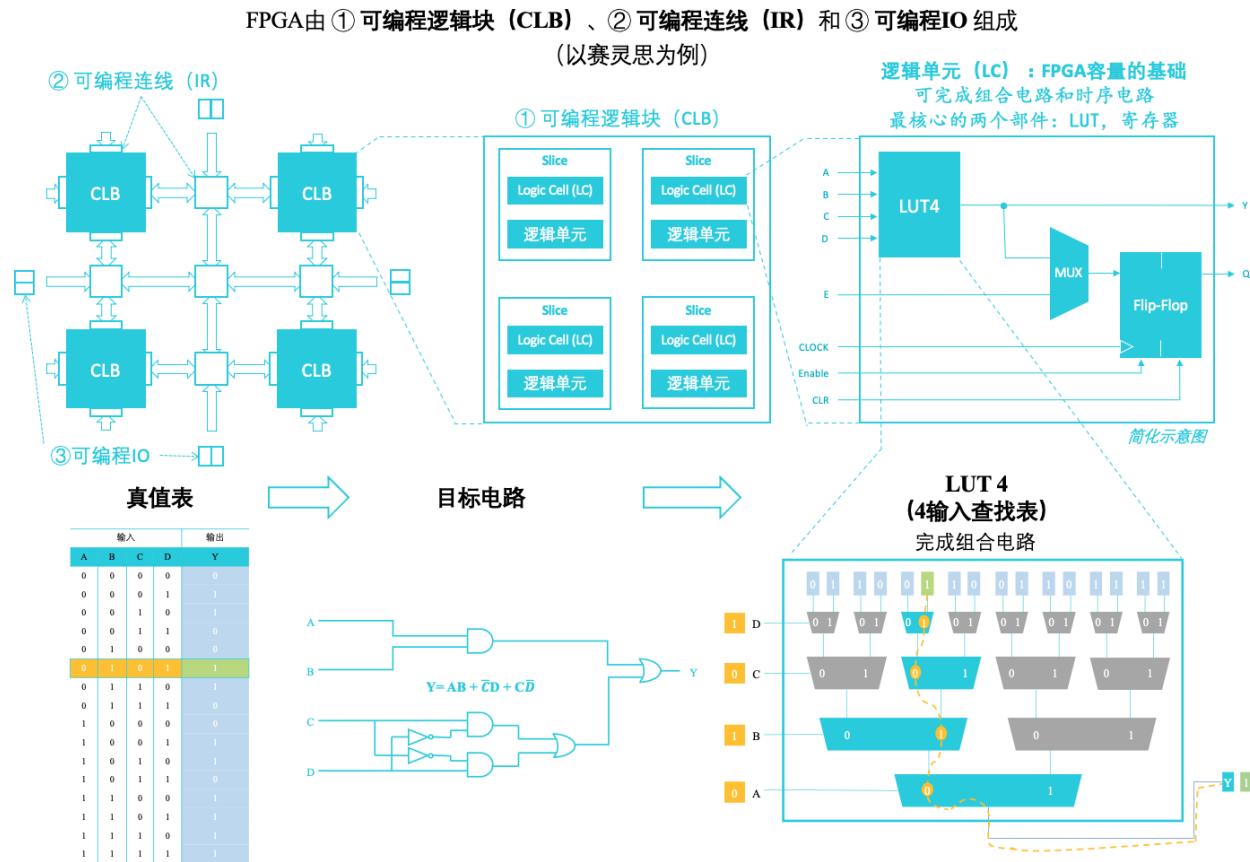

**FPGA** 由可编程逻辑块、可编程连线和可编程 I/O 三大部分组成。其中，1) 可编程逻辑块是 FPGA 架构中最重要的部分，负责承载主要的电路功能；而在电路被映射到各个逻辑块后，预先放置的 2) 可编程连线负责将这些逻辑块以时延最优的方式连在一起，共同构成一个更大规模的电路；最后，由 3) 可编程 I/O 负责 FPGA 与外界交互，可以实现诸如将信号串行解串行、将信号延迟以对准时钟等更复杂的功能。

可编程逻辑块本质上由多个 **LUT**、**MUX** 和寄存器构建而成，用于承载电路中的一个个逻辑“门”。每个厂商对自身 FPGA 的可编程逻辑块的称呼不一样，比如赛灵思是 **CLB** (Configurable Logic Block，可编程逻辑块)，而 Altera 则是 **LAB** (Logic Array Block)。尽管如此，可编程逻辑块中最重要的两块“积木”就是 **LUT** (Look-up Table，查找表) 和寄存器。以赛灵思传统的 FPGA 为例，1 个 CLB 包含了 4 个 Slice，而 1 个 Slice 由 2 个逻辑单元 (**Logic Cell, LC**) 组成。每个逻辑单元包括 1 个 LUT4、若干个多路复用器 (**MUX**) 和 1 个寄存器，可完成时序电路和组合电路，代表 FPGA 的基础容量。现代 FPGA 中往往有数十万个逻辑块，彼此既可前后相连，也可同时独立地处理 IO 输入的信号，不需要耗费时间处理控制指令，这是 FPGA 并行性好的原因。

其中，**LUT** 是 **FPGA** 实现可编程的基础，本质上是一个对应真值表输出的查找表，可以完成任意组合电路的功能。比如，下图中的组合逻辑 ( $Y = AB + \bar{C}D + C\bar{D}$ ) 最少需要 3 个逻辑门实现 (与门、异或门、或门)，在 FPGA 里面需要占用到一个逻辑单元。传统的 FPGA 基本是 LUT4 (四输入的 LUT)，而现代的 LUT 基本是 LUT6 或者 LUT8。除此之外，LUT 可以当作分布式的 RAM 来使用，比如 LUT4 就是一个  $16 \times 1$  的 RAM。

图7：FPGA 由可编程逻辑块、可编程连线、及可编程 IO 三部分构成，最重要的“积木”是 LUT 和寄存器

资料来源：东兴证券研究所绘制

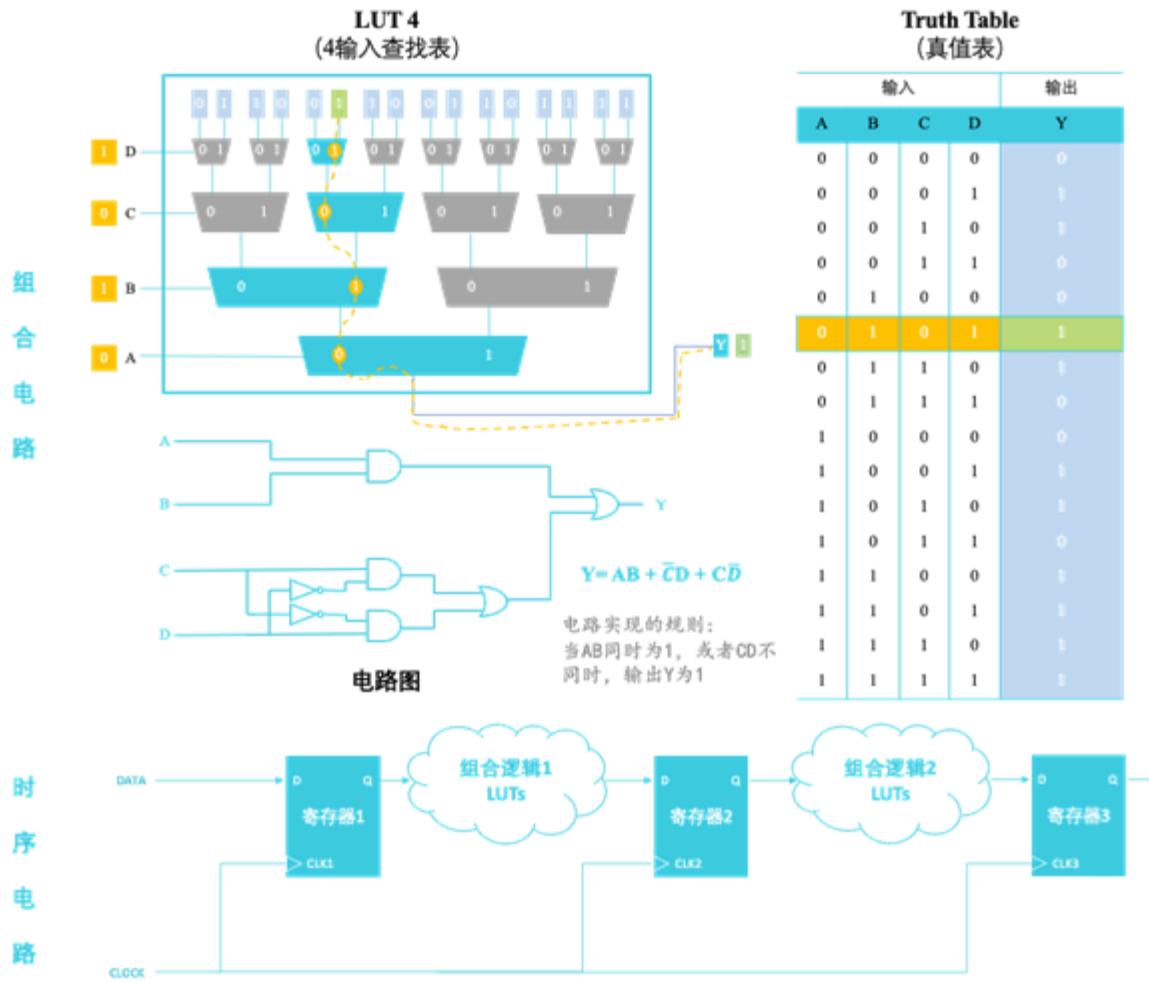

通过改变 LUT4 里面的 16 位掩码，就能灵活地对应不同的组合电路，再结合寄存器，可以完成时序电路的功能，从而实现任意电路的“可编程”。数字电路有两大类：组合电路和时序电路。组合电路的功能就是负责在特定规则下，将输入的信号转换为输出信号。例如，我们规定当 AB 同时为 1，或者 CD 不同时，输出才为 1，否则为 0，这一规则对应的表达式为  $Y = AB + \bar{C}D + C\bar{D}$ 。由于 A、B、C、D 每个变量有“0”和“1”的选项，所以输出有  $2^4$  即 16 种可能，我们将输入和输出的所有可能列出来，就形成了一张真值表(Truth Table)。将真值表中输出的 16 位数值配置到 LUT4 的 SRAM 单元中，我们就能把组合电路映射到查找表中。一个 LUT4 最多能表示 20 个 2 输入的逻辑门，百万甚至千万门级的电路往往是通过可编程连线，将不同的逻辑单元连在一起组合而成。而时序电路即“组合电路+存储”，逻辑单元中的寄存器可以用作存储单元，将组合逻辑的结果送到下一个组合电路的输入端，电路就能像流水线一样同时工作。

图8：LUT 的 SRAM 的对应真值表的输出，通过配置 SRAM，LUT 可以实现不同的组合电路功能

资料来源：东兴证券研究所绘制

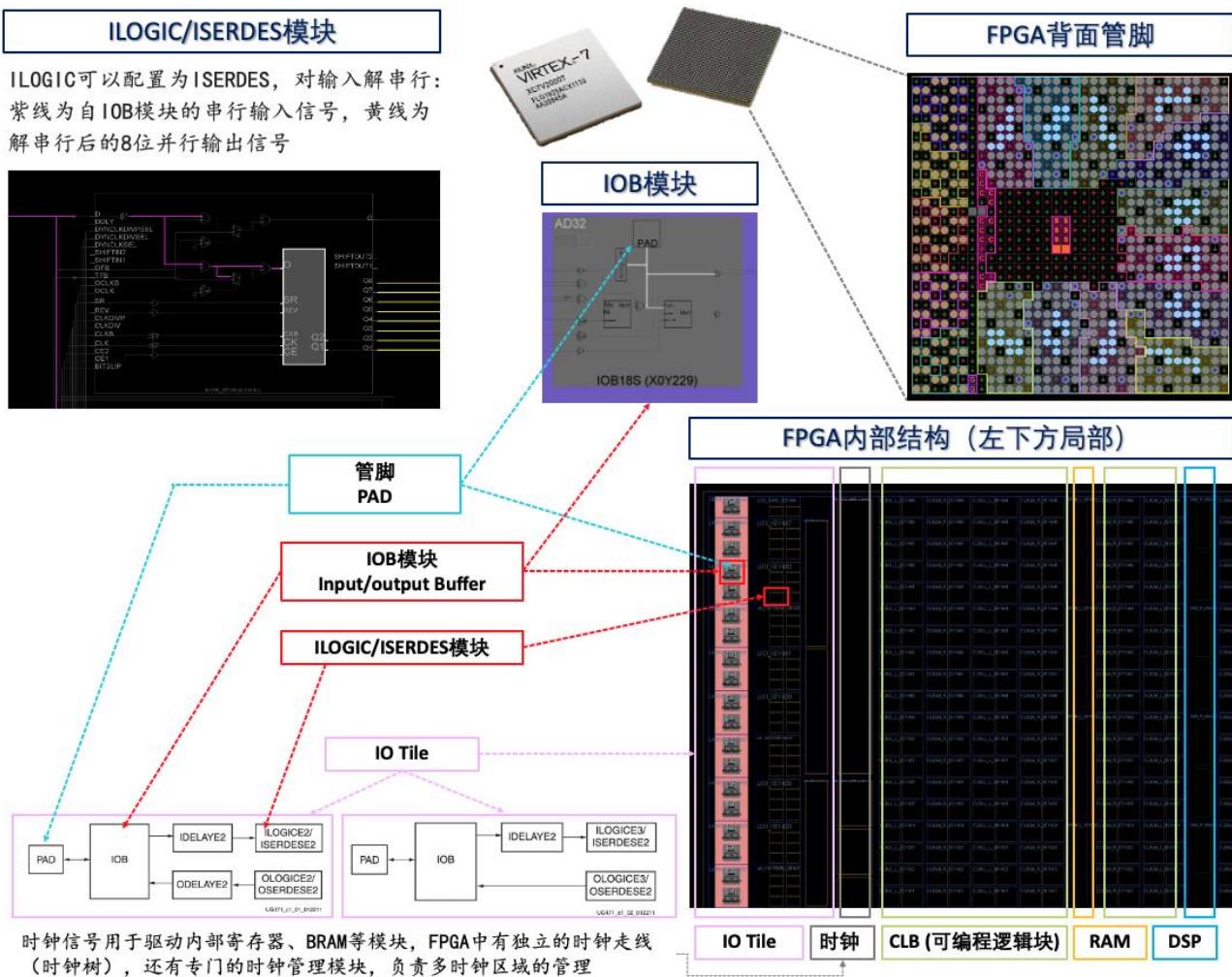

可编程连线负责联通 FPGA 中的众多模块，以一种满足时序约束的方式。将目标电路在 FPGA 上实现，包含了三个最核心的步骤：1) 映射 (Mapping)：将电路的逻辑门映射到不同的 LUT 中，形成 LUT 级网表；2) 包装 (Packing)：将这些 LUT 放置到 CLB 中，形成 CLB 级网表；3) 布局 & 布线 (Place-and-route)：将 CLB 放置在合适的位置并彼此相连。由于数据信号的处理和传输需要时间，时钟信号的传递和变化也需要时间，如果布局和连线的方式不合理，就会出现数据到达下一个寄存器的时间过晚或者过早，即数据采集失

败的情况。大型的电路往往有数十万个 CLB 需要相连，这项复杂的工作由 FPGA 厂商的 EDA 工具负责，例如赛灵思的 Vivado，Altera 的 Quartus，这些 EDA 将电路映射到多个 CLB 上，并且找到合理的布局和连接方式，确保电路能在用户指定的频率上工作，即满足时序约束。因此，连线的可编程性更多地体现在 EDA 软件对于时序约束的满足能力上。如何提高自家 EDA 在映射、包装、布局&布线这三个核心步骤的效率，以减少客户的设计用时（进而培养使用习惯），一直都是 FPGA 公司的研发重点，也是其竞争法宝。

图9：FPGA 厂商的 EDA 最主要负责将用户描述的电路映射到可编程逻辑块上，并在布局布线上满足时序约束

资料来源：MaxField《FPGAs Devices, Tools and Flows》，Vivado，隋文涛《FPGA 布局算法研究》，东兴证券研究所

布局布线是 FPGA 厂商的独门秘籍，是其 EDA 的核心。完整的 FPGA 设计流程包括三大步骤：设计输入（Design Entry）、仿真&综合（Simulation & Synthesis）、实施（Implementation）。“设计输入”指将电路用硬件描述语言（Verilog 或 VHDL）描述，“仿真”即检查描述的电路功能是否完整，“综合”负责电路的映射和包装，“实施”即布局&布线。在随后的静态时序分析（STA）和调试无误后，形成比特流文件下载到 FPGA 中，电路就可以“跑”起来了。尽管 FPGA 厂商的 EDA 工具能提供一套完整的流程，但在设计大型电路时，电路的验证仿真往往交给第三方的 EDA 完成，例如 Mentor 的 ModelSim。而 FPGA 的 EDA 则负责进行下

一步的综合（甚至综合也可以在第三方 EDA 中完成，例如 Synopsys 的 Synplify）。这是由于电路仿真不涉及 FPGA 的具体架构，只需考虑电路功能的完整性。随着电路的大型化和复杂化，这一工作逐渐由第三方 EDA 公司承担。而 FPGA 厂商的 EDA 真正核心之处在于布局和布线。因为布局布线涉及 **FPGA** 的内部具体架构，这是每家 **FPGA** 公司的机密，无法交给第三方完成，这是 FPGA 厂商需要自研 EDA 的根本原因。从 **FPGA** 诞生以来，布局布线就从来只在 **FPGA** 公司的 **EDA** 上进行。

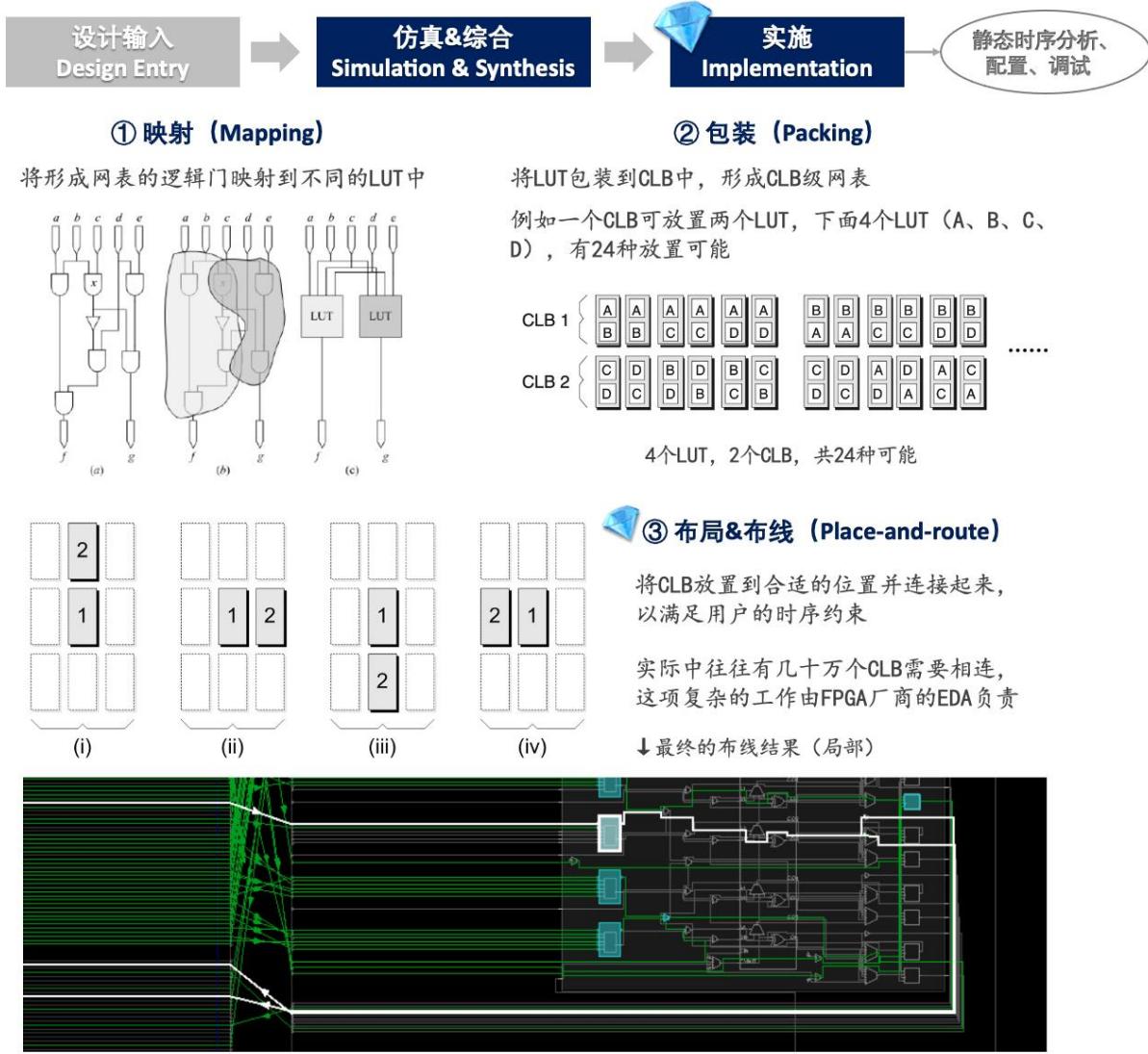

可编程 IO 负责 **FPGA** 和外界的交互，可以对输入和输出信号做复杂的处理。FPGA 通常有几百到上千个管脚，除了时钟、电源和配置的专用管脚外，大部分管脚负责引入或输出信号。**FPGA** 的可编程 IO (IO Tile) 是 **FPGA** 非常重要的部分，由 IOB 模块 (Input/output Buffer) 和紧邻的 IO 逻辑资源共同组成。外界的信号从管脚进入 **FPGA** 的 CLB 之前，首先通过可编程 IO 进行处理。除了可以指定引脚的电压水平和标准外，还能执行许多复杂的处理。例如，将信号延迟输入以对准 **FPGA** 内部的时钟，将信号异步或者同步采集等功能。

图10：可编程 IO 负责 **FPGA** 对外交互，同样是非常重要的部分（以赛灵思 Virtex-7 为例）

资料来源：赛灵思，东兴证券研究所绘制

其中，可编程 IO 中最重要的功能为串行和解串行数据。以赛灵思的 Virtex-7 FPGA 为例，IO Tile 中的 ISERDES 模块可以将输入的串行信号解串行为并行信号，OSERDES 模块可以将输出的并行信号串行，以

进行远距离传输。此外，FPGA 中功能相似位置相近的 IO 接口归为一个“簇 (bank)”，1 个簇包含 50 个 IO 口，因此 FPGA 的 IO 数量一般为 50 的倍数。一个 FPGA 可以有数十个簇，高达 1000 多个 IO 接口。

**现代的 FPGA 是逻辑单元和固化功能的混合体。**除了传统的 CLB 模块外，90 年代开始，FPGA 厂商不断将频繁用到的功能“固化”到 FPGA 中，包括 RAM、DSP、收发器、CPU 等单元，用户可以直接在片上调用，而不是用逻辑单元实现。这一操作可以极大地提高计算效率，避免浪费宝贵的逻辑资源，节省芯片面积。

**图11：赛灵思 7 系 FPGA 的架构 ASMBL（第四代），典型特点是以列排布 CLB、BRAM、DSP 等的资源**

资料来源：赛灵思，东兴证券研究所绘制

除此之外，为了实现更好的性能，现代 FPGA 的逻辑块和互联结构也发生了变化。首先，从可编程逻辑块内部每个查找表的结构来看，主流的 FPGA 从 LUT4 变成 LUT6 或者 LUT8，以减少逻辑块数量、降低走线时延，且内部的输入方式可以按需组合。例如，Altera ALM 中的 LUT8，可以按需划分成任意输入组合；赛灵思 CLB 中的 LUT6，也可以划分成两个 LUT5 使用。其次，逻辑块内部除了 LUT、寄存器、多路选择器这“三大件”外，还添加进了一些固化电路。例如，赛灵思在其 CLB 内部的每个 Slice 里都固化了进位链，以实现更快的算术运算。最后，在互联上，同一个 CLB 内部的 SLICE 互不相连，以避免全连接带来的布线延时。

### 3. FPGA 特点是能“经常改”和“算得快”

在解释完 **FPGA** 的原理架构后，我们来回答第一个问题，即 **FPGA** 给用户提供了什么价值？我们将其总结为能“经常改”和“算得快”：

- 1) 灵活性高，适合高速迭代的场景（能“经常改”）：正如我们前文解答过，只需要改变 **FPGA** 中 LUT 的掩码，一片 **FPGA** 就可以承载另一个电路的功能。因此，**FPGA** 可以实现任何电路功能，其耗时甚至不超过一秒，修改不限次数，这就是 **FPGA** 极高的灵活性特点。**FPGA** 这一特性尤其适合以下 4 种场景：

- a) 标准/协议/算法经常更改的行业，需要支持可重构的系统，例如，无线通信协议经常更改、数据中心互联需要兼容多种协议标准、神经网络算法飞速迭代、军工通信加密方式经常变化、在轨航天器的处理系统动态重构等，类似的场景使用 **FPGA** 能够节省大量的时间和研发成本；

- b) 快速迭代、成本敏感的行业，因为“现场”可用，相比 **ASIC**，**FPGA** 无需等待 三个月至一年的流片周期，上市时间短，对于消费电子这类竞争激烈、迭代迅速的行业尤其重要，像 **Lattice**、赛灵思自 2000 年起都纷纷针对消费电子市场，推出了不少单颗 \$2.5 上下的中低容量的 **FPGA**；

- c) 小批量的行业，芯片 研发阶段的 MASK (光罩) 费用是固定费用，65nm 一次需要 200 万人民币，45nm 需要 430 万人民币，28nm 需要 1000 万。随着制程提升，一次不成功的风险增大。对于年需求量 < 500 万颗的场景，专门为某一应用开发 **ASIC/ASSP**，后续的销售额很难摊平巨大的研发成本。**FPGA** 虽然单价较高，但由于其可以实现任何电路功能，节省了芯片千万级别的研发成本，特别适合小批量的产品，例如国防和航天领域；

图12：FPGA 灵活性高、并行性好的特点，使其特别适合小批量、时延要求低、变化快的场景

资料来源：东兴证券研究所绘制

- d) 反复修改验证的设计，例如，在 **ASIC/ASSP** 的原型设计中几乎都会使用 **FPGA** 进行验证，以发现设计中存在的问题，及时修改，尽可能避免多次流片的风险。芯片原型仿真是 **FPGA** 的“刚需”之一，亦是 **FPGA** 诞生的根本原因，最高端的 **FPGA** 往往会销售给英特尔这些大型的数字芯片公司，供其新一代产品的验证，这一需求亦不断支撑 **FPGA** 走在技术节点前列。

2) 并行性好, 适合要求低时延和大量并行计算的场景 (“算得快”): FPGA 内部数十万个 CLB 可以同时独立工作, 即使时钟频率较低, 其计算效率要远远高于数个高效单元, 特别适合信号处理这种涉及大量并行计算的场景。此外, 由于不存在线程或者资源冲突的问题, FPGA 的时延是确定的低时延, 特别适合低时延的场景。这类场景广泛存在于各个行业, 比如:

- a) 通信行业的基站, 无论是 RRU/AAU, 还是 BBU/DU/CU, 甚至核心网的设备, 都需要用到 FPGA, 实现诸如 Turbo 编码, 协议处理加速等的功能。而在售价数十万甚至百万人民币级别的无线信号测量仪器, 同样会用到单价上万元的高端 FPGA 进行信号的处理控制;

- b) 国防军工行业, 典型场景如雷达数据处理, 需要满足大容量、低延时、高可靠的特性, 才能实现微秒级的处理需求, 而这一时延和稳定性要求只有 FPGA 能达到; 在使用了光纤陀螺的惯性导航系统同样, FPGA 可以对光信号进行低延时控制, 实现光纤陀螺仪高精度、高动态的测量;

- c) 工业: 由于工业有大量的低时延场景, FPGA 在工业领域应用是非常广泛的, 常见于伺服电机驱动, 往往采取 CPU+FPGA 的架构, 以实现微秒级别的控制环路反馈/, 像赛灵思 Zynq 系列(SoC FPGA) 在工业就拥有广泛的应用。此外, 在激光设备中也使用 FPGA 进行皮秒/飞秒激光器的信号控制;

- d) 汽车: 典型的应用在 ADAS 领域, 这是由于 FPGA 比 GPU 时延更低, 能保证更好的制动距离; 除此之外, FPGA 也应用在行车后视镜等场景;

- e) 安防 & 视频: 主要应用在安防高清视频的前端数据采集和低延时处理, 在 LED 屏显同样应用广泛;

- f) AI: 深度学习的模型往往涉及大量的乘法和累加, 特别适合使用 FPGA 并行计算, 以加速训练速度。

换句话说, 相比 ASIC 和 ASSP, PLD 最突出的优点是灵活性高。对于设计电子系统的用户 (例如华为), 其产品内部使用的芯片有三种选择: 自己设计一颗 ASIC、购买例如高通、STM 提供的 ASSP、购买赛灵思的 PLD。ASIC 与 ASSP 的区别在于, ASIC 是针对单一使用者的单一应用设计的, 由使用者定义功能, 而 ASSP 是为多个使用者设计的, 其功能由芯片厂商而不是使用者定义, 因此需要统一的标准。ASIC 的设计费时, 成本也非常昂贵, 但能做到在目标应用的性能最优和功耗最低。ASSP 和 ASIC 的设计流程类似, 但更加通用, 能兼具多个应用场景的性能和功耗。ASIC 和 ASSP 制造后芯片功能就固化了, 以 FPGA 为代表的 PLD, 其芯片功能是可以反复修改的, 虽然性能上不一定是最优, 但灵活性是 ASIC 和 ASSP 所无法比拟的。

**表2: FPGA 的本质是高度标准化的逻辑芯片, 相比 ASIC 和 ASSP, PLD 的突出优点在于灵活性高**

| 标准化程度       | 低          | 高             |

|-------------|------------|---------------|

| ASIC        | ASSP       | PLD (包括 FPGA) |

| 由谁设计/制造?    | 用户自己       | ASSP 厂商       |

| 谁使用?        | 用户自己       | 用户            |

| 可定制? / 可重设? | 用户定制, 不可重设 | 不可定制, 不可重设    |

| 相对上市时间      | 非常慢        | 立即            |

| 相对单位成本      | 最低         | 中等            |

| 客户开发成本      | 最高         | 低             |

资料来源: Altera, 东兴证券研究所

因此，FPGA 无可比拟的灵活性，以及确定性的低时延优势，是 FPGA 难以被替代的原因，也是 FPGA 为客户提供的一无二的价值。

## 4. 什么是“好”的 FPGA？

从 FPGA 作为产品的角度来看，“好”很大程度上意味着“性能高”。由于现代的 FPGA 是逻辑单元和诸如 DSP、收发器、CPU 等固化单元的混合体，除了工艺制程和功耗外，评价 FPGA 的性能指标可分为逻辑资源、IO 资源和固化单元三大类，分别代表 FPGA 在容量、接口以及特定功能上的性能表现。

表3：评价 FPGA 性能的指标可分为逻辑资源、IO 和固化单元的指标，主要考虑制程、逻辑单元数

| 分类                                            | 所属单元                 | 指标                 | 单位 | 含义                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------|----------------------|--------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 首先考虑<br>产品代际                                  | 工艺制程                 | nm                 |    | FPGA 作为数字芯片的一种，本身追逐摩尔定律，使用更先进的制程可以降低功耗、芯片尺寸和单片成本，使得 FPGA 新一代的产品性能一般要优于上一代。FPGA 产品往往以“产品组合+制程代号”的形式命名，方便用户辨别。                                                                                                                                                                                       |

| ①<br>逻辑资源<br>(Logic Cells/<br>Logic Elements) | 逻辑单元数<br>(LCs/LEs)   | k<br>(个)           |    | 逻辑单元是 FPGA 的最小功能单元，包含“一个 LUT4 和一个寄存器”。逻辑单元越多，FPGA 容量越大，能构造的电路就越大、越复杂，往往体现了 FPGA 厂商的技术水平，大型的 FPGA 逻辑单元数基本在 1kk 以上。传统的 FPGA 基于 LUT4，而 2010 年后的 FPGA 大多基于 LUT6 或者 LUT8，因此业内通常以等效为 LUT4 后的逻辑单元数作为可比指标（例如赛灵思的 7 系采用 LUT6，其逻辑资源数通常是 LUT4 的 1.6 倍）。赛灵思通常称呼其逻辑单元为 Logic Cells，而 Altera 的则为 Logic Elements。 |

|                                               | 存储单元<br>容量           | Block RAM<br>Kb/Mb |    | Block RAM 是独立的存储单元。在使用 FPGA 实现算法时，普遍涉及到数据的缓冲、参数的临时存放，需要使用到片上的存储资源。虽然 CLB 中的 LUT 可以作为存储使用，即分布式 RAM (Distributed RAM)，但为了不浪费珍贵的逻辑资源，FPGA 厂商在 90 年代便开始将 RAM 嵌入到 FPGA 中，RAM 也是第一个被固化到 FPGA 中的模块。                                                                                                       |

| ②<br>固化单元                                     | DSP 单元<br>AI 单元      | DSP 数量<br>个        |    | 在使用 FPGA 实现算法时必须考虑的指标。DSP 模块可以实现多数的乘法、加减法、宽位逻辑操作等功能，速度远高于用 CLB 实现，因此 FPGA 厂商在 2000 年初纷纷将 DSP 嵌入到 FPGA 中，现在基本上是 FPGA 的“标配”。                                                                                                                                                                         |

|                                               | 峰值性能<br>INT8         | TOPS               |    | 对于计算密集型的应用 (AI 等)，FPGA 的运算能力也是非常重要的考虑因素，以运算单元每秒执行的操作次数衡量，TOPS 代表每秒 1 万亿次操作。低精度下，算力可以有成倍以上的提升，使得精度降低的损失可忽略不计，因此现在一般用 8 位整型精度 (INT8) 下每秒操作次数衡量，替代的精度指标包括 FP32 (32 位浮点精度)、FP16、FP6 等。                                                                                                                 |

|                                               | 收发器<br>(Transceiver) | 收发器速率<br>Gb/s      |    | 指收发器的传输速率，速率越高，数据传输量越大，收发器在高速数据处理中必须使用，在通信及数据中心应用中是非常看重的指标，是第二个被固化到 FPGA 的器件。                                                                                                                                                                                                                      |

|                                               | 处理器                  | 有无嵌入               | -  | SoC 级别的 FPGA 通常会嵌入处理器模块，将板上本来由单独的 CPU 芯片承担的控制功能放到 FPGA 中，以节省板上空间，提高计算效率。除了 ARM 之外，常见的嵌入到 FPGA 的处理器单元有 NIOS (Altera)、RISC-V 等。                                                                                                                                                                      |

|                                               | 接口                   | 固化接口数量             | -  | 固化的接口可以提高 FPGA 和外部交互的速度。嵌入的固化接口越多，FPGA                                                                                                                                                                                                                                                             |

|           |          |                                                                                                                                                                                  |

|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 和等级      | 的功能就越复杂。除了最常用的 PCIe 接口，还有比如 DDR、MIPI、Interlaken、以太网接口等。                                                                                                                          |

| ③ 可编程 I/O | I/O 数量 个 | IO 可以直连 CLB (引脚绑定)，因此 IO 数量越多，FPGA 能完成的功能也越多，是在接口和并行处理场景非常看重的指标。FPGA 的架构使其在 IO 数量上非常有优势，一般能达到数百个级别，而 MCU 通常只有数十个。                                                                |

| 速度等级      | -        | FPGA 的速度等级越高，LUT、寄存器处理时间更快，FPGA 的性能就越好，整体设计就能运行得更快。速度等级与 FPGA 的制造工艺相关。                                                                                                           |

| 功耗        | W (瓦)    | FPGA 的总功耗由静态功耗、动态功耗和 IO 功耗构成。芯片功耗越低，设备的耗电就越少，散热要求越低，整体尺寸亦愈能小型化。终端设备普遍拥有功耗预算，例如，嵌入式处理功耗一般要求不超过 50W。除了通过更先进的工艺降功耗之外，FPGA 厂商的架构、优化的布局算法、内部信号控制等也能有效降低功耗，在同样性能下，更低功耗的 FPGA 往往更受客户青睐。 |

注：由于各家 FPGA 厂商对自家嵌入了处理器、AD/DA 等的 SoC 级 FPGA 称呼不一，例如赛灵思的 MPSoC/RFSoC，Altera 的 SoC FPGA，还有 SoPC、PSoC、FPSoC 等等，为了统一名称，我们在文中统称为 SoC FPGA

资料来源：东兴证券研究所整理

工艺制程是区分每一代的 **FPGA** 标准，是评价 **FPGA** 首先考虑的指标。FPGA 作为数字芯片的一种，本身追逐摩尔定律，平均每 2-3 年就要推出新一代的产品。使用更先进的制程可以降低功耗、芯片尺寸和单片成本，使得 **FPGA** 新一代的产品性能一般要优于上一代。因此，评价 **FPGA** 首先要考虑其制程。工艺制程对于 **FPGA** 非常重要的另一个原因在于，**FPGA** 通常是大规模 ASIC/ASSP 原型仿真的工具，因此必需跟上最先进的制程（正如我们前文提到过，**FPGA** 大多基于 SRAM 单元，使其非常容易跟上最新的技术节点）。

基于这一点，**FPGA** 产品往往以“产品组合+制程代号”的形式命名，方便用户辨别。以赛灵思为例，其 45nm 的 **FPGA** 称为“6”系列，28nm 的 **FPGA** 称为“7”系列，例如 Virtex 7、Kintex 7 等，20nm 及更先进制程的 **FPGA** 则不再使用数字命名，例如 20nm 的 **FPGA** 为“Ultrascale”系列，16nm 的 **FPGA** 后缀为“Ultrascale+”。而使用了台积电 7nm FinFET 工艺的 Versal 是目前赛灵思最先进的产品，系包含了 **FPGA**、CPU、GPU、DSP 等器件的异构计算平台，由于其形态脱离了 **FPGA** 的范畴，因此不再使用传统的命名方法了。对于 Altera 来说同样，“V”代表 28nm 的产品，例如 Stratix V，Arria V，而其 14nm 的产品名后缀则为“10”，在被英特尔收购后，采用英特尔 10nm 工艺 (Intel 7) 产品则使用“Agilex”统称，对标赛灵思 7nm 的 Versal。

图13：FPGA 产品大多以“产品组合+制程”的形式命名（下图以赛灵思 FPGA 产品矩阵为例）

| 6系<br>45nm                                                                                                  | 7系<br>28nm                                                                                                 | UltraScale<br>20nm                                                                                                       | UltraScale+<br>16nm                                                                                                         | Versal<br>7nm                                                                                                               |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| <br>SPARTAN <sup>6</sup> | <br>VIRTEX <sup>7</sup> | <br>VIRTEX <sup>7</sup><br>UltraSCALE | <br>KINTEX <sup>7</sup><br>UltraSCALE+ | <br>ARTIX <sup>10</sup><br>UltraSCALE+ |

| <br>ZYNQ                 |                                                                                                            |                                                                                                                          | <br>ZYNQ <sup>10</sup><br>UltraSCALE+  | <br>XILINX<br>VERSAL                   |

注：1) 虽然赛灵思在去年初被 AMD 收购，目前业内仍习惯保留赛灵思的称呼。Altera 在 2015 年被 Intel 收购，目前新旧称呼皆有。为了方便与历史比较，我们在全文中整体沿用 Altera 的名称，对于 15 年被收购之后的新产品和技术，例如 Agilex，则使用 Intel 称呼；2) Zynq 是赛灵思 SoC 级别的 FPGA，嵌入了 CPU，其 UltraScale+ 分为 MPSoC 和 RFSoC 两类；3) Versal 是赛灵思最新的产品，为异构计算平台，包含 7nm 可编程逻辑、AI 引擎、CPU、GPU 等。

资料来源：赛灵思，东兴证券研究所绘制

**逻辑单元数代表 FPGA 的基础容量，是目前评价 FPGA 基础容量的统一指标。**ASIC 的最小功能单元是“门”，因此其容量以门级数规模衡量。而 FPGA 的最小功能单元被称为基础逻辑单元（学界称 BLE，Basic Logic Element；FPGA 厂商称之为逻辑单元（Logic Cell）），包含一个 LUT 和一个寄存器。正如我们前文提到过，FPGA 实现可编程的基础是 LUT，本身可实现组合电路，配合寄存器可以完成时序电路，即一个逻辑单元拥有完成所有数字电路功能的能力。所以，逻辑单元数量越多，FPGA 容量越大，能构造的电路就越大、越复杂。

**大容量 FPGA 直接体现 FPGA 厂商的能力，能持续供应的厂商屈指可数。**大型的 FPGA 逻辑单元数基本在 1kk 以上，这是因为逻辑单元数超过 1kk，需要包括 LUT、CLB、互联在内的 FPGA 架构的更改，否则功耗和时延就会高到不可接受。此外，还需要 EDA 工具配套设计流程、布局布线算法的迭代。因此，大容量 FPGA 的设计难度远超中小容量 FPGA。是否拥有大型 FPGA 产品，往往是 FPGA 厂商能力的直接体现，能做到的厂商屈指可数。目前，全球排名前五名的 FPGA 厂商中，只有赛灵思和 Altera（Intel）两家有能力持续提供大容量的 FPGA 产品线。

过去，FPGA 厂商曾经使用门级数规模来衡量 FPGA 的容量，但从 2000 年后就逐渐转用统一的“逻辑单元数”指标了，这是因为：1) 门级规模数是 FPGA 容量的间接指标，逻辑单元数量才是 FPGA 容量的直接指标，90 年代末，FPGA 在门级规模数上比肩门阵列等竞品，没必要再转换为竞品的评价指标了；2) 为了满足日益增长的性能需求，FPGA 内部的 LUT 结构和集成度不断变化，转化为门级数越来越困难。

图14：90 年代，FPGA 厂商在门级规模数上展开竞争，巨头赛灵思和 Altera 均在 90 年代末完成百万门级的跨越

注：赛灵思财年结束日在每年的 4 月初（比自然年晚约一个季度），而 Altera 则大致为每年 12 月底（基本对准自然年）

资料来源：赛灵思，Altera, WSTS, FMI Research, Dataquest, 东兴证券研究所绘制

门级数竞争是 FPGA 厂商第一阶段的竞争主线(1985-2000)。替代 ASIC 的背后是性能提升的需求。

FPGA 诞生目的是为了替代门阵列等的 ASIC，其容量指标是门级数规模，出于这个考虑，90 年代初，FPGA 厂商普遍将产品内部的逻辑容量转化为门级数规模，方便用户比较。在当时，复杂的电子系统要求百万门级的规模，大多使用标准单元和门阵列实现，而 FPGA 当时容量只有 20-50 万门，无法进入高端市场。鉴于此，90 年代，FPGA 厂商纷纷在门级数上展开竞争，以拓展在高端市场的份额。

门级数竞争也亦是 FPGA 厂商第一阶段的竞争主线。通过 LUT 输入数量、簇结构、互联形式等的架构改善，辅之以摩尔定律的推动，**FPGA 的密度和速度得以飞速提升**。终于，在 90 年代末，赛灵思和 Altera 均实现了百万门级的跨越，FPGA 开始加速替代门阵列、标准单元和 ASIC。此时，FPGA 的门级数已经可以比肩门阵列等竞品，没有必要再将逻辑资源数转化为门级数了。

同时，随着 FPGA 集成度的提升，不断将 RAM、DSP、CPU 等功能嵌入到 FPGA 中，以及 LUT4 逐渐提升到 LUT6、LUT8 甚至更高，将 FPGA 的容量转化为门级规模数越来越困难。因此，在 2000 年后，国际上越来越多使用“逻辑单元数”作为基本容量指标，因其能更好代表 FPGA 可调用的资源数，赛灵思从 2005 年之后不再提供门级数规模，而是改用逻辑单元数这一指标。

以赛灵思为例，其逻辑单元数以“1 个 LUT4+1 个寄存器”为基准，是因为最初的 FPGA 中一个逻辑单元确实仅包含 1 个 LUT4、1 个寄存器（以及数个 MUX），所以逻辑单元数等于其 LUT 的数量。但随着 LUT6 的引入、进位器的添加以及 MUX 数量的增长，现在的一个逻辑单元能实现以往多个 LUT4+寄存器实现的功能。因此，现在逻辑单元数这一指标往往是将内部逻辑资源等效为“LUT4 \*1 +寄存器\*1”的个数，这一倍数的具体值由各个公司决定。以赛灵思为例，其采用了 LUT6 的 7 系产品，“逻辑单元数”为内部 LUT6 数量的 1.6 倍，由于在 7 系架构中，一个 LUT6 连接 2 个寄存器，所以寄存器数量是逻辑单元数的  $2/1.6=1.25$  倍。

以 BRAM、DSP、收发器等为代表的固化单元性能是 FPGA 性能体系的第二大部分。除了可编程的逻辑单元外，现代的 FPGA 还集成了许多固化单元，我们常说的 FPGA 的 SerDes 速率、DSP 工作频率等，都是在谈论 FPGA 中不同的固化单元的性能。

集成度竞争是 FPGA 厂商第二阶段的竞争主线 (2000-2010)。将板上分立的 DSP 等器件纳入到 FPGA，背后是减少电路面积、降低功耗的需求。90 年代中期，FPGA 厂商发现用户在使用 FPGA 时，会频繁将 LUT 作为存储使用（即“软”实现），占用了许多逻辑单元，导致 FPGA 容量出现不够的情况。因此，RAM 是第一个被固化到 FPGA 中的单元，即“硬核”化。将这些用户频繁使用到的功能固化到 FPGA 中，可以极大地提升计算效率，用户也不需要为浪费宝贵的逻辑资源而烦恼。例如，将 DSP 嵌入到 FPGA 中（而不是通过万能的 LUT 实现），可以节省 80% 的功耗和 DSP 在板上占用的面积。因此，在 90 年代末完成门级数的超越后，FPGA 厂商的竞争主线从门级数转向集成度竞争，先后将 RAM、DSP、收发器、DDR 接口、CPU、GPU 等许多功能嵌入到 FPGA 中，这是现代的 FPGA 中往往包含了许多固化单元的原因。因此，从 FPGA 的性能评价指标上，也往往涉及到这些固化单元。

尽管如此，一块“好”的 FPGA 并不一定是能力上的最优，而是最贴近使用者的需求，做到在多个指标上的最优，例如功耗、固化功能、成本等。这是因为 FPGA 使用者购买的是整个芯片，如果集成了太多不需要的功能，就相当于提高了使用成本。因此，FPGA 厂商纷纷根据各个下游市场/应用场景做细分，推出了对应高中低端的产品。以龙头赛灵思为例，其拥有高端的 Virtex，性价比的 Kintex，低容量的 Spartan，超低功耗

的 CoolRunner，再加上温度、速度等级等的区别，仅 7 系产品就有高达 1000+ 的料号，产品矩阵非常完备。

**FPGA 的温度等级的考虑。**温度过低或者过高的工作环境，往往会使得 FPGA 时序达不到设计要求。如果器件在  $<0^{\circ}\text{C}$  或者  $>50^{\circ}\text{C}$  的环境下工作，就要选择更高温度等级的器件。一般来说，商业级/通用 FPGA 可以工作在  $0^{\circ}\text{C}$ ~ $85^{\circ}\text{C}$  范围内，而工业级 (I) 需要在  $-40^{\circ}\text{C}$ ~ $100^{\circ}\text{C}$ ，军温级 (Q) 可以在  $-40^{\circ}\text{C}$ ~ $125^{\circ}\text{C}$  工作。

图15：赛灵思和 Altera 的产品矩阵，高中低端市场覆盖完整

资料来源：赛灵思，Altera，Intel，东兴证券研究所绘制

对于高端市场，其需求是最高的性能，单片价格也非常昂贵。高端的 FPGA 需求来自于无线通信，例如 5G 通信的基带侧和核心网侧，还有人工智能的算法训练、半导体原型芯片的仿真、航天器主系统、通信的测试测量仪器、医疗成像仪器，这些场景通常数据处理量大，或者需要同时做到极低的时延和高算力，或者需要非常强的抗辐射能力。目前，高端 FPGA 制程基本在 20nm 及以下，逻辑单元数大于 700k，基本在 1kk 以上的水平，不仅 DSP 和 BRAM 的数量惊人，收发器速率基本在 50GB/s 以上，同时还集成了 CPU 等的处理单元和 PCIe 5 等的先进接口，即基本以 SoC 的形式出现。目前，全球高端的 FPGA 基本由赛灵思或者 Altera 提供，代表产品有：赛灵思 7nm 的 ACAP Versal，16nm 的 Virtex Ultrascale+，Altera 10nm (Intel 7) 的 Stratix 10 和 Agilex，他们通常非常昂贵，典型的单片价格在 5 千美元到 1 万美元之间，体现了当代 FPGA 性能、密度以及集成度的最高水平。高端市场是 FPGA 厂商最重要的收入来源，以 Altera 为例，其高端 FPGA 产品 Stratix 系列的收入占比高达 55%。

中端市场追求的是性价比，需要做到性能和成本的平衡。需求来自于无线通信的空口侧、工业、安防、国防场景，这些下游场景通常需要的逻辑单元数在 100k 以上，但不超过 500k，收发器速率在 25Gb/s 左右，典型制程是 28nm，是 FPGA 行业的中坚力量。中端市场不追求最高的性能，性能和功耗同等重要。典型的中高端产品包括赛灵思的 Kintex，以及 SoC 的 FPGA Zynq，Altera 的 Arria，Lattice 最新推出的 Avant，中低端市场包括赛灵思在中低端过渡的 Artix，以及 Lattice 的 Certus。一般收入占比在 25% 左右。单价一般在数十至数百美元，不超过 5000 美元。

低容量市场对性能要求较低，但需要极低的成本和功耗。低容量 FPGA 的场景常见于消费电子，部分汽车和工业 IoT 的场景，最典型的应用在视频设备的桥接，包括 MIPI、DPI、CMOS 相机、屏显等的接口，如今 VR、AR 设备也会使用到。因为低容量 FPGA 一般是作为灵活接口或者预留使用的，所以不需要高密度，一般 5k-10k 左右的容量即可满足，也基本不需要收发器、处理器等复杂功能。尽管如此，由于低容量的大部分场景应用在移动设备上，对低容量对成本和功耗要求非常高，功耗一般在 5mW-150mW 级别，单价不超过 \$20/片，典型的价格为 \$2.5/片左右。

表4：FPGA 高中低端市场的需求来源，各市场定位性能指标典型值、下游需求及龙头产品组合

| 指标     |                 | 高端                                        | 性价比（中端~中高端）                          | 低容量                             |

|--------|-----------------|-------------------------------------------|--------------------------------------|---------------------------------|

| 典型需求   |                 | 最高的性能、高密度、高集成度                            | 性能和功耗/成本的平衡                          | 需要极低的成本和功耗                      |

| 典型制程   |                 | 7nm、10nm、14/16nm、20nm                     | 28nm                                 | ≥28nm (40nm、56nm)               |

| 逻辑资源   | 逻辑单元数 (LCs/LEs) | >700k, 典型 1K+, 最高 7352k                   | 100k - 500k                          | <100k, 典型 10k                   |

| 固化单元   | Block RAM 容量    | 36Mb - 95Mb, 最高 174Mb                     | 4Mb - 60Mb                           | 0.2 Mb - 4.3Mb                  |

|        | DSP 数量          | 1,000 - 6,000, 最高 14,352                  | 1,080 - 3,528                        | 80                              |

|        | 峰值 INT8 TOPs    | 4-28, 最高 363 TOPs                         | 不考虑                                  | 不考虑                             |

|        | 收发器速率           | 58Gb/s, 最高 116Gb/s PAM4                   | 12.5Gb/s - 32.75Gb/s                 | 无收发器                            |

|        | 收发器个数           | 48-140 个 58G/s 收发器，<br>最高 70 个 112G/s 收发器 | 8/16/32                              | 不考虑                             |

|        | 处理器             | 嵌入 CPU、GPU、AI 等单元                         | 可能有 CPU                              | 无处理器                            |

|        | PCIe 接口         | 4 个 Gen4 x4, 最高 8 个 Gen5 x4               | 4 个 Gen3 x16                         | 1 个 Gen2 x1                     |

| I/O    | I/O 数量          | 500 - 1000                                | 150 - 400                            | 100 - 400                       |

| 目标下游市场 |                 | 无线通信、半导体仿真、<br>测试测量、数据中心、AI、<br>国防航空航天、医疗 | 无线通信（空口侧）<br>国防、汽车、工业、<br>安防、广播、数据中心 | 消费电子、<br>部分汽车、工业、安防<br>的桥接/预留功能 |

| 典型单价   |                 | \$5000 - \$10,000                         | \$700 - \$5000                       | \$2.5, < \$20                   |

| 销售额占比  |                 | 55%                                       | 25%                                  | 20%                             |

| 产品组合   | Xilinx          | Versal、Virtex                             | Zynq、Kintex、Artix                    | Spartan                         |

|        | Altera (Intel)  | Agilex、Stratix                            | Arria                                | Cyclone                         |

|        | Lattice         | 无                                         | Avant、Certus                         | ECP、Mach、<br>CrossLink、iCE      |

注：Versal 并不是传统 FPGA，而是包含 FPGA 的异构计算平台；Zynq 是赛灵思 SoC 级别的 FPGA，嵌入了 CPU 或者基带；高端分类中的最高数值引用了赛灵思 Versal 系列，或者 Intel 的 Agilex 系列的性能参数最高值；Artix 是赛灵思定位在 Spartan 和 Kintex 之间的过渡产品，因此有时也会与 Cyclone 和 Certus 作为竞品比较；销售额占比我们引用了 Altera 被收购前在 2013 年披露的数据。

资料来源：赛灵思，Altera，Lattice，东兴证券研究所整理

**FPGA 的总功耗由静态功耗、动态功耗、IO 功耗和收发器构成**，静态功耗是电路的功耗，主要是由晶体管漏电造成；动态功耗指芯片处于工作状态时电路翻转产生的功耗，来源于时钟、逻辑、BRAM、处理单元、收发器等单元。芯片功耗越低，设备的耗电就越少，散热要求越低（或不需要额外的散热改造），整体尺寸亦愈能小型化。一般来说，嵌入式处理非常看重功耗，功耗预算不超过 50W。FPGA

公司通过两种方式降低功耗：1) 硬件上，使用更先进的制程和工艺、3D-IC 技术、嵌入更多的固化单元、更低功耗的架构；2) 软件上，优化布局算法，以减少跨时钟域和多余的逻辑资源的占用，以及提供功耗估计工具方便用户修改。

因此，不少厂商在功耗上另辟蹊径，以建立在低容量市场的竞争优势，从而摆脱低容量市场单纯依靠量大低成本的竞争方式，以及一贯以来的价格战问题。低容量市场技术成熟，进入壁垒相对较低，厂商之间提供的产品差异不大，往往容易出现价格战的问题。但由于“性能-功耗-便携性”的矛盾一直存在，低容量市场对低功耗的追求同样在不断增长。因此，优化功耗的能力是低容量市场厂商除了价格之外的竞争法宝。例如，目前全球出货量最高的FPGA厂商Lattice，其Certus系列就使用了FD-SOI工艺，比起基于CMOS的竞品，例如Altera的Cyclone、赛灵思的Artix，其功耗要低70%-75%。因此，尽管Lattice在FPGA全球市占率仅为5%，没有大容量FPGA产品线，但凭借在功耗上的优势，在低容量市场优势明显，整体毛利率同样能达到50%以上。

图16: FPGA的功耗拆分, 从硬件上降功耗最为有效

资料来源：赛灵思，东兴证券研究所绘制

除了 FPGA 之外，许多 FPGA 厂商还同时提供 CPLD 产品，主要瞄准极低功耗的场景。90 年代中后期，低密度的 FPGA 对 CPLD 的替代，使得 CPLD 在 2000 年开始市场增长缓慢。尽管如此，CPLD 在一些需要极低功耗的低容量场景仍有非常强的竞争力：低容量 FPGA 功耗一般在 mW 级别，CPLD 可以进一步下探到  $\mu$ W 级别。例如，赛灵思的 CPLD CoolRunner 功耗仅有  $28.8\mu\text{W}$ ，远低于其 Arkitx7 50K 近  $600\text{mW}$  的总功耗。

图17: Lattice 的 FPGA CrossLink 嵌入了性能优异的 MIPI 硬核, 在安防行业特别受欢迎

图18: Lattice 在低功耗上的优势明显, 在低容量做到功耗比竞品低 70%-75%

资料来源：Lattice, 东兴证券研究所

资料来源：Lattice, 东兴证券研究所

此外，对于航天设备，**FPGA** 抗辐射能力是非常重要的性能指标。离地越远，辐射越大，要求器件具备的抗辐射能力越高。不同于地面，外太空的航天器没有地球大气层的保护，其接受的辐射量是地面的百倍甚至千倍以上。太空中的辐射来源于太阳活动、宇宙射线和地球磁场的辐射捕获带 (Van Allen Belt)，主要有质子、重离子等，这些重粒子通常能量大到足以击穿原子，产生的电子空穴对会造成电子器件的存储单元发生翻转，严重的可致器件损坏，导致在轨任务的失败，这对于造价百万甚至在千万美元的航天器来说是不可接受的。同时，由于重粒子无法被遮挡，航天器需要具备电路级的抗辐射能力。在卡门线以上 (海拔高度 100km) 运行的电子系统需要使用宇航级的 **FPGA**。其中，在 LEO 高度通常运行着大部分的商业通信卫星 (比如 Starlink)、观测卫星以及空间站 (比如天宫 1 号和国际空间站)，其辐射来源主要为质子，辐射量 (以 LET 衡量) 平均在  $40 \text{ MeV-cm}^2 / \text{mg}$ ，使用耐辐射 (Radiation Tolerant) **FPGA** 即可。而进入 MEO 或者 GEO 高度，在轨的通常为导航和气象卫星，更远的还有执行探月活动、火星任务的航天器，辐射主要为能量更高的重离子，辐射量平均在  $92 \text{ MeV-cm}^2 / \text{mg}$ ，需要使用辐射加固 (Radiation Hardened) **FPGA**。**FPGA** 的抗辐射能力和航行高度挂钩，越抗辐射，就越能确保航天器顺利运行在 MEO 以上，执行登月、火星、甚至星际航行任务。

图19：外太空环境需要使用宇航级 **FPGA**，其抗辐射能力和航行高度直接挂钩

资料来源：赛灵思，FAI，NASA，东兴证券研究所绘制

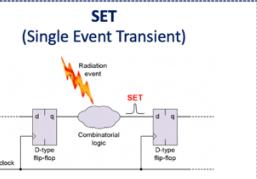

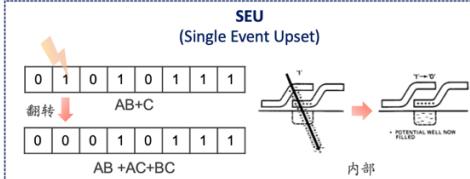

太空中的辐射对电子器件的影响主要是单粒子效应 (SEE) 和总剂量效应 (TID)。单粒子效应 (SEE, Single Event Effects) 是宇宙射线击中航天器内部电子器件时造成的一次性损坏。其中, SEU 是最频繁出现的事件, 即存储单元中单个 bit 发生翻转, 可能导致严重的后果。例如, 处于着陆阶段的飞行器, 在关键逻辑块上的翻转, 会改变该逻辑块所表述的电路功能, 可能使本来应该开启的反推被关闭, 导致着陆失败。而 SEFI 是指发生在关键控制逻辑上的 SEU, 往往导致系统发生全面故障。MBU 即发生在多个 bit 上的翻转。尽管如此, 这些都是“软”错误, 可以通过冗余设计和频繁的动态刷新很好地规避。而有些 SEE 是破坏性的, 例如, SEB 的发生意味着电子器件被射线击穿, 即“烧坏”; SEL 即 CMOS 发生开路, 电路发生电流过载, 往往导致器件损坏。破坏性的 SEE 一旦发生是不可修复的, 所以工程师会确保航天器中的电子器件具有相应的抗辐射能力。除了单次高能粒子撞击造成的 SEE 外, 太空辐射对电子器件的损伤还包括总剂量效应 (TID, Total Ionizing Dose), 累积的辐射量会使得电子器件的性能退化, 超过一定的辐照剂量阈值后 (比如 $>100$  krad), 电路就会发生错误。

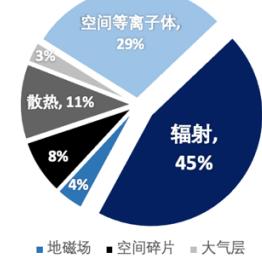

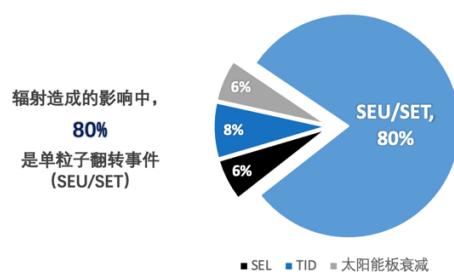

宇宙射线造成的单粒子效应是航天器故障的主因。根据 TIMA 实验室和法国国家太空研究中心统计，全球 20 年间 100 多次在轨航天器的故障事件中，辐射是第一诱因，45%的故障来源于太空辐射。而辐射造成的影响中，80%为单粒子事件（例如 SEU/SET），6%为 SEL，8%为 TID。SEU 是在太空中最频繁发生的故障。

图20：宇宙射线导致的单粒子效应是航天器发生故障的最重要原因

## 单粒子效应 (Single Event Effects) 是航天器故障主因

航天器故障中，

45%

由太空辐射引起

发生原因：宇宙射线击中电子器件，有的会造成可修复的短暂故障，严重的可导致器件损坏

➤ 非破坏性：SEU、MBU、SET、SEFI

➤ 破坏性：SEB、SEGR、SEL、SEDR

资料来源：赛灵思，CNES，Cypress，Electronic Engineering，Microelectronics Reliability，NASA，TI，TIMA Laboratory，东兴证券研究所绘制

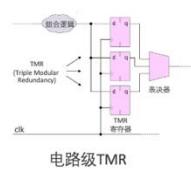

因此，FPGA 的抗辐射能力主要考虑对总剂量效应和单粒子事件的防护能力，具体指标有 TID 耐性、SEL 阈值、SEFI 发生率和 SEU 发生率。一般来说，耐辐射器件适合运行在 LEO 高度，其 TID 指标通常要大于 100 krad，SEL 阈值在 50 MeV·cm<sup>2</sup> /mg 以上。而辐射加固的器件 TID 指标一般大于 700 Krad，SEL 阈值需要在以上 100 MeV·cm<sup>2</sup> /mg，才能胜任在 MEO 高度及以上的在轨任务。SEFI 发生率 2.76E-7，相当于每 1 万年不到 1 次的发生率，可以认为是 SEFI 免疫的。

目前，全球有能力提供宇航级 FPGA 公司屈指可数。宇航级 FPGA 需要额外使用许多技术，比如 TMR 的使用使得芯片面积大幅增加、测试上需要租用昂贵的重离子加速器设备等，制造的成本高，做到辐射加固更是需要从设计到制造封测的一系列流程改变。因此，宇航级 FPGA 价格非常昂贵。尽管如此，对于 GEO 轨道、月球和火星等的战略探索任务，使用辐射加固的电子器件是必须的。目前，全球有能力提供辐射加固 FPGA 的公司主要为赛灵思和 Microchip (包括其收购的 Actel 和 Atmel)，均与美国国防部、NASA 等机构部门有着数十年的紧密合作。其中，赛灵思唯一的辐射加固 FPGA 是其 65nm 的 Virtex 5QV 产品，其 TID 剂量阈值达到 1 Mrad，SEL 阈值在 125 MeV·cm<sup>2</sup>/mg 以上。Virtex 5QV 用于火星漫步车“好奇号”上执行视觉加速计算任务。其余耐辐射 FPGA 包括 Virtex II QV、Virtex 4 QV、RT Kintex UltraScale 以及最新的 7nm 抗辐射产品 Versal XQRV。除了低轨卫星，Virtex II 还广泛运用在好奇号、毅力号等火星漫步车上，执行着陆器控制和视觉分析的任务。

图21：离地球越远，FPGA 的抗辐射能力要求越高，使用到的辐射加固技术就越多

离地越远 → 要使用到越多的辐射加固技术 → 制造成本越大、价格越昂贵

全球提供辐射加固FPGA的公司：

- Xilinx

- Microchip (Actel & Atmel)

Virtex 5 QV (RHB)

板级TMR

如何做到辐射加固？

- 制造上：抗辐射工艺，比如SOI、SOS、SOD

- 电路设计：三模冗余设计（TMR）；主次路径

- 板级设计：板级冗余，spaceVPX

- 软件上：回读校验+动态刷新

- 封装：陶瓷封装等可靠性高的封装

- 测试：长时间的真空环境测试抗辐射能力，需要重离子加速器

赛灵思现有宇航级FPGA产品：

耐辐射级 (Radiation-tolerant)

- Versal XQR (7nm)

- RT Kintex UltraScale (20nm)

- Virtex 4 QV (90nm)

- Virtex II QPro (0.15 μm)

辐射加固级 (Radiation-hardened)

- Virtex 5QV (65nm)

赛灵思宇航级FPGA抗辐射能力

| Xilinx XQR     | 推出时间 | LC                   | TID                               | SEL                           | SEFI            | SEU <sub>cfg</sub> |

|----------------|------|----------------------|-----------------------------------|-------------------------------|-----------------|--------------------|

| 宇航级FPGA        |      | 逻辑单元数                | 辐射总剂量阈值                           | SEL阈值                         | 翻转发生次数 (次/器件/日) |                    |

| Virtex II QPro | 2003 | 10k, 28k, 67k        | 200 Krad(Si)                      | > 160 MeV-cm <sup>2</sup> /mg | 1.5E-6          | -                  |

| Virtex-4QV     | 2008 | 55k, 56k, 142k, 200k | 300 Krad(Si)                      | > 125 MeV-cm <sup>2</sup> /mg | 1.5E-6          | -                  |

| Virtex-5QV     | 2010 | 131k                 | 1 Mrad(Si)                        | > 125 MeV-cm <sup>2</sup> /mg | 2.76E-7         | 3.8E-10            |

| RT Kintex U    | 2020 | 726k                 | 100 Krad(Si)                      | > 80 MeV-cm <sup>2</sup> /mg  | 4.5E-4          | 9.5E-9             |

| Versal XQR     | 2021 | 1,968k               | 耐辐射级FPGA, 预计2023年一季度出货, 因此具体数据未披露 |                               |                 |                    |

资料来源：赛灵思，BYU, Electronic Engineering, 东兴证券研究所绘制

过去，星载 FPGA 处理能力落后于商业级 10-15 年，现在已经和商业级接近，背后是不断增长的提升卫星处理能力的需求。过去，卫星习惯于使用抗辐射的 Virtex II 和 Virtex 4，虽然抗辐射性能达标，但其处理能力基本落后于商业级产品 10-15 年。比如，03 年推出的 Virtex II QPro 依然广泛使用在目前的在轨卫星中；而美国在 2020 年发射的毅力号火星漫游车，其搭载的科学仪器同样大量使用了耐辐射级 Virtex II，以及 08 年推出的 Virtex 4QV。从推出时间看，商业级的 Virtex 5 在 2006 年推出，而辐射加固的 Virtex 5QV 是 2010 年推出的，中间间隔 4 年，而且 2010 年最先进的产品是 Virtex 7，中间间隔两代；耐辐射的 RT Kintex UltraScale 是 2020 年推出的，而其商业级早在 2013 年就推出了，中间间隔 7 年。然而，近两年来我们看到赛灵思加快了宇航级 FPGA 的推出。目前，赛灵思最先进的产品是 19 年推出的 ACAP Versal (7nm)，而去年初就推出了宇航级的 Versal XQR，做到了和商业级同代际。Versal XQR 针对低轨卫星的 AI 应用，主要目的包括获取更清晰的卫星观测图像、快速识别云层和地面目标，不仅逻辑单元数大幅增加，还嵌入了 AI 处理单元、高速的收发器等，使得很多数据不需要回传地面就能在卫星上进行分析，不仅节省了宝贵的星地通信带宽，还大幅提高了低轨卫星的处理能力和反应时间。

## 5. 设计“好”的 FPGA，难点在哪里？

FPGA 的设计难点在于以下几个方面：

一是产品定义上，必须平衡市场上各个需求，难度在于如何平衡可编程功能和固化功能。在 FPGA 中嵌入固化单元，往往比使用 LUT、寄存器等万能资源来说，拥有更低的功耗和面积。例如，固化了 AD/DA 和 ARM 核的 RFSoC FPGA，就比使用分立的“ARM+AD/DA+FPGA”的方案，面积要减少 50%、功耗降低 30%-40%、

成本降低 40%-60%。尽管如此，要嵌入哪些固化单元需要设计者权衡，因为 FPGA 的开发者购买的是整个芯片，他们仍有可能为自己不需要或者不使用的功能付费；另一方面，如果 FPGA 的固化功能太少，其在市场上的竞争力就大为降低，因为客户不得不使用太多的宝贵的可编程逻辑资源，去实现本来应该固化的功能，功耗和时延均大幅增加。这都需要 FPGA 公司有非常好的客户的沟通。

**Altera 历史上在 Excalibur 的失败，说明了产品定义和需求匹配的重要性。**在 FPGA 上嵌入处理器硬核，早在 2000 年就有过尝试。在  $0.18/0.15\mu\text{m}$  节点中，Altera 为了和赛灵思在性能上竞争，将 ARM9 嵌入到了其最新的 SOPC FPGA Excalibur 中，成为业内首个将处理器嵌入到 FPGA 的厂商。然而，刚刚经历科网泡沫的客户将功耗提升到了和性能同等重要的位置，不愿意为过高性能的 FPGA 付费，对 FPGA 需求仍然在灵活性上，使得 Altera 在  $0.18/0.15\mu\text{m}$  的 FPGA 市场份额陡降至 20%，而此前赛灵思和 Altera 一直都维持在 6-4 分成的局面。Altera 之后吸取了教训，在嵌入固化单元时进行了非常小心的考虑，不再一味强调产品的性能，而是强调了解客户需求，并在随后的  $0.13\mu\text{m}/90\text{nm}$  节点推出了针对高端市场的 Stratix 和中低容量的 Cyclone，在 90nm 市占率反超赛灵思。

图22：Altera 曾经因为 Excalibur 丢失了大部分市场份额

资料来源：Xilinx, Altera, 东兴证券研究所绘制

二是从技术上，体现在必须跟上最新的制程，制程领先是 FPGA 市场份额最直接的决定因素。FPGA 的通用性使其走线和面积比起 ASIC 来说不是最优。因此，FPGA 必须在制程上做到领先 ASIC 或者 ASSP 数代，以带来更有竞争力的性能表现，这使得 FPGA 对制程的追逐是必然的选择。此外，FPGA 从新品发布到量产阶段中间存在客户导入环节，在这期间客户评估不同厂商新推出的 FPGA，最后确定一家在后续量产的产品中使用，并在上面完成自己的电路设计，即一个 **Design-win**，这一过程通常需要 9-12 个月。由于开发环境、产品架构等各不相同，一旦确定了之后，用户转移到另一家 FPGA 是非常困难和费时的。这种高绑定的特点，造就了 FPGA 非常强的壁垒，使得最先推出的玩家往往能赢得大部分市场份额。一般来说，在最新制程的 design-wins 能预测 2-3 年后在 FPGA 市场的份额。FPGA 龙头赛灵思历史上是制程领导者，市场份额从 2000 年后便维持在 50% 的水平，除了 Altera 能跟上赛灵思的节奏，行业其他玩家均落后龙头 2-3 个代际。

**从 Altera 在 40nm 的赶超可以看出制程领先对 FPGA 的重要性。**2008 年，由于联电在 40nm 节点出现交付问题，使得长期和联电合作的赛灵思 40nm 新品推出受阻，而长期与台积电合作的 Altera 则首先推出 40nm，并在历史上首次成为制程领导者。在 2 年后的 2010 年，Altera 凭借在 40nm 的优势，市场份额从 36% 跃升至 40%，而赛灵思的市场份额则多年来首次下降到 50% 以下。此前的格

局是赛灵思大概 50% 的份额，Altera 在 30% 的份额，此次领先使得 Altera 从 08 年的 36% 逐年跃升至 11 年的 42%，整体市场份额提升大概 6 个点。赛灵思随后将主晶圆厂切换至台积电，并首先推出 28nm 产品，在 12 年夺回了被 Altera 吃掉的份额。

图23：FPGA 在最新制程的推出速度，基本可以预测 2 年后的市场份额

资料来源：赛灵思，Altera，Intel，ElectronicsWeekly，Dataquest，iSuppli，东兴证券研究所绘制

**FPGA 技术上的第二个难点在于架构创新。** FPGA 设计不是简单地堆叠逻辑单元，制程对性能的帮助亦是有限的，如何排布逻辑单元和各固化单元，来平衡性能提升和面积、时延、功耗之间的矛盾，是非常重要的问题，而架构是 FPGA 厂商对这个问题给出的答案。FPGA 厂商必须不断推出新架构实现的技术，并以专利的形式固定下来，以适应下游不断增长的性能、功耗和成本的需求。FPGA 的架构设计需要考虑 LUT 的大小、BLE 的大小、逻辑块大小、互联结构等许多因素。好的架构，更容易充分地利用逻辑资源，功耗和时延通常也更低。FPGA 巨头赛灵思和 Altera 通常与学界紧密合作，诸如多伦多大学等科研院所为 FPGA 的架构演进和算法迭代做了非常重要的贡献。

三是 FPGA 硬件和设计工具绑定的特点，使得 EDA 和硬件必须做到并重开发。FPGA 的 EDA 有两个方面

图24：FPGA 的架构设计需要考虑非常多的的因素，赛灵思等巨头与学界紧密合作

资料来源：多伦多大学, *FPGA 2000*, 东兴证券研究所绘制

的竞争因素考量：1) 软件的易用性；2) 核心的“映射-包装-布局布线”算法。前者可以稍落后于硬件，而后者是和硬件的架构高度绑定的，必须与硬件同时发展。我们在前文提过，虽然仿真等工作可以由第三方 EDA 完成，但由于架构不公开，并不存在通用的 FPGA 布局布线工具，布局布线只能由 FPGA 厂商自己的 EDA 软件完成。因此，FPGA 的容量每上一个台阶，就必须更新配套的“映射-包装-布局布线”三大算法。历史上

**图25：FPGA 和软件绑定的特点，使得 EDA 和硬件同等重要**

资料来源：赛灵思，Altera，Lattice，东兴证券研究所绘制

有过通用的 FPGA 全流程 EDA 开发尝试，但都无一例外失败了。对于客户来说，切换 FPGA 厂商不仅仅是适应新的开发环境所花费的时间和经历，其设计在 FPGA 上实现的效率亦各不相同。而且开发软件是以免费或者非常低的价格提供给购买了 FPGA 的用户的，软件本身不产生收入。这种硬件和软件高绑定的特点，使得 FPGA 新进厂商在攻克了硬件的诸多技术难点外，还要完成配套软件的开发，这是 FPGA 的设计难于其它类型芯片的原因，亦是 **FPGA 的进入壁垒如此之高的原因之一**。历史上赛灵思和 Altera 都曾与第三方的 EDA，比如 Synopsys、Mentor 合作优化仿真以及综合的流程，但布局布线从来只在自己的 EDA 上进行。

软硬件并重的特点，使得 **FPGA 呈现“重”研发的特点**。FPGA 软硬件绑定的特点，使得 FPGA 厂商除了芯片设计外，还需要额外投入软件研发的费用。例如，1992 年，处于迅速发展时期的赛灵思，每年的研发大约有 50% 投入到硬件，50% 投入到 EDA 中；即使在市场地位后稳固的 2001 年，每年也有 40% 的研发投入在软件。在 2000 年后，随着 FPGA 的容量和复杂度大幅增加，FPGA 厂商的研发费率均大幅提升，全球 FPGA 前三赛灵思、Altera 和 Lattice 的研发费率均常年保持在 20% 的水平，远高于芯片设计公司的平均 10% 水平。

图26：全球前三 FPGA 公司的研发费率常年保持 20%以上

资料来源：赛灵思，Altera，Lattice，东兴证券研究所绘制

此外，如今 **FPGA 厂商不止提供传统的 FPGA 芯片，还提供许多板级的方案，以减少使用者的开发难度，培养用户黏性**。传统的 FPGA 销售方式是“FPGA 芯片+赠送免费的 EDA 工具”。现在，FPGA 厂商更多地销售相应的板级应用方案，目的是为了减少使用者的开发难度，培养用户黏性。

图27：除了 FPGA 和配套的 EDA，如今的 FPGA 厂商还提供了板级的解决方案，以实现客户快速开发的目的

资料来源：赛灵思，东兴证券研究所

## 风险提示

下游需求不及预期，中美贸易战超预期。

## 分析师简介

### 分析师：李美贤

中国人民大学硕士，2019年7月加入东兴证券研究所，从事通信及电子研究，关注新兴科技领域，重点覆盖AI、云计算、工业互联网等产业链。

## 分析师承诺

负责本研究报告全部或部分内容的每一位证券分析师，在此申明，本报告的观点、逻辑和论据均为分析师本人研究成果，引用的相关信息和文字均已注明出处。本报告依据公开的信息来源，力求清晰、准确地反映分析师本人的研究观点。本人薪酬的任何部分过去不曾与、现在不与，未来也将不会与本报告中的具体推荐或观点直接或间接相关。

## 风险提示

本证券研究报告所载的信息、观点、结论等内容仅供投资者决策参考。在任何情况下，本公司证券研究报告均不构成对任何机构和个人的投资建议，市场有风险，投资者在决定投资前，务必要审慎。投资者应自主作出投资决策，自行承担投资风险。

## 免责声明

本研究报告由东兴证券股份有限公司研究所撰写，东兴证券股份有限公司是具有合法证券投资咨询业务资格的机构。本研究报告中所引用信息均来源于公开资料，我公司对这些信息的准确性和完整性不作任何保证，也不保证所包含的信息和建议不会发生任何变更。我们已力求报告内容的客观、公正，但文中的观点、结论和建议仅供参考，报告中的信息或意见并不构成所述证券的买卖出价或征价，投资者据此做出的任何投资决策与本公司和作者无关。

我公司及报告作者在自身所知情的范围内，与本报告所评价或推荐的证券或投资标的不存在法律禁止的利害关系。在法律许可的情况下，我公司及其所属关联机构可能会持有报告中提到的公司所发行的证券头寸并进行交易，也可能为这些公司提供或者争取提供投资银行、财务顾问或者金融产品等相关服务。本报告版权仅为我公司所有，未经书面许可，任何机构和个人不得以任何形式翻版、复制和发布。如引用、刊发，需注明出处为东兴证券研究所，且不得对本报告进行有悖原意的引用、删节和修改。

本研究报告仅供东兴证券股份有限公司客户和经本公司授权刊载机构的客户使用，未经授权私自刊载研究报告的机构以及其阅读和使用者应慎重使用报告、防止被误导，本公司不承担由于非授权机构私自刊发和非授权客户使用该报告所产生的相关风险和责任。

## 行业评级体系

公司投资评级 (A股市场基准为沪深 300 指数，香港市场基准为恒生指数，美国市场基准为标普 500 指数)：

以报告日后的 6 个月内，公司股价相对于同期市场基准指数的表现为标准定义：

强烈推荐：相对强于市场基准指数收益率 15% 以上；

推荐：相对强于市场基准指数收益率 5%~15% 之间；

中性：相对于市场基准指数收益率介于-5%~+5% 之间；

回避：相对弱于市场基准指数收益率 5% 以上。

行业投资评级 (A股市场基准为沪深 300 指数，香港市场基准为恒生指数，美国市场基准为标普 500 指数)：

以报告日后的 6 个月内，行业指数相对于同期市场基准指数的表现为标准定义：

看高：相对强于市场基准指数收益率 5% 以上；

中性：相对于市场基准指数收益率介于-5%~+5% 之间；

看淡：相对弱于市场基准指数收益率 5% 以上。

## 东兴证券研究所

北京

西城区金融大街 5 号新盛大厦 B 座 16 层

邮编：100033

电话：010-66554070

传真：010-66554008

上海

虹口区杨树浦路 248 号瑞丰国际大厦 5 层

邮编：200082

电话：021-25102800

传真：021-25102881

深圳

福田区益田路 6009 号新世界中心 46F

邮编：518038

电话：0755-83239601

传真：0755-23824526