证券研究报告：电子|深度报告

2023年7月21日

## 行业投资评级

强于大市 | 维持

## 行业基本情况

|       |         |

|-------|---------|

| 收盘点位  | 3868.3  |

| 52周最高 | 4444.94 |

| 52周最低 | 3261.49 |

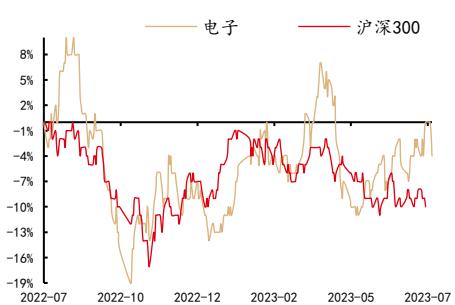

## 行业相对指数表现（相对值）

资料来源：聚源，中邮证券研究所

## 研究所

分析师: 吴文吉

SAC 登记编号: S1340523050004

Email: wuwenji@cnpsec.com

## 近期研究报告

《存力与AI共振》 - 2023.07.11

## 从存力到封力：CoWoS 研究框架

## ● 投资要点

摩尔定律放缓，芯片特征尺寸已接近物理极限，先进封装成为提升芯片性能，延续摩尔定律的重要途径。先进封装是指处于前沿的封装形式和技术，通过优化连接、在同一个封装内集成不同材料、线宽的半导体集成电路和器件等方式，提升集成电路的连接密度和集成度。目前，带有倒装芯片(FC)结构的封装、晶圆级封装(WLP)、系统级封装(SiP)、2.5D 封装、3D 封装等均被认为属于先进封装范畴。

先进封装增速高于整体封装，2.5D/3D 封装增速居先进封装之首。根据 Yole，2021 年，先进封装市场规模约 375 亿美元，占整体封装市场规模的 44%，预计到 2027 年将提升至占比 53%，约 650 亿美元，CAGR<sub>21-27</sub> 为 9.6%，高于整体封装市场规模 CAGR<sub>21-27</sub> 6.3%。先进封装中的 2.5D/3D 封装多应用于(x)PU, ASIC, FPGA, 3D NAND, HBM, CIS 等，受数据中心、高性能计算、自动驾驶等应用的驱动，2.5D/3D 封装市场收入规模 CAGR<sub>21-27</sub> 高达 14%，在先进封装多个细分领域中位列第一。

先进封装处于晶圆制造与封测制程中的交叉区域，涉及 IDM、晶圆代工、封测厂商，市场格局较为集中，前 6 大厂商份额合计超过 80%。全球主要的 6 家厂商，包括 2 家 IDM 厂商(英特尔、三星)，一家代工厂商(台积电)，以及全球排名前三的封测厂商(日月光、Amkor、JCET)，合计处理了超过 80% 的先进封装晶圆。

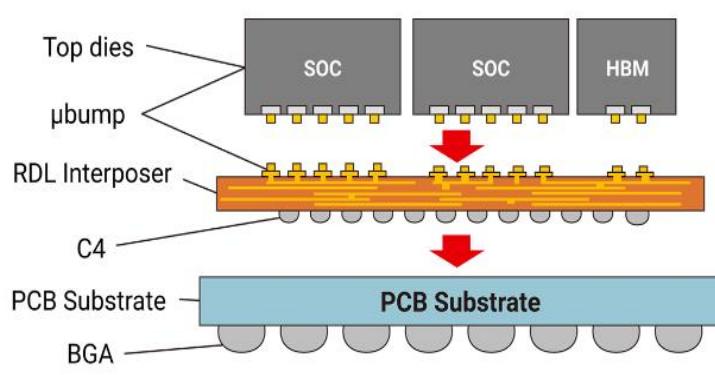

CoWoS (Chip On Wafer On Substrate) 是台积电的一种 2.5D 先进封装技术，由 CoW 和 oS 组合而来，根据不同中介层 (interposer) 分为 CoWoS-S/R/L 三种类型。其中 CoWoS-S 最为经典应用最广，采用硅作为中介层。CoWoS-R 基于 InFO 技术，利用 RDL 中介层互连各 chiplets。CoWoS-L 结合了 CoWoS-S 和 InFO 技术的优点，使用内插器与 LSI (本地硅互连) 芯片进行芯片间互连，同时用于电源和信号传输的 RDL 层提供灵活集成。

超越摩尔 (More than Moore, 下文简称 MtM) 提速，制造设备为关键。采用全新结构的 3D 集成是推动半导体行业发展的重要技术，诸如存储器、逻辑器件、传感器和处理器等不同类型的器件和软件的复杂集成，以及新材料和先进的芯片堆叠技术，都需要基于 3D 集成技术。

晶圆级封装键合技术为实现 3D 集成的有力抓手。3D 集成技术存在晶圆级对准精度、键合完整性、晶圆减薄与均匀性控制以及层间(层间)互连这 4 项挑战，随着摩尔定律逼近材料与器件的物理极限，源于微机电系统 (Micro Electro Mechanical Systems, MEMS) 制造技术的晶圆级封装键合技术逐渐进入集成电路制造领域，成为实现存储器、逻辑器件、射频器件等部件的三维堆叠同质/异质集成，进而提升器件性能和功能，降低系统功耗、尺寸与制造成本的重要技术途径。

其中熔融与混合键合使得芯片在性能上能够实现相当于更低工艺节点性能，同时扫除晶圆键合走向 CMOS 互联工艺的最大障碍。

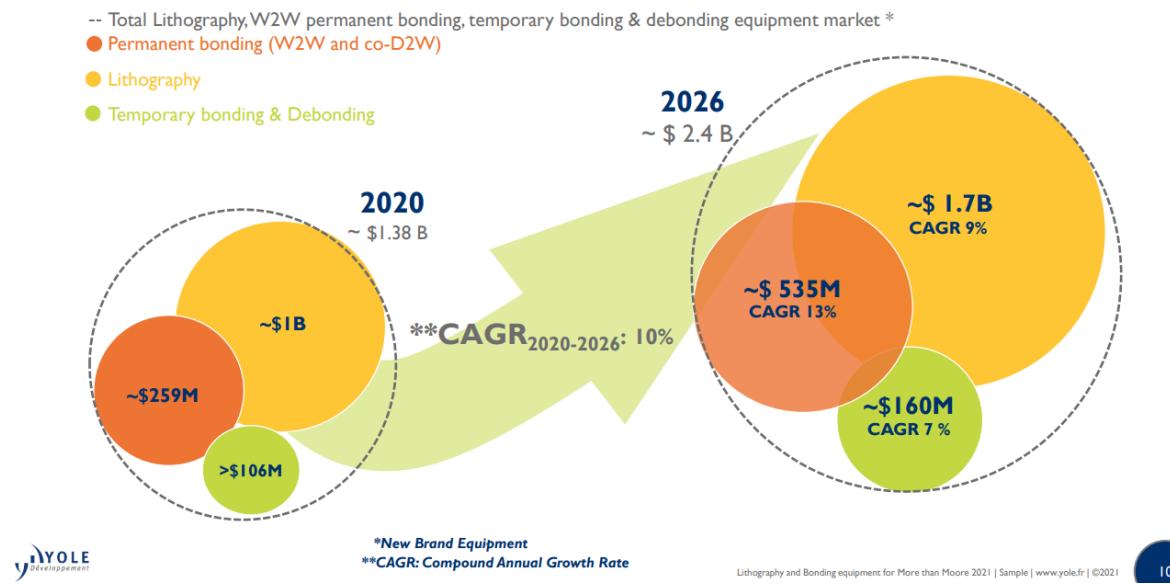

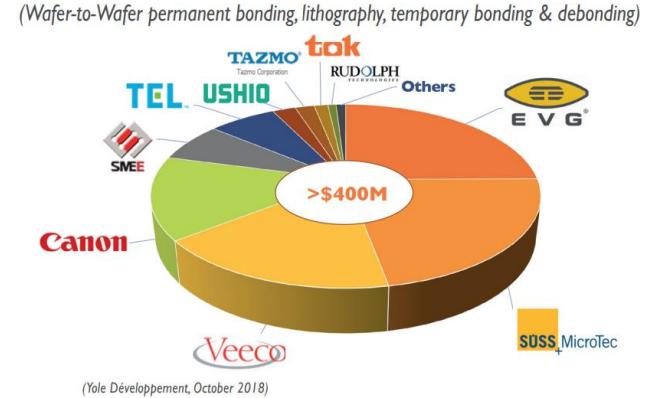

光刻设备是超越摩尔变革的支柱，键合设备则推动先进封装的发展。就设备而言，晶圆级封装键合设备和光刻设备因超越摩尔 (MtM) 提速愈发关键。MtM 市场涵盖 MEMS、CMOS 图像传感器 (CIS)、电源和射频 (RF) 以及先进封装 (AP) 等，MtM 设备包括晶圆对晶圆 (Wafer-to-Wafer, W2W) 永久键合、光刻、临时键合和解键合设备。Yole 测算 2020 年全球这三类 MtM 设备总规模为 13.8 亿美元，预计到 2026 年将超过 24 亿美元，CAGR<sub>2020-2026</sub> 为 10%，主要是由光刻设备驱动，其次为 W2W 永久键合。目前发达国家晶圆键合设备市场已比较成熟，国际一流晶圆键合设备厂商主要包括奥地利 EVG 公司与德国 SUSS MicroTec 公司等，而我国市场仍处成长阶段。随着 3D 集成技术的发展，在企业不断加大资金投入的基础上，晶圆键合系列设备市场将迎来井喷式发展，建议关注拓荆科技（混合键合），芯源微（临时键合和解键合）。

● 风险提示：

下游需求不及预期；行业景气度复苏不及预期；公司技术与产品迭代进展不及预期等。

● 建议关注：

晶圆代工：中芯国际

封装设备：拓荆科技，芯源微

封装材料：华海诚科，联瑞新材，德邦科技

封装：江波龙，深科技，长电科技，通富微电，晶方科技，甬矽电子，华天科技

## 目录

|                                                           |    |

|-----------------------------------------------------------|----|

| 1 后摩尔时代，先进封装成为提升芯片性能重要解法.....                             | 5  |

| 1.1 摩尔定律放缓，先进封装日益成为提升芯片性能重要手段.....                        | 5  |

| 1.2 先进封装份额占比提升，2.5D/3D 封装增速领先先进封装 .....                   | 6  |

| 1.3 先进封装处于晶圆制造与封测的交叉区域 .....                              | 7  |

| 2 CoWoS：台积电的 2.5D 先进封装技术 .....                            | 8  |

| 2.1 CoWoS-S：最经典的 CoWoS 技术，以硅基板作为中介层.....                  | 9  |

| 2.2 CoWoS-R：使用 RDL 替代硅作为中介层 .....                         | 10 |

| 2.3 CoWoS-L：使用小芯片和 RDL 作为中介层，融合 CoWoS-S 和 InFO 技术优点 ..... | 11 |

| 3 超越摩尔 (MtM) 提速，制造设备为关键 .....                             | 12 |

| 3.1 光刻设备是超越摩尔的支柱，键合设备推动先进封装.....                          | 12 |

| 3.2 MtM 设备 (W2W 永久键合、光刻、临时键合和解键合设备) 相关工艺与流程 .....         | 14 |

| 3.3 MtM 设备市场规模 .....                                      | 17 |

| 3.4 MtM 设备厂商 .....                                        | 18 |

## 图表目录

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| 图表 1: 全球封装技术向先进封装迈进 .....                                             | 5  |

| 图表 2: 半导体封装技术演进路线图 .....                                              | 6  |

| 图表 3: 2020–2027 年先进封装市场收入规模预测（单位：十亿美元） .....                          | 7  |

| 图表 4: 先进封装处于晶圆制造与封测制程中的交叉区域 .....                                     | 8  |

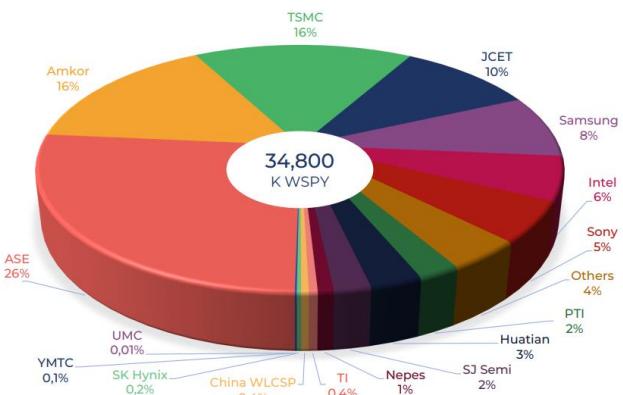

| 图表 5: 2021 年先进封装按晶圆拆分市场份额 (300MM EQ WSPY) .....                       | 8  |

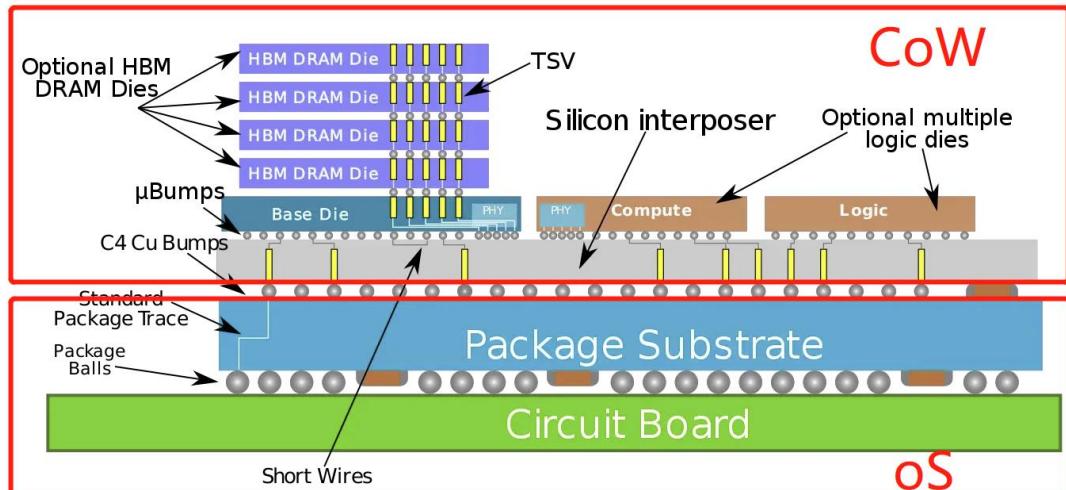

| 图表 6: CoWoS 结构: CoW+oS .....                                          | 8  |

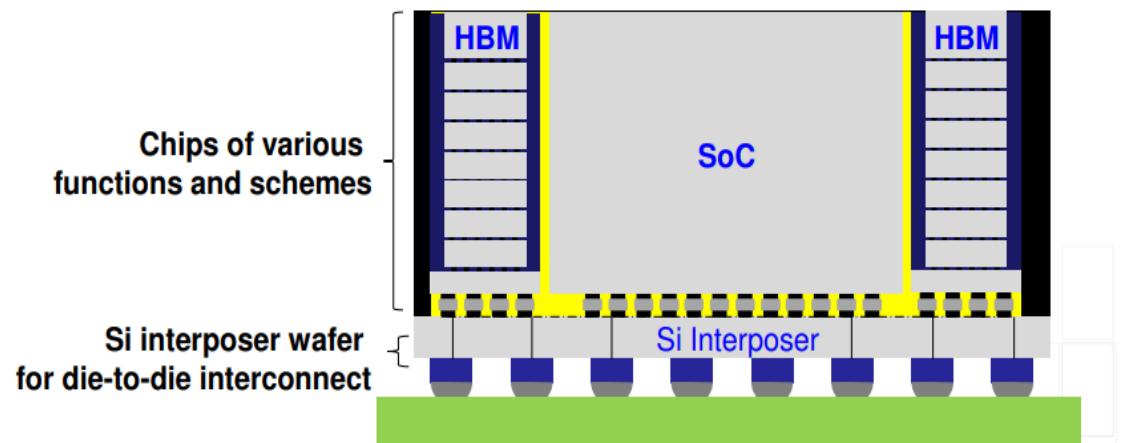

| 图表 7: CoWoS-S 结构 .....                                                | 9  |

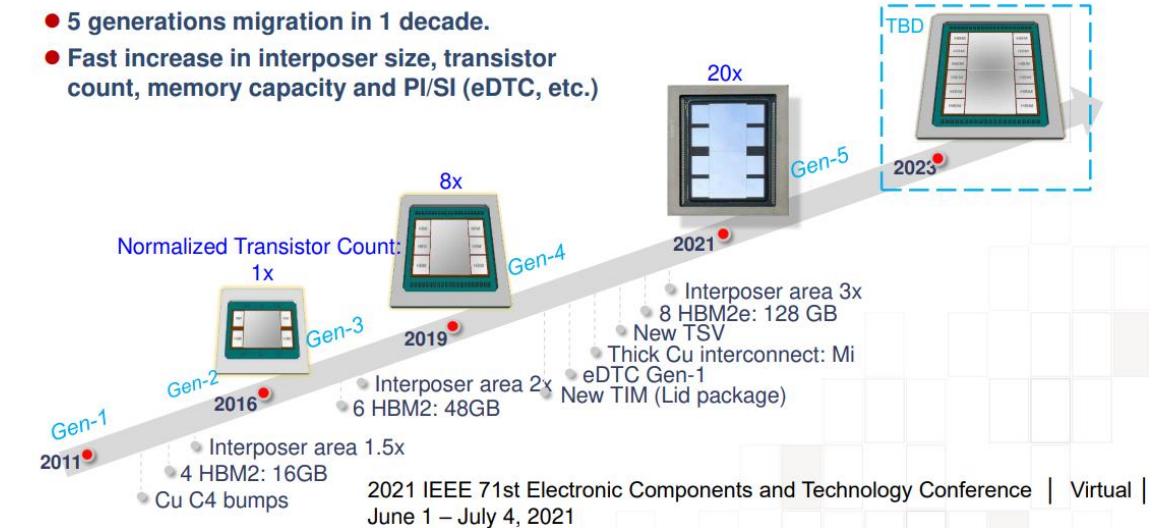

| 图表 8: CoWoS-S 技术演进 .....                                              | 10 |

| 图表 9: CoWoS-R 结构 .....                                                | 10 |

| 图表 10: CoWoS-R 缓冲原理 .....                                             | 10 |

| 图表 11: CoWoS-L 结构 .....                                               | 11 |

| 图表 12: MtM 设备 (W2W 永久键合、光刻、临时键合和解键合设备) 的技术路线图与相关应用 .....              | 13 |

| 图表 13: 晶圆键合及后续工艺流程 .....                                              | 14 |

| 图表 14: 晶圆键合工艺及典型器件 .....                                              | 15 |

| 图表 15: 混合键合优点之一：几乎消除了信号丢失 .....                                       | 16 |

| 图表 16: SoIC 和 SoIC+ 的凸块密度路线图 .....                                    | 16 |

| 图表 17: 三维集成的主要晶圆键合技术示意图 .....                                         | 16 |

| 图表 18: 混合键合流程示意图 .....                                                | 16 |

| 图表 19: 2020–2026 年 MtM 设备 (W2W 永久键合、光刻、临时键合和解键合设备) 市场规模预测（十亿美元） ..... | 17 |

| 图表 20: 全球 MtM 设备厂商 .....                                              | 19 |

| 图表 21: 2017 年 MtM 设备市场竞争格局（百万美元） .....                                | 19 |

## 1 后摩尔时代，先进封装成为提升芯片性能重要解法

### 1.1 摩尔定律放缓，先进封装日益成为提升芯片性能重要手段

随着摩尔定律放缓，芯片特征尺寸接近物理极限，先进封装成为提升芯片性能，延续摩尔定律的重要手段。先进封装是指处于前沿的封装形式和技术，通过优化连接、在同一个封装内集成不同材料、线宽的半导体集成电路和器件等方式，提升集成电路的连接密度和集成度。当前全球芯片制程工艺已进入 3-5nm 区间，接近物理极限，先进制程工艺芯片的设计难度、工艺复杂度和开发成本大幅增加，摩尔定律逐渐失效，半导体行业进入“后摩尔时代”。集成电路前道制程工艺发展受限，但随着人工智能等新兴应用场景的快速发展，对于芯片性能的要求日益提高，越来越多集成电路企业转向后道封装工艺寻求先进技术方案，以确保产品性能的持续提升。以系统级封装（SiP）、倒装焊封装（FC）、扇出型集成电路封装（Fan-Out）等为代表的先进封装技术应运而生，在“后摩尔时代”逐步发展为推动芯片性能提升的主要研发方向，也成为封装产业增长的主要驱动力。

图表1：全球封装技术向先进封装迈进

| 阶段   | 起始时间       | 封装形式                                            | 具体典型的封装形式                                                                       |

|------|------------|-------------------------------------------------|---------------------------------------------------------------------------------|

| 第一阶段 | 20世纪70年代以前 | 通孔插装型封装                                         | 晶体管封装（TO）、陶瓷双列直插封装（CDIP）、塑料双列直插封装（PDIP）、单列直插式封装（SIP）等                           |

| 第二阶段 | 20世纪80年代以后 | 表面贴装型封装                                         | 塑料有引线片式载体封装（PLCC）、塑料四边引线扁平封装（PQFP）、小外形表面封装（SOP）、无引线四边扁平封装（PQFN）、双边扁平无引脚封装（DFN）等 |

| 第三阶段 | 20世纪90年代以后 | 球栅阵列封装（BGA）                                     | 塑料焊球阵列封装（PBGA）、陶瓷焊球阵列封装（CBGA）、带散热器焊球阵列封装（EBGA）、倒装芯片焊球阵列封装（FC-BGA）               |

|      |            | 芯片级封装（CSP）                                      | 引线框架型CSP封装、柔性插入板CSP封装、刚性插入板CSP封装、圆片级CSP封装                                       |

| 第四阶段 | 20世纪末开始    | 多芯片组封装（MCM）                                     | 多层陶瓷基板（MCM-C）、多层薄膜基板（MCM-D）、多层印制板（MCM-L）                                        |

|      |            |                                                 | 系统级封装（SiP）、芯片上制作凸点（Bumping）                                                     |

| 第五阶段 | 21世纪前十年开始  | 晶圆级系统封装-硅通孔（TSV）、扇出型集成电路封装（Fan-Out）、三维立体封装（3D）等 |                                                                                 |

资料来源：艾森半导体招股说明书，中邮证券研究所

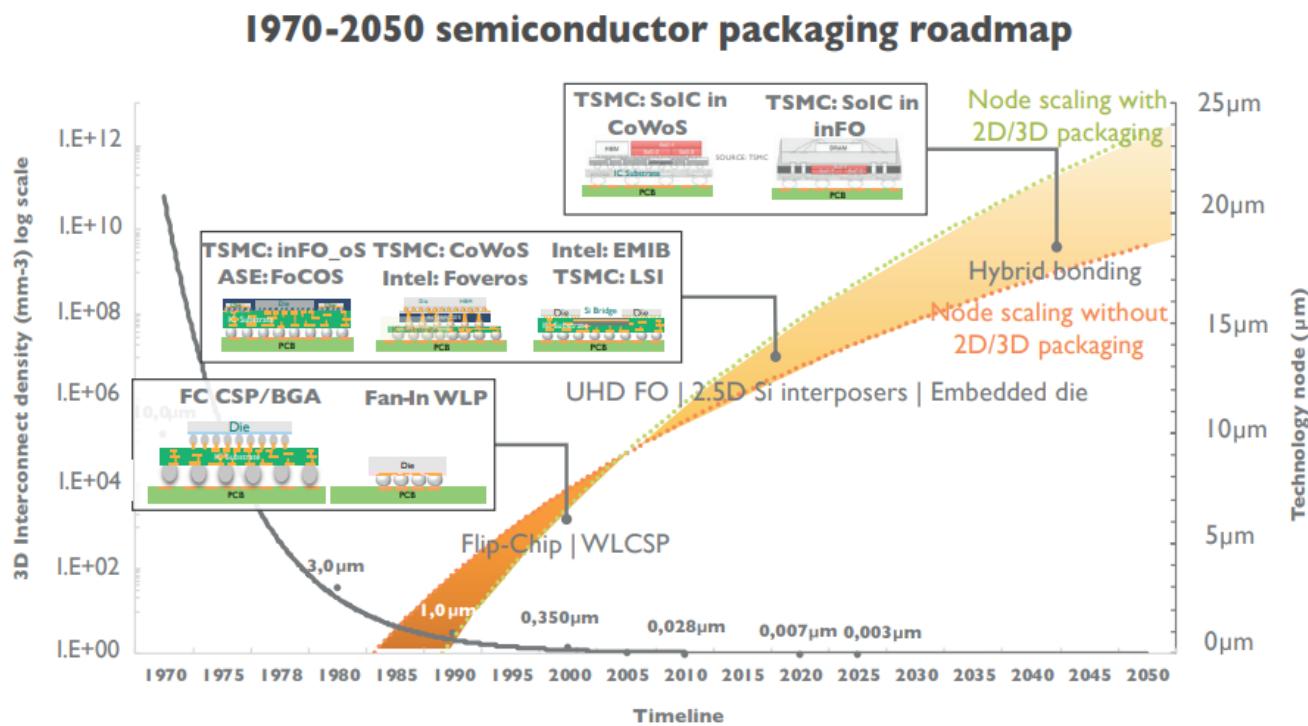

图表2：半导体封装技术演进路线图

资料来源：Yole，中邮证券研究所

## 1.2 先进封装份额占比提升，2.5D/3D 封装增速领先先进封装

**AI 带动先进封装需求。** TrendForce 报告指出，聊天机器人等生成式 AI 应用爆发式增长，带动 2023 年 AI 服务器开发大幅扩张。这种对高端 AI 服务器的依赖，需要使用高端 AI 芯片，这不仅将拉动 2023~2024 年 HBM 的需求，而且预计还将在 2024 年带动先进封装产能增长 30~40%。

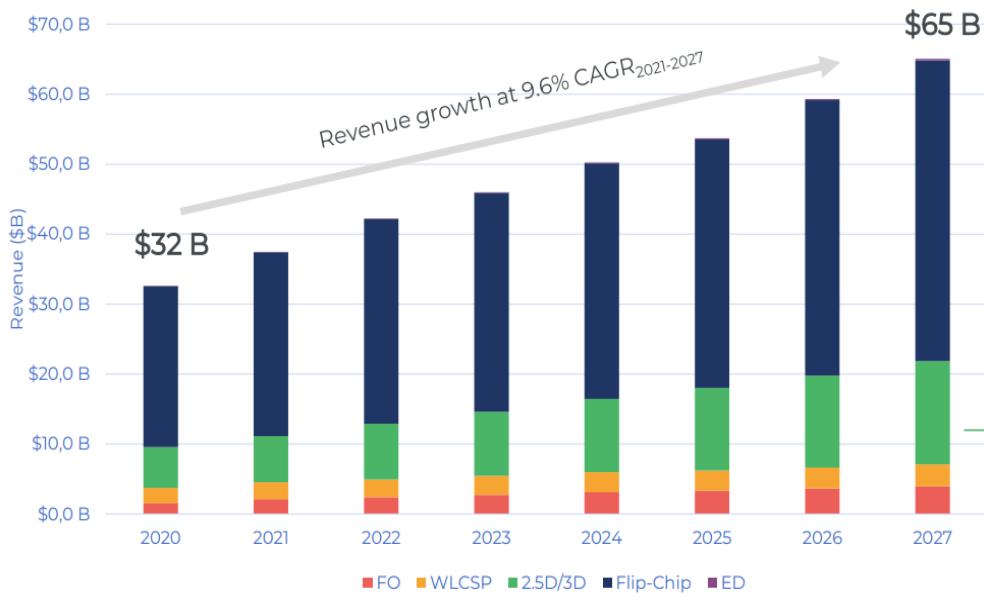

**先进封装增速高于整体封装，2.5D/3D 封装增速居先进封装之首。**根据 Yole，2021 年，先进封装市场规模约 375 亿美元，占整体封装市场规模的 44%，预计到 2027 年将提升至占比 53%，约 650 亿美元， $CAGR_{21-27}$  为 9.6%，高于整体封装市场规模  $CAGR_{21-27}$  6.3%。先进封装中的 2.5D/3D 封装多应用于(x)PU, ASIC, FPGA, 3D NAND, HBM, CIS 等，受数据中心、高性能计算、自动驾驶等应用的驱动，2.5D/3D 封装市场收入规模  $CAGR_{21-27}$  高达 14%，在先进封装多个细分领域中位列第一。

图表3：2020-2027年先进封装市场收入规模预测（单位：十亿美元）

资料来源：Yole，中邮证券研究所

### 1.3 先进封装处于晶圆制造与封测的交叉区域

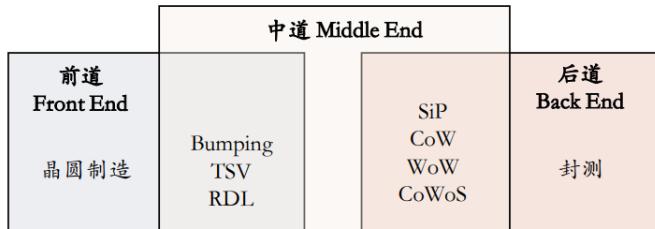

先进封装处于晶圆制造与封测制程中的交叉区域，涉及 IDM、晶圆代工、封测厂商。先进封装要求在晶圆划片前融入封装工艺步骤，具体包括应用晶圆研磨薄化、重布线 (RDL)、凸块制作 (Bumping) 及硅通孔 (TSV) 等工艺技术，涉及与晶圆制造相似的光刻、显影、刻蚀、剥离等工序步骤，从而使得晶圆制造与封测前后道制程中出现中道交叉区域，如图表 4 所示。

前后道大厂争先布局先进封装，竞争格局较为集中。后摩尔时代，先进制程成本快速提升，一些晶圆代工大厂发展重心正在从过去追求更先进纳米制程，转向封装技术的创新。诸如台积电、英特尔、三星、联电等芯片制造厂商纷纷跨足封装领域。先进封装竞争格局较为集中，全球主要的 6 家厂商，包括 2 家 IDM 厂商(英特尔、三星)，一家代工厂商(台积电)，以及全球排名前三的封测厂商(日月光、Amkor、JCET)，共处理了超过 80% 的先进封装晶圆。

图表4：先进封装处于晶圆制造与封测制程中的交叉区域

图表5：2021年先进封装按晶圆拆分市场份额(300MM EQ WSPY)

资料来源：艾森半导体招股说明书，中邮证券研究所

资料来源：Yole，中邮证券研究所

## 2 CoWoS：台积电的2.5D先进封装技术

**CoWoS (Chip On Wafer On Substrate)** 是台积电的一种2.5D先进封装技术，由**CoW**和**oS**组合而来：先将芯片通过**Chip on Wafer (CoW)**的封装制程连接至硅晶圆，再把**CoW**芯片与基板(**Substrate**)连接，整合成**CoWoS**。核心是将不同的芯片堆叠在同一片硅中介层实现多颗芯片互联。在硅中介层中，台积电使用微凸块(**µBumps**)、硅通孔(**TSV**)等技术，代替了传统引线键合用于裸片间连接，大大提高了互联密度以及数据传输带宽。**CoWoS**技术能够提高系统性能、降低功耗、缩小封装尺寸，也为台积电在后续的封装技术保持领先奠定了基础。

图表6：CoWoS结构：**CoW+oS**

资料来源：Wikichip，中邮证券研究所

根据采用的不同的中介层 (interposer)，台积电把 CoWoS 封装技术分为三种类型——CoWoS-S (Silicon Interposer)、CoWoS-R (RDL Interposer) 以及 CoWoS-L (Local Silicon Interconnect and RDL Interposer)。

## 2.1 CoWoS-S：最经典的 CoWoS 技术，以硅基板作为中介层

CoWoS-S (Silicon Interposer) 即 2011 年首次亮相的用硅 (Si) 衬底作为中介层的先进封装技术 (chip-on-wafer-on-substrate with silicon interposer)，提供广泛的中介层尺寸、HBM 立方体数量和封装尺寸，可以实现大于 2X 的光罩尺寸 ( $1,700\text{mm}^2$ )，中介层集成了领先的 SoC 芯片和四个以上的 HBM2/HBM2E 立方体。在过去，“CoWoS”一般即指以硅基板作为中介层的先进封装技术。

图表7：CoWoS-S 结构

资料来源：台积电官网，中邮证券研究所

CoWoS-S 从 2011 年的第一代升级到 2021 年的第五代，第六代技术有望于 2023 年推出，将会在基板上封装 2 颗运算核心，同时可以板载多达 12 颗 HBM 缓存芯片。第五代 CoWoS-S 技术使用了全新的 TSV 解决方案，更厚的铜连接线，晶体管数量是第 3 代的 20 倍。它的硅中介层扩大到  $2500\text{mm}^2$ ，相当于 3 倍光罩面积，拥有 8 个 HBM2E 堆栈的空间，容量高达 128 GB。并且，台积电以 Metal TIM 形式提供最新高性能处理器散热解决方案，与第一代 Gel TIM 相比，封装热阻降低至 0.15 倍。

图表8: CoWoS-S 技术演进

资料来源：台积电官网，中邮证券研究所

## 2.2 CoWoS-R: 使用 RDL 替代硅作为中介层

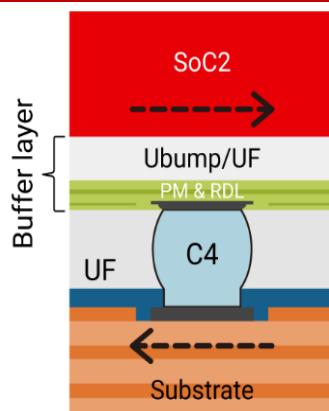

CoWoS-R (RDL Interposer) 是使用有机基板/重新布线层 (RDL) 替代了硅 (Si) 作为中介层的先进封装技术。CoWoS-R 采用 InFO 技术使用 RDL 作为中介层并为 chiplets 之间的互连提供服务，特别是在 HBM (高带宽存储器) 和 SoC 异构集成中。RDL 中介层由聚合物和铜走线组成，机械灵活性相对较高，这种灵活性增强了 C4 接头的完整性，并允许新封装可以扩大其尺寸以满足更复杂的功能需求。

图表9: CoWoS-R 结构

资料来源：台积电官网，中邮证券研究所

图表10: CoWoS-R 缓冲原理

资料来源：台积电官网，中邮证券研究所

CoWoS-R 技术的主要特点包括：

- 1) RDL interposer 由多达 6L 铜层组成，用于最小间距为 4um 间距（2um 线宽/间距）的布线。

- 2) RDL 互连提供良好的信号和电源完整性性能，路由线路的 RC 值较低，可实现高传输数据速率。共面 GSGSG 和具有六个 RDL 互连的层间接地屏蔽可提供卓越的电气性能。

- 3) RDL 层和 C4/UF 层由于 SoC 与相应衬底之间的 CTE 不匹配而提供了良好的缓冲效果。C4 凸块的应变能密度大大降低。

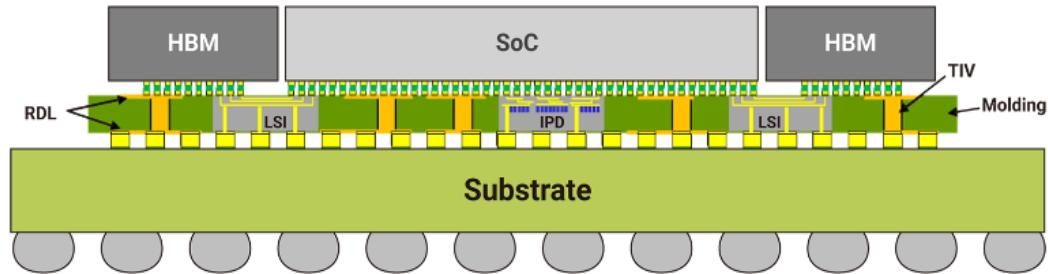

### 2.3 CoWoS-L：使用小芯片和 RDL 作为中介层，融合 CoWoS-S 和 InFO 技术优点

**CoWoS-L (Local Silicon Interconnect and RDL Interposer)** 是使用小芯片 (chiplet) 和 RDL 作为中介层 (硅桥) 的先进封装技术，结合了 CoWoS-S 和 InFO 技术的优点，具有灵活的集成性。CoWoS-L 使用内插器与 LSI (本地硅互连) 芯片进行芯片间互连，以及用于电源和信号传输的 RDL 层，从 1.5 倍 reticle interposer 尺寸和 1 倍 SoC+4 倍 HBM 立方体开始，并将向前扩展，将包络扩大到更大的尺寸，以集成更多芯片。

图表11：CoWoS-L 结构

资料来源：台积电官网，中邮证券研究所

CoWoS-L 服务的主要功能包括：

- 1) LSI 芯片，用于通过多层亚微米铜线实现高布线密度晶粒互连。LSI 芯片可以在每个产品中具有多种连接架构（例如 SoC 到 SoC、SoC 到 chiplet、SoC 到 HBM 等），也可以重复用于多个产品。相应的金属类型、层数和间距与 CoWoS-S 的产品一致。

- 2) 基于成型的中介层，正面和背面具有宽间距的 RDL 层，TIV（通过中介层通孔）用于信号和功率传输，可在高速传输中提供低高频信号损失。

3) 能够在 SoC 芯片下方集成其他元件，例如独立的 IPD（集成无源器件），以支持其与更好的 PI/SI 的信号通信。

### 3 超越摩尔 (MtM) 提速，制造设备为关键

#### 3.1 光刻设备是超越摩尔的支柱，键合设备推动先进封装

在摩尔定律的引导下，集成电路行业始终保持高速发展，晶体管特征尺寸已从 90nm 向 7nm 迈进。随着晶体管特征尺寸日益接近物理极限，量子效应和短沟道效应愈发严重，内部电子自发地通过源极和漏极，导致漏电流增加，限制了晶体管的进一步缩小。因此，按照摩尔定律的方式，通过缩小晶体管特征尺寸来提升集成电路性能、降低功耗变得越发困难，晶体管将会快速地接近约 5nm 的极限栅极长度，因此探索新的沟道材料和器件结构是推动 IC 产业继续发展的两条极为重要的路线。

三维 (Three-dimensional) 集成是超越摩尔 (More than Moore, 下文简称 MtM) 至关重要的研究应用方向。3D 集成的定义是将摩尔晶圆或芯片在垂直于晶圆或芯片平面方向上进行堆叠，集成电路技术由二维平面向三维方向发展，该技术分段实现，首先实现几层的三维封装，随着时间的推移，三维集成芯片层数将会不断增加。采用全新结构的 3D 集成是推动半导体行业发展的重要技术，诸如存储器、逻辑器件、传感器和处理器等不同类型的器件和软件的复杂集成，以及新材料和先进的芯片堆叠技术，都需要基于 3D 集成技术。

晶圆级封装键合技术为实现 3D 集成的有力抓手。3D 集成技术存在晶圆级对准精度、键合完整性、晶圆减薄与均匀性控制以及层内(层间)互联这 4 项挑战，随着摩尔定律逼近材料与器件的物理极限，源于微机电系统 (Micro Electro Mechanical Systems, MEMS) 制造技术的晶圆级封装键合技术逐渐进入集成电路制造领域，成为实现存储器、逻辑器件、射频器件等部件的三维堆叠同质/异质集成，进而提升器件性能和功能，降低系统功耗、尺寸与制造成本的重要技术途径，对满足集成电路高集密度、高功能密度和高性能集成的迫切需求，突破国内自主可控平面集成能力不足的瓶颈，实现集成电路由平面集成向三维立体集成的

跨越式发展有重要的战略价值。因此，英特尔、三星及台积电等知名企业及众多高校、科研院所均围绕晶圆级封装键合开展了设备、器件、工艺的研究。

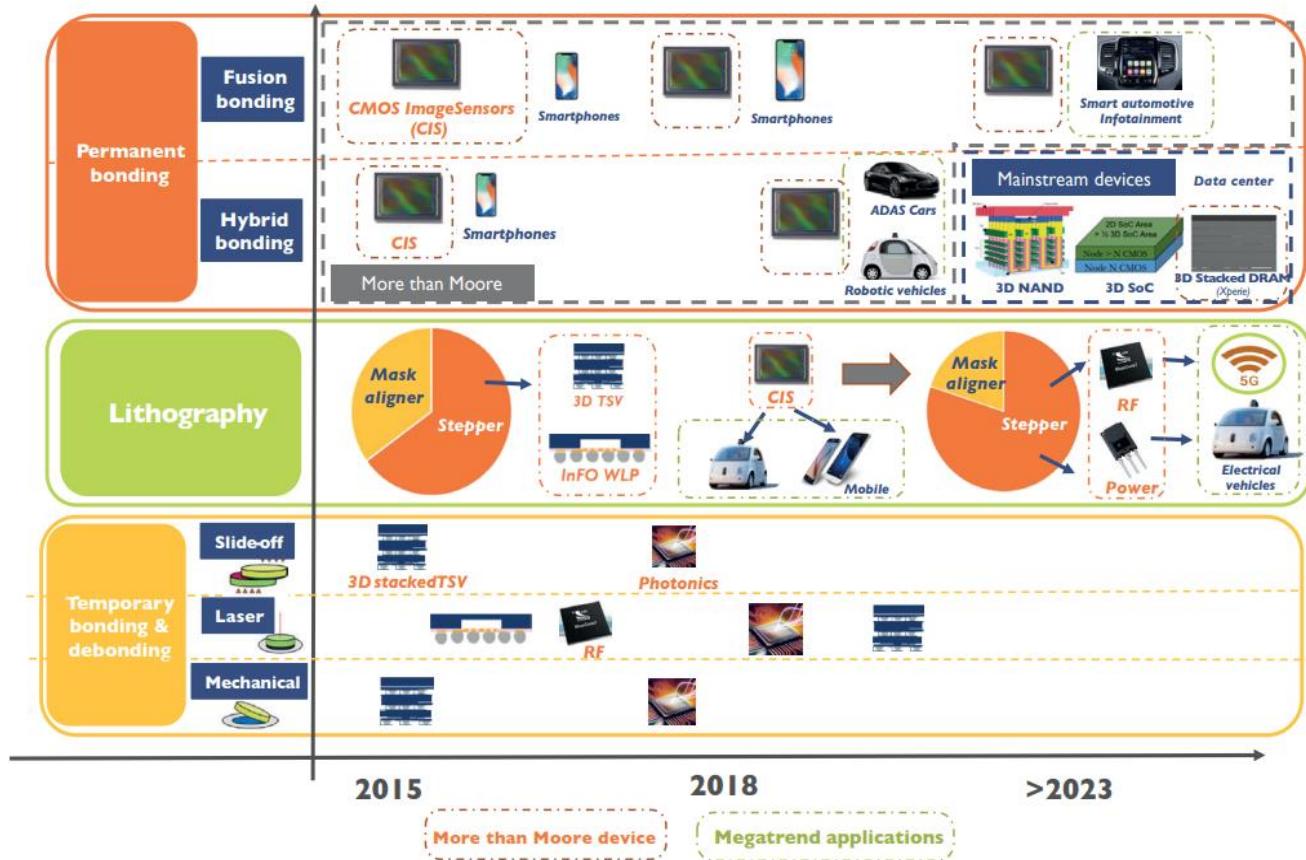

光刻设备是超越摩尔变革的支柱，键合设备则推动先进封装的发展。就设备而言，晶圆级封装键合设备和光刻设备因超越摩尔（MtM）提速愈发关键。MtM 市场涵盖 MEMS、CMOS 图像传感器（CIS）、电源和射频（RF）以及先进封装（AP）等，MtM 设备包括晶圆对晶圆（Wafer-to-Wafer, W2W）永久键合、光刻、临时键合和解键合设备，这三类设备的技术路线图和相关应用如下图所示。

图表12：MtM 设备（W2W 永久键合、光刻、临时键合和解键合设备）的技术路线图与相关应用

资料来源：Yole，中邮证券研究所

**光刻设备：**从传统使用的曝光机（mask aligner）正持续过渡到步进投影光刻机或扫描仪，同时加速采用无掩模光刻。这种变化是由超越摩尔器件微型化、超越摩尔器件与其他超越摩尔单元或主流器件集成在芯片或系统中，以及增加图案化过程良率所驱动的。器件集成的趋势如 3D 堆叠和重构晶圆，需要对光刻设备进行修改，以解决先进封装中的键合工艺缺陷。这些缺陷可能包括衬底翘曲、错位和厚度不均匀。

**键合设备：**在永久键合设备方面，背面照明（BSI）CMOS 图像传感器的混合键合发展迅速。混合键合用于 3D 集成和堆叠，主要用于存储器和逻辑器件。表面活化键合（SAB）现用于硅绝缘体（SOI）和专用于电源及射频应用的工程衬底。临时键合设备则受衬底减薄和处理尤其是先进封装的推动而有较快发展。

### 3.2 MtM 设备（W2W 永久键合、光刻、临时键合和解键合设备）相关工艺与流程

**晶圆键合设备：**晶圆键合设备通过化学和物理作用将两块同质或异质晶片紧密地结合起来，从而实现微电子材料、光电材料及其纳米等级微机电元件的电气互联、功能集成和器件封装。晶圆键合设备广泛应用于射频器件、惯性器件、光电器件、信息处理器件及 3D 集成逻辑集成电路的先进封装制造，对位精度、键合温度均匀性、键合压力范围及控制精度对晶圆键合工艺具有重要影响。

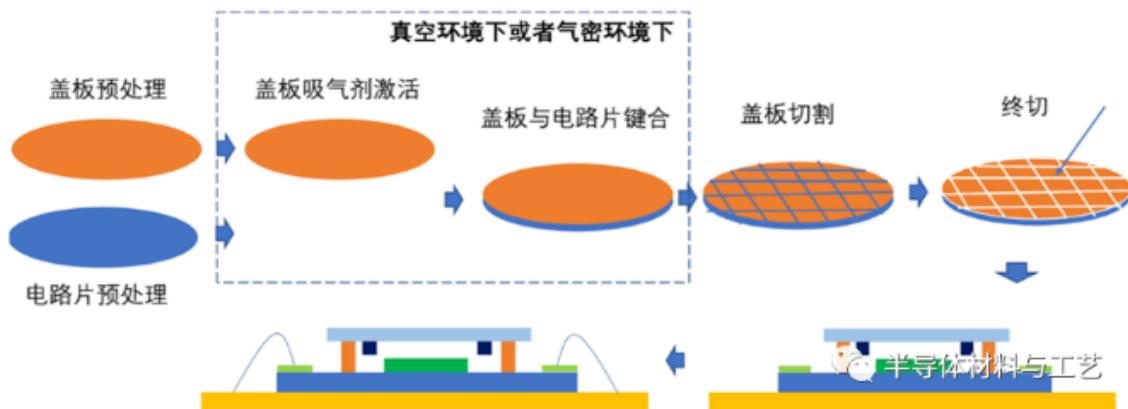

**晶圆键合工艺过程：**首先将待键合的一组晶圆进行预处理、清洗、视觉对准，进而通过不同方法实现晶圆对的键合。晶片接合后，界面的原子受到外力的作用而产生反应形成共价键结合成一体，并使接合界面达到特定的键合强度，称之为**永久性键合**。若借助粘结剂将晶片接合，也可作为**临时键合**，通过将器件晶圆固定在承载晶圆上，可为超薄器件晶圆提供足够的机械支撑，保证器件晶圆能够顺利安全地完成后续工艺制程，如光刻、刻蚀、钝化、溅射、电镀和回流焊。

图表13：晶圆键合及后续工艺流程

资料来源：半导体材料与工艺，中邮证券研究所

具体的晶圆键合工艺可按照键合材料、键合手段、应用场景分类，方法不尽相同，按照键合工艺对晶圆键合分类如下图表：

**图表14：晶圆键合工艺及典型器件**

| 工艺                                                    | 要点                                                                                      | 典型器件及应用                                    |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------|

| 阳极键合 (Anodic Bonding)                                 | 硅/金属和玻璃绝缘体之间产生密封，无需中间层。高碱离子浓度硼硅酸盐玻璃是该工艺的主要要求，加热键合，对基底材料施加电场，洁净，原子接触                     | MEMS器件，硅-玻璃键合，临时键合                         |

| 高真空键合 (High Vacuum Wafer Bonding Technology)          | 高真空处理和加工，晶圆表面活化，无氧化物直接键合，室温直接键合，具有真空下校准能力，无吸气剂高真空封装                                     | 工程基板，MEMS封装，“超CMOS”器件，叠层太阳能电池，高性能逻辑器件，功率器件 |

| 芯片到晶圆熔融与混合键合 (Die-to-Wafer Fusion and Hybrid Bonding) | 1) Co-D2W：载体制备、载体填充、晶圆键合（临时和永久）和载体分离；<br>2) DP-D2W：载流子填充、芯片清洁和激活以及直接放置倒装芯片              | 高带宽存储器，小芯片，3D堆叠式背面照明CMOS图像传感器              |

| 晶圆共晶键合 (Eutectic Bonding)                             | 共晶温度远低于粘结过程中材料的熔化温度，对不规则表面、划痕和颗粒不太敏感，从而有利于大批量生产，有更好的脱气性和气密性                             | Al-Ge、Au-Sn和Au-In等MEMS器件，陀螺仪               |

| 熔融与混合键合 (Fusion and Hybrid Bonding)                   | 在环境条件下的预键合，小于100nm的非常高的对准允许使用晶圆到晶圆熔合键合。铜焊盘可与介电层平行加工，允许在环境温度下预结合介电层，而在退火期间可通过金属扩散结合实现电接触 | CMOS图像传感器，存储器以及三维上系统(SoC)                  |

| 金属扩散键合 (Metal Diffusion Bonding)                      | 具有高扩散率的金、铝和铜是最稳定的材料，用于热压键合。与铝和铜相比，金需要较少的扩散温度，并且具有不被氧化的额外优势                              | RF-MEMS，发光二极管(LED)，激光二极管以及功率器件             |

| 临时键合与解键合 (Temporary Bonding and Debonding)            | 临时键合是为薄品片或将超薄品片提供机械支撑的一个重要过程                                                            | 超薄芯片和封装                                    |

| 瞬时液相键合 (Transient Liquid Phase Bonding)               | 与共晶键合相比，液相键合界面通过扩散而不是冷却到熔点以下而凝固，形成具有快速扩散特性和高可靠性的组合物                                     | 高可靠性键合线或电气连接的场合                            |

资料来源：半导体材料与工艺，中邮证券研究所

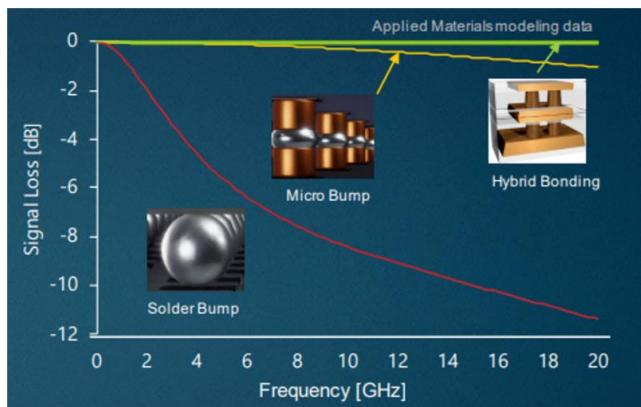

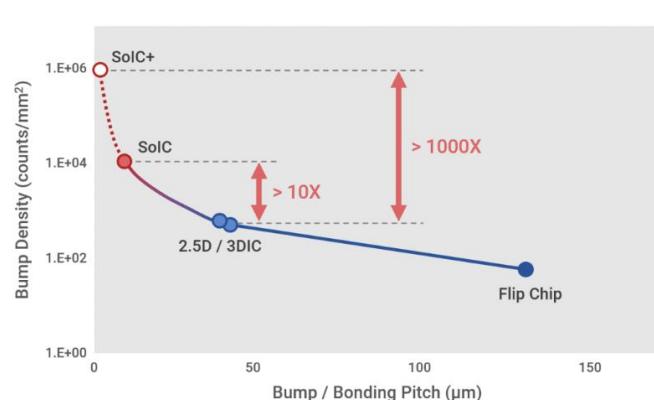

**熔融与混合键合：**使得芯片在性能上能够实现相当于更低工艺节点性能。混合键合技术涉及芯片到晶圆或晶圆之间铜焊点的连接，这些铜焊点承载着功率、信号以及周围的电介质，提供比铜微凸点多1000倍的连接性能；可将信号延迟降低到可忽略不计的水平，同时将凸点密度提高到比2.5D集成方案高三个数量级。虽然目前仅限于选择HBM和处理器/缓存等高端应用，但混合键合很快将会应用到3D DRAM、RF调制解调器和microLED的GaN/Si键合等领域。另外，在最需要提高性能和功率的时候，混合键合为晶体管节点缩放提供了一种可行的替代方案。例如，AMD的Ryzen 7-5800X3D处理器采用台积电的SoIC(集成芯片系统)7nm工艺制造。尽管并未使用5nm工艺，但芯片性能仍提高了15%，功耗降低了3倍。AMD报告指出，通过混合键合，芯片在性能上能够实现相当于更低工艺节点性能。

图表15：混合键合优点之一：几乎消除了信号丢失

资料来源：应用材料，云脑智库，中邮证券研究所

图表16：SoIC 和 SoIC+ 的凸块密度路线图

资料来源：台积电，云脑智库，中邮证券研究所

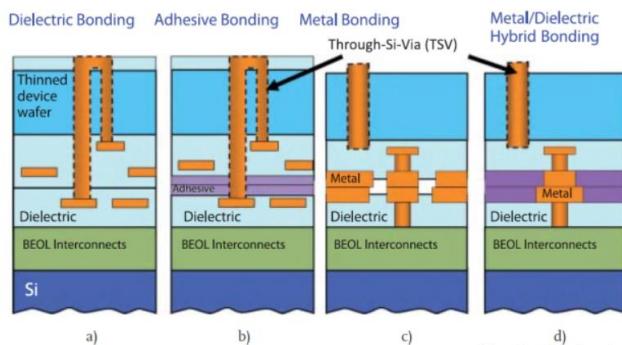

**熔融与混合键合：扫除晶圆键合走向 CMOS 互联工艺的最大障碍。**通过晶圆键合的方式实现的三维互联的方式有多种，但如下图中(a)所示的熔融键合方案和(d)所示的混合键合方案，更适合先进的 CMOS 工艺。金属热压键合(c)需要使用极高的压力(10–100kN)，甚至类似阳极键合还会使用高压电场，不利于实现与 CMOS 的工艺兼容性，容易破坏其前道的金属图形，因此仅需要常温键合+低温退火的熔融键合和混合键合(d)便因其与 CMOS 良好的工艺兼容性，得到了越来越多的青睐。**熔融键合**从早期需要 1000°C 高温进行数小时退火的工艺条件，发展到只需要常压等离子表面活化后常温键合之后，在不足 400°C 的条件下退火，甚至在超高真空下使用等离子表面活化后无需退火，为其强大的 CMOS 工艺兼容性提供了保障。而不借助 TSV 直接使用铜触点进行互联的**混合键合**，将上下晶圆间的互联距离缩小到了最短，进一步提升了电学性能。

图表17：三维集成的主要晶圆键合技术示意图

资料来源：半导体行业观察，Handbook of Wafer Bonding, Chap. 15，中邮证券研究所

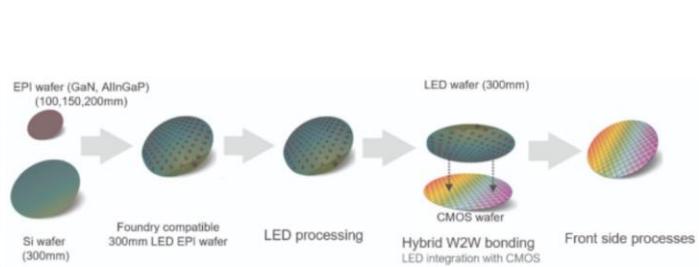

图表18：混合键合流程示意图

资料来源：半导体行业观察，Integrating microLEDs with advanced CMOS, Compound Semiconductor, 2022，中邮证券研究所

### 3.3 MtM 设备市场规模

整个半导体设备市场价值数十亿美元，相比之下，MtM 的永久键合、临时键合和解键合、光刻设备市场是一个数百万美元的小众市场。然而，5G 等大趋势应用市场将 MtM 设备的复杂性推向了新的水平，引致大笔投资。Yole 测算 2020 年全球这三类 MtM 设备总规模为 13.8 亿美元，预计到 2026 年将超过 24 亿美元（CAGR<sub>2020-2026</sub> 为 10%），其高速增长主要是由光刻设备驱动，其次为 W2W 永久键合设备。

MtM 设备的光刻设备市场主要由先进封装驱动。先进封装目前占整个 MtM 光刻工具市场规模的近 60%，并将继续以步进技术主导该行业。

W2W 永久键合设备市场预计将由新兴的 CIS 产品推动；同时，3D NAND 和 3D SoC 等新的主流半导体应用也将在未来五年内大力推动 W2W 永久键合设备市场的增长。

临时键合和解键合设备受益于 3D TSV 等先进封装，亦有极大的发展空间。临时键合和解键合设备仍然是一个相对较小的利基市场，但已经应用于较多 MtM 领域，如 3D TSV 平台，扇出晶圆级封装（FO WLP），MEMS 和传感器，电源器件和光电子应用。从技术角度来看，激光解键合代表了目前广泛用于 FO WLP 和 2.5D 中间层封装的主导技术，在三星、SK 海力士、美光等主要存储器制造企业的支持下，激光解键合预计将继续保持领先地位。

图表19：2020–2026 年 MtM 设备（W2W 永久键合、光刻、临时键合和解键合设备）市场规模预测（十亿美元）

资料来源：Yole，中邮证券研究所

### 3.4 MtM 设备厂商

目前 MtM 设备的市场格局呈现国际厂商主导，国产厂商起步发展的状态。随着先进封装趋势向着更复杂的异质集成、更大的封装载体、更薄的芯片以及更小的封装尺寸等方向发展，发达国家晶圆键合设备市场已比较成熟，而我国市场仍处成长阶段。

随着 3D 封装技术的发展，在企业不断加大资金投入的基础上，晶圆键合系列设备市场将迎来井喷式发展。目前，国际一流晶圆键合设备厂商主要包括奥地利 EVG 公司与德国 SUSS MicroTec 公司等。

奥地利 EVG 公司的主流产品，适合阳极键合、共晶键合、金属扩散键合、直接键合、聚合物键合、熔融与混合键合和瞬时液相键合的小批量、半自动晶圆键合解决方案，如 EVG510、EVG520、EVG540 晶圆键合系统；也可以提供全自动、大批量、满足 3D 异构集成高对准精度生产的晶圆键合解决方案，如 EVG560、EVG GEMINI、EVG Combond、EVG Bondscale 等晶圆键合系统；还有用于扇出封装、晶圆减薄、3D 堆叠、晶圆键合的临时键合和晶圆解键合解决方案，如 EVG850、EVG850TB、EVG850LT 等晶圆临时键合与解键合系统；晶圆对准设备由 Smartview 发展到 Smartview3，对准精度提高到 50nm。

德国 SUSS MicroTec 拥有六十多年的历史，是半导体行业领先的微结构工艺设备制造商，产品涵盖光刻、涂胶/显影、晶圆键合、光刻掩膜版清洗等诸多半导体、微加工相关领域。SUSS 晶圆键合系统主要包括 XB8、SB6/8Gen2、XBS200、XBS300、XBC300Gen2 等系统，最大晶圆尺寸 304.8 mm (12 英寸)，对准精度  $\leq 50$  nm，能够满足包括共晶、直接键合等各种晶圆键合工艺需求。

晶圆键合设备总体技术发展方向是高精度、高集成化、高可靠性、高动态、高效化的趋势，关键技术指标为：对准精度  $\leq 50$  nm；键合温度均匀性  $\leq \pm 1\%$ ；最大晶圆尺寸 304.8 mm (12 英寸)；最大键合压力 100 kN；最高键合温度 550 °C。

根据 Yole 对 2020 年超越摩尔光刻机的市场格局测算，佳能是超越摩尔光刻机销售的领导者，拥有 34% 的市场份额，提供多种工具。同时，ASML 正在接近佳能，占有 21% 的份额。我国国内市场先进封装光刻设备的销售由 SMEE (上海微电子装备) 推动，而德国 SUSS MicroTec 仍然是掩模对准曝光机销售的主导厂商。

图表20：全球 MtM 设备厂商

资料来源：Yole，中邮证券研究所

图表21：2017 年 MtM 设备市场竞争格局（百万美元）

资料来源：Yole，中邮证券研究所

### 国内厂商：

1) 拓荆科技：不断开拓混合键合设备。公司积极进军高端半导体设备的前沿技术领域，研制了应用于晶圆级三维集成领域的混合键合 (Hybrid Bonding) 设备产品系列，同时，该设备还能兼容熔融键合 (Fusion Bonding)。公司混合键合系列产品包括晶圆对晶圆键合 (Wafer to Wafer Bonding) 产品和芯片对晶圆键合表面预处理 (Die to Wafer Bonding Preparation and Activation) 产品，可以实现直接或基于层间的键合工艺、复杂的常温共价键合工艺。

公司的晶圆对晶圆键合产品可以实现复杂的 12 英寸晶圆对晶圆常温共价键合，搭载了晶圆表面活化、清洗、键合和自研的键合精度检测模块，具有对准精度高、产能高、无间隙等性能特点。截至 2022 年末，公司成功研制了首台晶圆对晶圆键合产品 Dione 300，并出货至客户端进行验证，取得了突破性进展。

公司的芯片对晶圆键合表面预处理产品可以实现芯片对晶圆键合前表面预处理工序，包括晶圆及切割后芯片的表面活化及清洗工艺。截至 2022 年末，公司已完成芯片对晶圆键合表面预处理产品 Pollux 的研发。截至 2023 年 4 月 18 日，该产品已出货至客户端进行验证。

2) 芯源微：持续发力临时键合和解键合设备。在后道先进封装领域，公司作为行业龙头持续提升机台各项技术指标，全新的 BHP 盘体平衡压技术可应用于 Chiplet 等新兴先进封装领域，在更高工艺等级下实现了产品良率的提升；化学药液管控技术实现了对强挥发性、强腐蚀性化学药液挥发物的精准管控，达到了更高标准的机台耐腐蚀等级和产品工艺效果；新开发的激光解键合去胶清洗技术，

实现了在同一机台内完成激光解键合-RL 层清洗-TB 胶层清洗等多种工艺，可有效提升客户生产效率。截至 2022 年末，公司在多项工艺能力上达到了更高水平，力争为客户提供更具价值的产品解决方案，同时积极定义下一代产品。

在 Chiplet 技术中，为了缩小芯片体积、提高芯片散热性能和传导效率等，晶圆减薄工艺会被大量应用，为了不损伤减薄中以及减薄后晶圆，需要将晶圆片与玻璃基板临时键合并在完成后续工艺后最终解键合。同时在 Chiplet 技术路线 Fout、CoWoS 等封装工艺路线都要经过单次或多次的临时键合及解键合工艺来实现芯粒互联。针对以上半导体工艺应用场景，公司已成功研发临时键合机、解键合机产品，目前临时键合机正在进行客户端验证。

## 中邮证券投资评级说明

| 投资评级标准                                                                                                                                                                                     | 类型    | 评级   | 说明                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------------------------|

| 报告中投资建议的评级标准：<br>报告发布日后的6个月内相对市场表现，即报告发布日后的6个月内公司股价（或行业指数、可转债价格）的涨跌幅相对同期相关证券市场基准指数的涨跌幅。<br>市场基准指数的选取：A股市场以沪深300指数为基准；新三板市场以三板成指为基准；可转债市场以中信标普可转债指数为基准；香港市场以恒生指数为基准；美国市场以标普500或纳斯达克综合指数为基准。 | 股票评级  | 买入   | 预期个股相对同期基准指数涨幅在20%以上      |

|                                                                                                                                                                                            |       | 增持   | 预期个股相对同期基准指数涨幅在10%与20%之间  |

|                                                                                                                                                                                            |       | 中性   | 预期个股相对同期基准指数涨幅在-10%与10%之间 |

|                                                                                                                                                                                            |       | 回避   | 预期个股相对同期基准指数涨幅在-10%以下     |

|                                                                                                                                                                                            | 行业评级  | 强于大市 | 预期行业相对同期基准指数涨幅在10%以上      |

|                                                                                                                                                                                            |       | 中性   | 预期行业相对同期基准指数涨幅在-10%与10%之间 |

|                                                                                                                                                                                            |       | 弱于大市 | 预期行业相对同期基准指数涨幅在-10%以下     |

|                                                                                                                                                                                            | 可转债评级 | 推荐   | 预期可转债相对同期基准指数涨幅在10%以上     |

|                                                                                                                                                                                            |       | 谨慎推荐 | 预期可转债相对同期基准指数涨幅在5%与10%之间  |

|                                                                                                                                                                                            |       | 中性   | 预期可转债相对同期基准指数涨幅在-5%与5%之间  |

|                                                                                                                                                                                            |       | 回避   | 预期可转债相对同期基准指数涨幅在-5%以下     |

## 分析师声明

撰写此报告的分析师（一人或多人）承诺本机构、本人以及财产利害关系人与所评价或推荐的证券无利害关系。

本报告所采用的数据均来自我们认为可靠目前已公开的信息，并通过独立判断并得出结论，力求独立、客观、公平，报告结论不受本公司其他部门和人员以及证券发行人、上市公司、基金公司、证券资产管理公司、特定客户等利益相关方的干涉和影响，特此声明。

## 免责声明

中邮证券有限责任公司（以下简称“中邮证券”）具备经中国证监会批准的开展证券投资咨询业务的资格。

本报告信息均来源于公开资料或者我们认为可靠的资料，我们力求但不保证这些信息的准确性和完整性。报告内容仅供参考，报告中的信息或所表达观点不构成所涉证券买卖的出价或询价，中邮证券不对因使用本报告的内容而导致的损失承担任何责任。客户不应以本报告取代其独立判断或仅根据本报告做出决策。

中邮证券可发出其它与本报告所载信息不一致或有不同结论的报告。报告所载资料、意见及推测仅反映研究人员于发出本报告当日的判断，可随时更改且不予通告。

中邮证券及其所属关联机构可能会持有报告中提到的公司所发行的证券头寸并进行交易，也可能为这些公司提供或者计划提供投资银行、财务顾问或者其他金融产品等相关服务。

《证券期货投资者适当性管理办法》于2017年7月1日起正式实施，本报告仅供中邮证券客户中的专业投资者使用，若您非中邮证券客户中的专业投资者，为控制投资风险，请取消接收、订阅或使用本报告中的任何信息。本公司不会因接收人收到、阅读或关注本报告中的内容而视其为专业投资者。

本报告版权归中邮证券所有，未经书面许可，任何机构或个人不得存在对本报告以任何形式进行翻版、修改、节选、复制、发布，或对本报告进行改编、汇编等侵犯知识产权的行为，亦不得存在其他有损中邮证券商业性权益的任何情形。如经中邮证券授权后引用发布，需注明出处为中邮证券研究所，且不得对本报告进行有悖原意的引用、删节或修改。

中邮证券对于本申明具有最终解释权。

## 公司简介

中邮证券有限责任公司，2002年9月经中国证券监督管理委员会批准设立，注册资本50.6亿元人民币。中邮证券是中国邮政集团有限公司绝对控股的证券类金融子公司。

中邮证券的经营范围包括证券经纪、证券投资咨询、证券投资基金销售、融资融券、代销金融产品、证券资产管理、证券承销与保荐、证券自营和与证券交易、证券投资活动有关的财务顾问等。中邮证券目前已经在北京、陕西、深圳、山东、江苏、四川、江西、湖北、湖南、福建、辽宁、吉林、黑龙江、广东、浙江、贵州、新疆、河南、山西等地设有分支机构。

中邮证券紧紧依托中国邮政集团有限公司雄厚的实力，坚持诚信经营，践行普惠服务，为社会大众提供全方位专业化的证券投、融资服务，帮助客户实现价值增长。中邮证券努力成为客户认同、社会尊重，股东满意，员工自豪的优秀企业。

## 中邮证券研究所

### 北京

电话：010-67017788

邮箱：yanjiusuo@cnpsec.com

地址：北京市东城区前门街道珠市口东大街17号

邮编：100050

### 上海

电话：18717767929

邮箱：yanjiusuo@cnpsec.com

地址：上海市虹口区东大名路1080号邮储银行大厦3楼

邮编：200000

### 深圳

电话：15800181922

邮箱：yanjiusuo@cnpsec.com

地址：深圳市福田区滨河大道9023号国通大厦二楼

邮编：518048