# 先进封装产业+键合技术发展， 共驱键合设备广阔空间

华安机械

分析师：张帆 执业证书号：S0010522070003 邮箱：zhangfan@hazq.com

分析师：徒月婷 执业证书号：S0010522110003 邮箱：tuyueting@hazq.com

2025年3月20日

华安证券研究所

## 目录

一、终端市场发展与键合设备迭代互为驱动

二、键合技术发展带来设备厂商机遇

三、AI产业浪潮下的键合设备发展

四、设备厂商和投资标的梳理

## 一、终端市场发展与键合设备迭代互为驱动

## 1.1 半导体键合概念

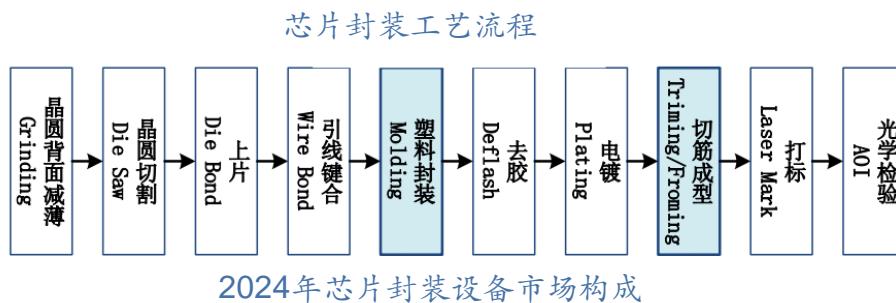

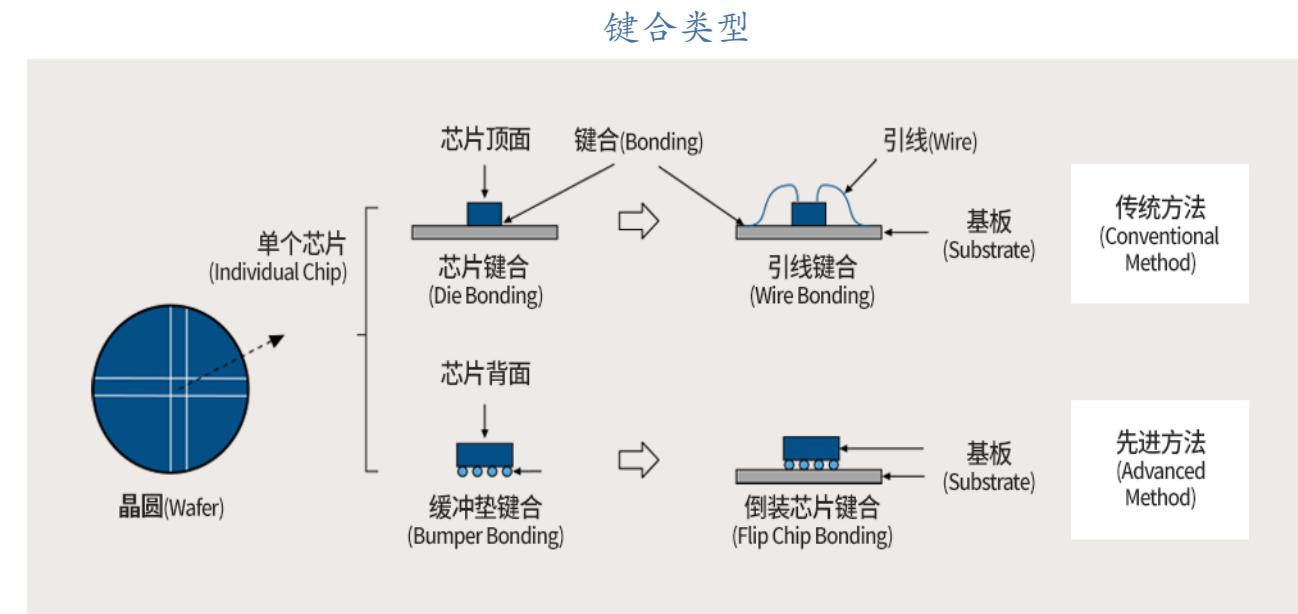

- 半导体后道封装工艺包含背面研磨(Back Grinding)、划片(Dicing)、芯片键合(Die Bonding)、引线键合(Wire Bonding)及成型(Molding)等步骤。这些工艺的顺序可根据封装技术的变化进行调整、相互结合或合并。

- “键合”是指将晶圆芯片固定于基板上。键合工艺可分为传统方法和先进方法两种类型。传统方法采用芯片键合(Die Bonding)（或芯片贴装(Die Attach)）和引线键合(Wire Bonding)，而先进方法则采用IBM于60年代后期开发的倒装芯片键合(Flip Chip Bonding)技术。倒装芯片键合技术将芯片键合与引线键合相结合，并通过在芯片焊盘上形成凸块(Bump)的方式将芯片和基板连接起来。

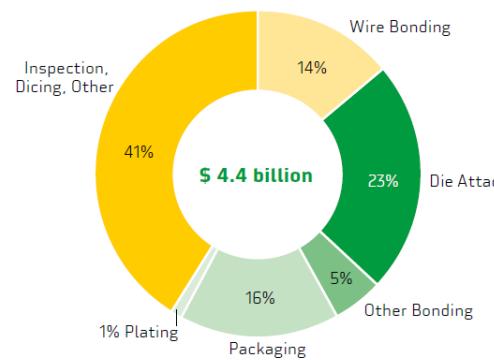

2024年芯片封装设备市场构成

资料来源：BESI、Tech Insights、SK海力士、耐科装备、华安证券研究所整理

## 1.2 键合分类

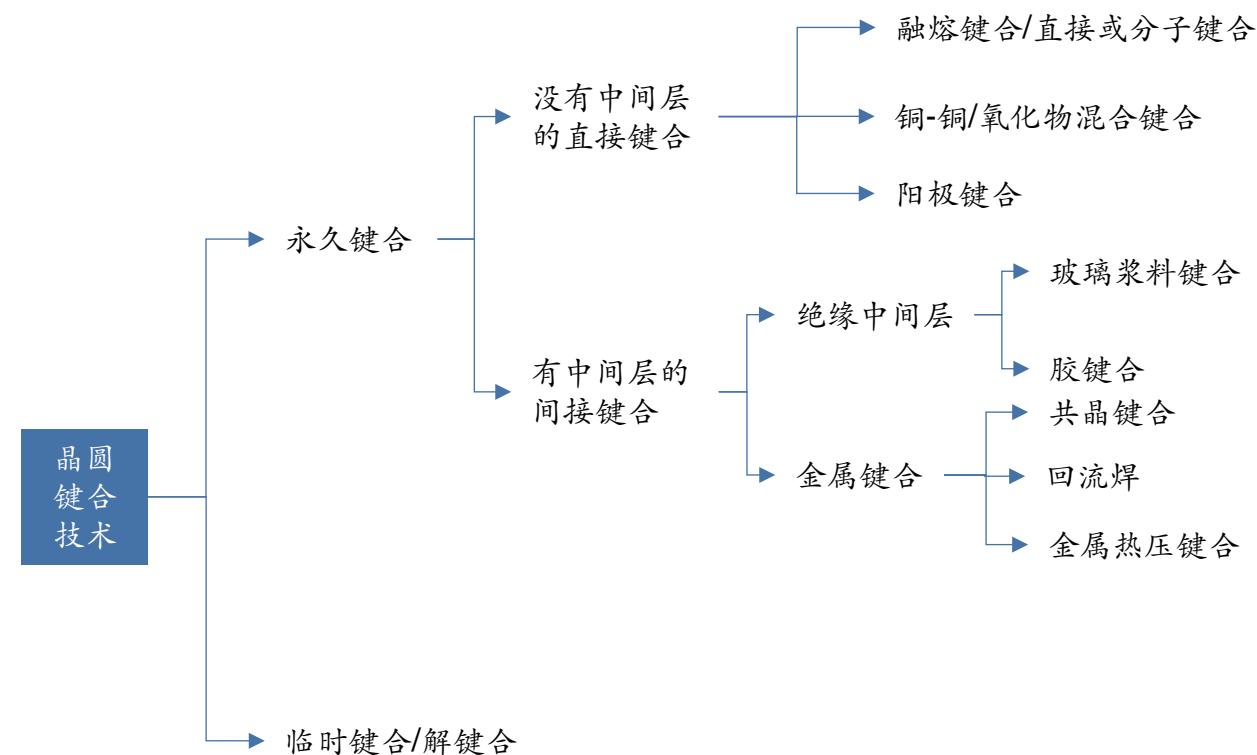

- 按是否需要进行解键合，可以将晶圆键合分为永久键合和临时键合。

- 永久键合后无需解键合，按照封装方案的不同，永久键合可能涉及完整的晶圆或单片芯片，其连接到其他晶圆或再分配层或中介层，目的是保证封装组件键合的永久性，并提供牢固的电、热和机械连接。根据是否有中间层，可以将永久键合分为两种主要类型：

- (1) 没有中间层的直接键合，包括融熔键合/直接或分子键合、铜-铜/氧化物混合键合、阳极键合等；

- (2) 有中间层的间接键合，按照中间层材料分为使用绝缘中间层的玻璃浆料键合、胶键合等，以及使用金属键合的共晶键合、金属热压键合、回流焊等。

- 临时键合是指将晶圆临时键合到一个或多个临时载体衬底上，从而为薄晶片或超薄晶片提供机械支撑，之后再解离的过程。电子产品的小型化要求芯片具有更好的散热和更高性能，因此需要对晶圆进行减薄以达到所需厚度。然而当晶圆的厚度减小到200微米内时，超薄晶圆会变得脆弱并容易发生翘曲。因此半导体行业提出了各种临时粘合/解离(TBDB)技术，在晶圆减薄、加工和转移过程中为超薄晶圆提供机械支撑和物理保护，减少翘曲和破片的风险，以及加工时因晶圆位移等可能产生的缺陷。

资料来源：麦姆斯咨询、华安证券研究所整理

## 1.3 终端市场发展与设备迭代互为驱动

- AI、电动汽车和先进移动设备等终端应用市场的驱动下，永久键合以及临时键合和解键合设备市场持续增长。相对的，光刻和键合设备的升级迭代，是下游市场持续迭代的重要支撑。

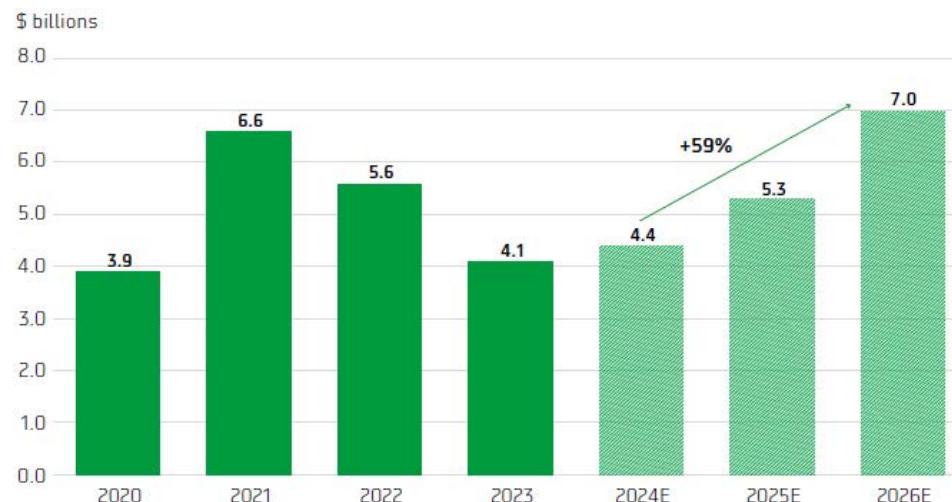

- 根据TechInsights，2024年半导体封装设备市场与2023年相比预计实现增长，但与2021年的上一个周期性峰值相比预计下降。当前的下行周期主要是由2020年和2021年大规模产能建设后主流消费应用需求下降驱动的。2024年主要终端用户市场的需求减少，被生成式AI应用的大幅增长所抵消，主要用于高端计算和数据中心。在持续两年多的行业低迷之后，2024年至2026年组装设备市场预期将增长59%，这受益于半导体单位产量增加，过剩库存消耗，产能利用率上升，以及AI相关先进封装解决方案的需求继续增加。

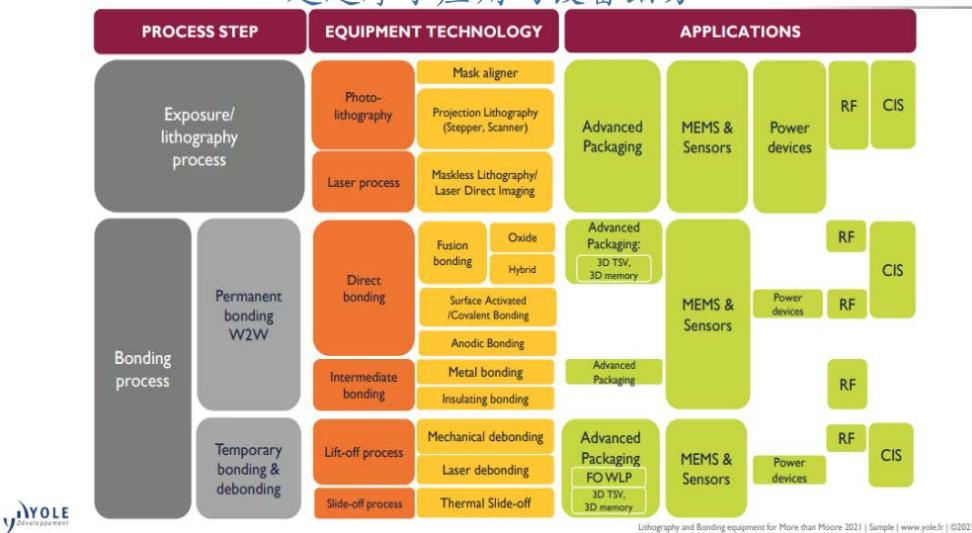

- 光刻设备是超越摩尔器件的制造技术发展的支柱，键合设备的改进则推动了先进封装。在永久键合设备方面，背面照明（BSI）CMOS图像传感器的混合键合正在发展，混合键合也无可争议地被用于存储器和逻辑器件的3D集成和堆叠。临时键合设备的销售则受衬底减薄和处理的推动，尤其是先进封装。

2020-2026E的封装设备市场趋势

超越摩尔应用的设备细分

资料来源：TechInsights、YOLE、华安证券研究所整理

## 1.4 先进封装发展中的键合设备技术升级

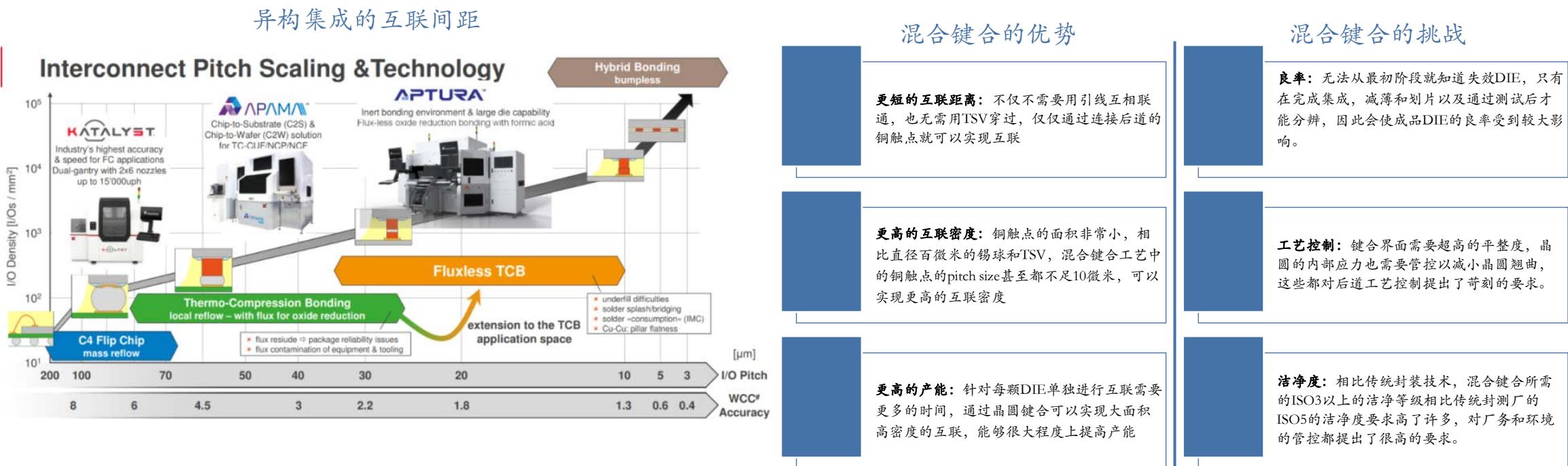

- 摩尔定律驱动先进封装的发展，同样伴随着键合方式的改变，键合技术发展的主线是实现更高密度的互联和更小的封装尺寸。

- 在封装史上，最后一次重大范式转变是从引线键合到倒装芯片：引线键合工艺要求键合焊区的凸点电极沿芯片四周边缘分布，引线的存在也需要塑封体提供保护，从而增加了体积，阻碍了芯片工作时热量的散发。随着器件小型化和复杂化，传统封装使用的引线键合工艺逐渐难以满足行业需求。与传统的引线键合技术相比，倒装芯片焊接技术键合焊区的凸点电极不仅仅沿芯片四周边缘分布，且可以通过再布线实现面阵分布。因而倒装芯片焊接技术具有小尺寸、高密度、高性能等优点。

- 从倒装芯片起，更先进的封装形式（例如晶圆级扇出和TCB）一直是相同核心原理的渐进式改进。未来，随着堆叠需求的增长，密度及精度要求的提升，无焊剂的混合键合工艺有望引领封装范式的下一次转变。

|                 | Wire Bond<br>(1975) | Flip Chip<br>(1995) | TCB Bonding<br>(2012) | HD Fan Out<br>(2015) | Hybrid Bonding<br>(2018) |

|-----------------|---------------------|---------------------|-----------------------|----------------------|--------------------------|

| Architecture    |                     |                     |                       |                      |                          |

| Contact Type    |                     |                     |                       |                      |                          |

| Contact Density |                     |                     |                       |                      |                          |

| Substrate       | Organic/leadframe   | Organic/leadframe   | Organic /Silicon      | None                 | None                     |

| Accuracy        | 20-10 $\mu$ m       | 10-5 $\mu$ m        | 5-1 $\mu$ m           | 5-1 $\mu$ m          | 0.5-0.1 $\mu$ m          |

| Energy/Bit      | 10pJ/bit            | 0.5pJ/bit           | 0.1pJ/bit             | 0.5pJ/bit            | <.05pJ/bit               |

资料来源：Besi、华安证券研究所整理

华安证券

HUAAN SECURITIES

证券研究报告

## 二、键合技术发展带来设备厂商机遇

## 2.1 关注键合技术发展本身带来的设备厂商机会

- 不同键合方式均有其应用场景，往往同一产品的不同流程中综合运用多重键合方式，加上不同器件并存，整体键合设备呈现多样化并存的局面。

- 键合技术随着下游应用领域变化而不断发展，关注键合技术发展本身带来的设备厂商机会。一些晶圆键合设备由MEMS领域应用转化到3D集成技术的先进封装领域，表现出高对准精度特点，并向自动化、集成化方向发展。

| 工艺                                                   | 要点                                                                                      | 典型器件及应用                                     |

|------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------|

| 阳极键合(Anodic Bonding)                                 | 硅/金属和玻璃绝缘体之间产生密封，无需中间层。高碱离子浓度硼硅酸盐玻璃是该工艺的主要要求，加热键合，对基MEMS器件，硅-玻璃键合，临时键合底材料施加电场，洁净，原子接触   | MEMS器件，硅-玻璃键合，临时键合                          |

| 高真空键合(High Vacuum Wafer Bonding Technology)          | 高真空处理和加工，晶圆表面活化，无氧化物直接键合，室温直接键合，具有真空下校准能力，无吸气剂高真空封装                                     | 工程基板，MEMS封装，“超越CMOS”器件，叠层太阳能电池，高性能逻辑器件，功率器件 |

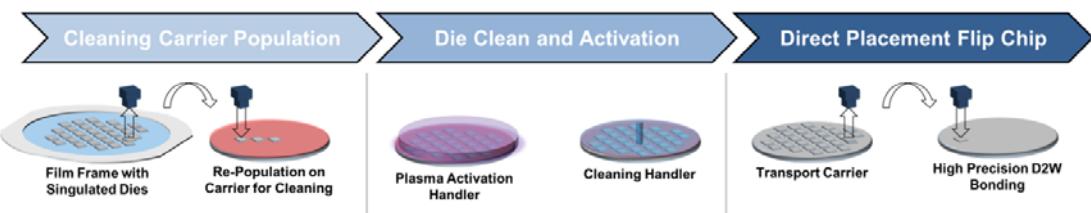

| 芯片到晶圆熔融与混合键合(Die-to-Wafer Fusion and Hybrid Bonding) | 1)Co-D2W:载体制备、载体填充、晶圆键合(临时和永久)和载体分离2)DP-D2W:载流子填充、芯片清洁和激活以及直接放置倒装芯片                     | 高带宽存储器，小芯片，3D堆叠式背面照明CMOS图像传感器               |

| 晶圆共晶键合(Eutectic Bonding)                             | 共晶温度远低于粘结过程中材料的熔化温度，对不规则表面、划痕和颗粒不太敏感，从而有利于大批量生产，有更好的脱气性和气密性                             | Al-Ge、Au-Sn和Au-In等MEMS器件，陀螺仪                |

| 熔融与混合键合(Fusion and Hybrid Bonding)                   | 在环境条件下的预键合，小于100nm的非常高的对准允许使用晶圆到晶圆熔合键合。铜焊盘可与介电层平行加工，允许在环境温度下预结合介电层，而在退火期间可通过金属扩散结合实现电接触 | CMOS图像传感器、存储器以及三维片上系统(SoC)                  |

| 金属扩散键合(Metal Diffusion Bonding)                      | 具有高扩散率的金、铝和铜是最稳定的材料，用于热压键合。与铝和铜相比，金需要较少的扩散温度，并且具有不被氧化的额外优势                              | RF-MEMS、发光二极管(led)、激光二极管以及功率器件              |

| 临时键合与解键合(Temporary Bonding and Debonding)            | 临时键合是为薄晶片或将超薄晶片提供机械支撑的一个重要过程                                                            | 超薄芯片和封装                                     |

| 瞬时液相键合(Transient Liquid Phase Bonding)               | 与共晶键合相比，液相键合界面通过扩散而不是冷却到熔点以下而凝固，形成具有快速扩散特性和高可靠性的组合物                                     | 高可靠性键合线或电气连接的场合                             |

资料来源：半导体材料与工艺，华安证券研究所整理

## 2.1 倒装回流焊

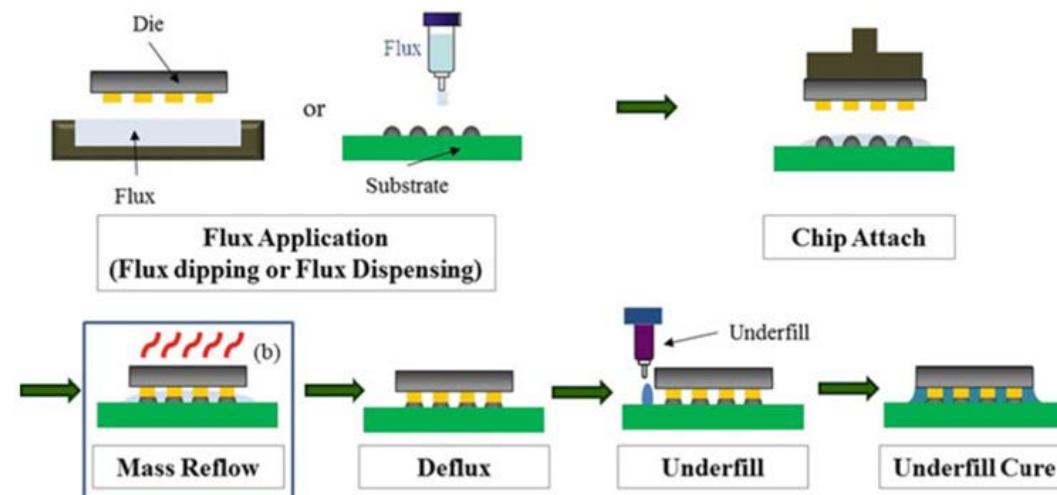

- 在先进封装工艺中，倒装芯片发展时间最长，较为成熟。倒装芯片起源于20世纪60年代，由IBM率先研发出来，是将芯片功能区朝下以倒扣的方式背对着基板，通过焊料凸点（简称Bump）与基板进行互联。基础的倒装芯片采用回流焊作为键合方案，此外，还有热压焊、超声焊和胶粘连接等方案。

- 由于倒装芯片焊接技术键合焊区的凸点电极不仅仅沿芯片四周边缘分布，且可以通过再布线实现面阵分布，因而与传统的引线键合技术相比，倒装芯片焊接技术具有如下优点：①尺寸小、薄，重量更轻；②密度更高，能增加单位面积内的I/O数量；③性能提高，短的互连减小了电感、电阻以及电容，信号完整性、频率特性更好；④散热能力提高，倒装芯片没有塑封体，芯片背面可用散热片等进行有效的冷却，使电路的可靠性得到提高；⑤生产效率高，降低了批量封装的成本。

倒装键合（Flip Chip Bonding）回流焊的工艺流程

资料来源：雪域资本、华安证券研究所整理

## 2.2 从倒装回流焊到TCB

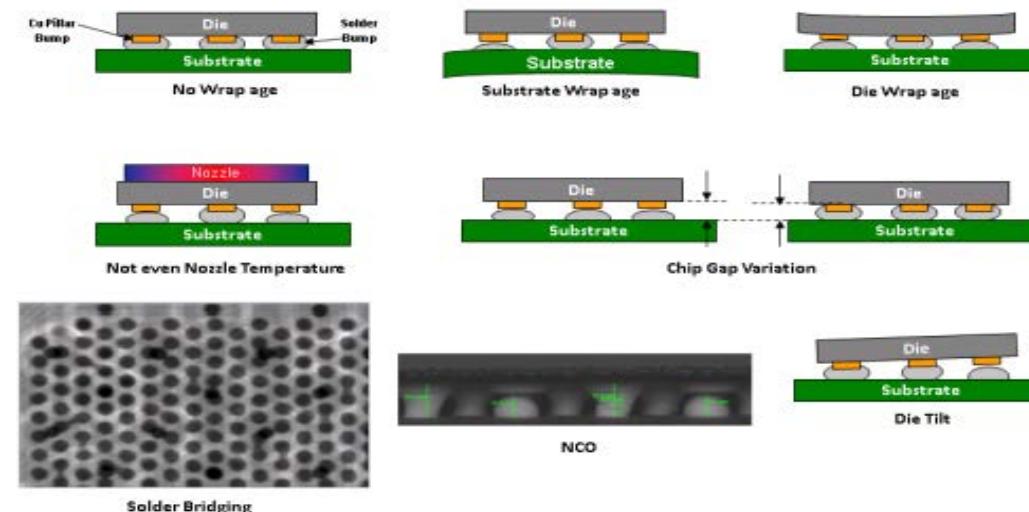

- 随着互连密度的增加和间距缩小到50μm以下，回流焊工艺缺陷率的提高，厂商开始寻求新的工艺和设备以解决回流焊的缺陷问题，TCB热压键合应运而生。

- ✓ 1) 根据所使用的回流锡膏的种类，回流温度的峰值一般控制在240°C到260°C。但是由于回流炉中加热会导致芯片、基板、焊球以不同的速率膨胀，从而发生翘曲导致芯片不能很好的被粘合，最后导致良率出现问题。由于Bump尺寸和间距的减小、超薄die的使用以及封装材料热膨胀系数的差异，回流焊工艺的缺陷率提高，回流焊过程中产生的翘曲、非接触性断开、局部桥接等缺陷增加。

- ✓ 2) 芯片的位置容易发生偏移：一是料盘/载具在传输过程中受震动影响，二是回流过程中芯片的自由偏移。焊接凸点间距(Pitch)越小，芯片尺寸越大，偏移失效越严重。

回流焊工艺造成的缺陷

资料来源：艾邦半导体网、华安证券研究所整理

## 2.3 TCB

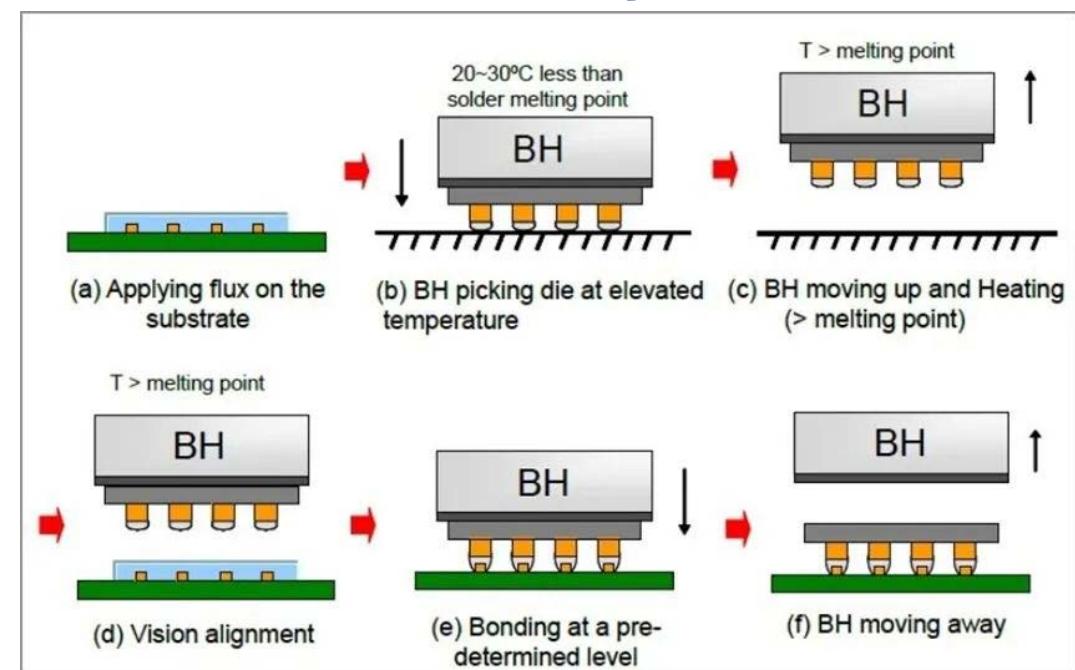

- 英特尔公司最早选择了基于基板(Substrate)的TCB(Thermal Compression Bonding热压键合)工艺以替代传统的回流焊,由英特尔和ASMPT公司联合开发,并于2014年导入量产。TCB典型的工艺温度范围在150°C-300°C之间,压力水平在10-200MPa之间。

- TCB的工艺流程: 1) 首先将喷涂了助焊剂(Flux)的基板固定在真空板上,这样基板将不会随着热发生翘曲形变; 2) 之后BH(贴片头)将捡起的晶片(Die)迅速加热到临界锡球融化温度; 3) 经过相机对位后, BH把晶片精准贴放到基板的凸点阵列区; 4) 在基板与晶片的凸点物理位置接触的一瞬间, BH从压力敏感控制转为位置敏感控制,并迅速加热到锡球融化温度以上保持数秒,之后BH迅速冷却,使得上下凸点之间的连接变为固相,焊接过程完成。

- TCB解决了标准倒装芯片的几个主要问题: 1) 热量从芯片顶部施加,因此只有芯片和C4焊料连接会升温,可以最大限度地减少基板翘曲问题。2) 这种键合方式确保均匀粘合,没有间隙变化或倾斜。3) 这种键合几乎没有空隙。4) 在相同的I/O间距下, TCB可实现更好的电气性能。TCB还允许I/O间距缩小到更小的尺寸,并可以封装更薄的die。

热压键合 (TCB Bonding) 工艺流程

资料来源: 雪域资本、华安证券研究所整理

## 2.4 从TCB到fluxless TCB

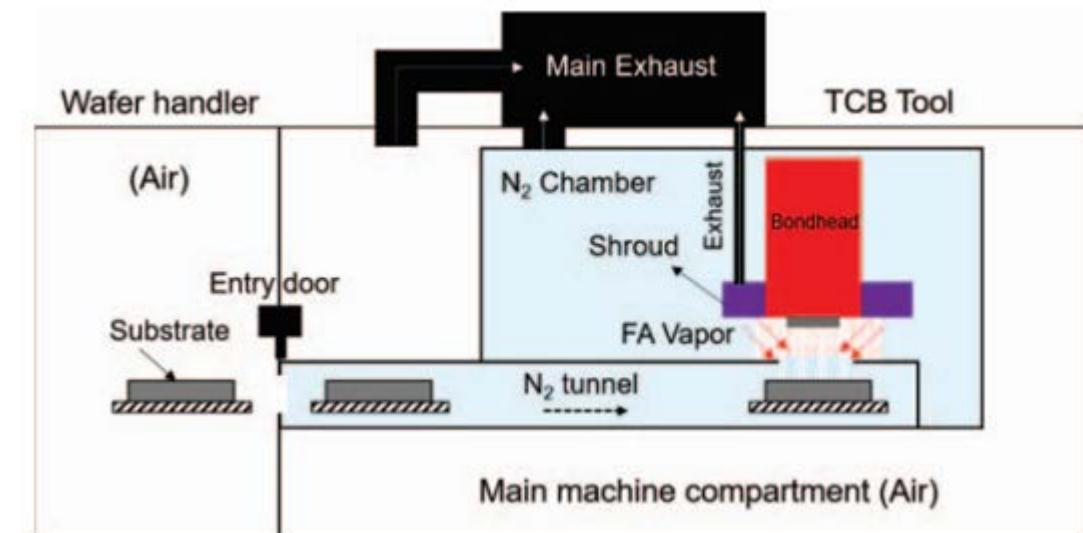

- 标准的TCB工艺需要使用助焊剂。在加热过程中，铜可能会氧化并导致互连故障，助焊剂是一种用于去除铜氧化物的涂层。但当互连间距缩小到 $10\mu\text{m}$ 以上时，助焊剂会变得很难清除，并会留下粘性残留物，这会导致互连发生微小变形，从而造成腐蚀和短路。

- 无助焊剂的TCB (fluxless TCB) 则最早由库力法索于2023年推出。没有助焊剂可提高互连的长期可靠性，因为它消除了可能导致芯片性能故障的污染风险，能够将键合间距缩小至 $10\mu\text{m}$ 。但它需要更严格的工艺控制，并且由于涉及额外步骤，吞吐量较低。

- 为了消除与助焊剂相关的挑战，无助焊剂TCB在真空或惰性气体环境（如氮气或氩气）中运行，以防止键合过程中发生氧化。流程为：1) 基板放在基座上进行预加热，在氮气保护的通道中被传送到键合头下方。2) 键合头将晶粒吸起，根据BUMP点进行对位，在升温的同时喷出甲酸气体将基板及晶粒上的BUMP氧化层去除，然后进行热压键合。

无助焊剂热压键合 (TCB Bonding) 示意图

资料来源：K&S、艾邦半导体网、华安证券研究所整理

## 2.5 混合键合——概念

- 在封装行业完成由引线键合转向倒装键合的范式转变后，先进封装的封装方法都使用某种带焊料的凸块作为硅与封装基板之间的互连。在微凸块方案中，每个芯片之间的间隔距离取决于微凸块的高度，但由于存在物理上的限制，这些技术只能将Bump之间的间距缩小到约10微米。

- 3D内存堆栈和异构集成需要极高的互连密度，与本身支持高密度互连方案的微凸块相比，采用无凸块互连的混合键合可提供更小尺寸的I/O端子和减小间距的互连。其尺寸超出了10微米互连间距，并且它不使用任何中介物，例如具有更高电阻的焊料。因此，混合键合互连方案可以显著降低整体封装厚度，在多芯片堆叠封装中可能减薄高达数百微米。

资料来源：半导体行业观察、TechSugar、华安证券研究所整理

## 2.5 混合键合——应用场景

- 20世纪80年代中期，混合键合技术（Hybird Bonding）的概念被提出，这是一种新型的键合技术，能够实现更精细的连接和更高的性能。这一技术最初被称为直接键合连接（Direct Bond Interconnect, DBI），并在2000年由Ziptronix公司进一步开发。

- 业界第一个Hybrid Bonding量产的产品是由Sony2015年在CMOS图像传感器的应用Cu-Cu直接键合。

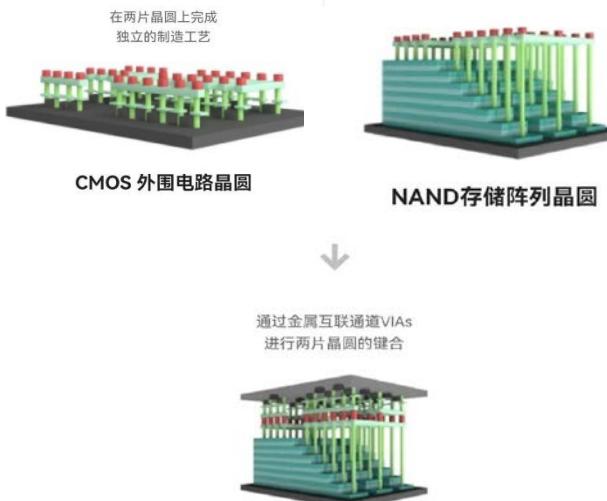

- 混合键合在3D NAND典型应用：长江存储的Xtacking®通过混合键合Memory和CMOS垂直互联。三星也于2025年与长存签署了堆叠400层NAND所需的混合键合技术的专利许可协议。

- 混合键合逐渐走向了逻辑、HBM等更多应用场景：AMD 3D V-Cache采用台积电SoIC-X技术，通过混合键合将缓存直接堆叠于CPU核心，显著提升系统性能；SK海力士和三星等计划利用混合键合实现HBM存储器更高层数堆叠，优化散热与带宽。

长江存储的Xtacking®

混合键合设备的细分应用

|                 | Backside Illuminated Image Sensor | Memory                 |                    |                 |                          | Logic            |                    |                         |

|-----------------|-----------------------------------|------------------------|--------------------|-----------------|--------------------------|------------------|--------------------|-------------------------|

|                 |                                   | 3D NAND Flash          | HBM Stacks         | DDR6+           | Next Gen. Memory         | SoC Partitioning |                    | Scaling                 |

| Device Stack    | Photo Diode + DRAM + Logic        | NAND Block + Periphery | 12+ layer stacking | Peri under DRAM | Peri on MRAM, FeRAM, PCM | SoIC             | SRAM + Logic       | Backside PDN (5nm node) |

| Bonding Process | W2W                               | W2W                    | W2W and/or D2W     | W2W             | W2W                      | W2W an/or D2W    | W2W                | W2W                     |

|                 | hybrid                            | hybrid                 | hybrid             | fusion          | fusion & hybrid          | hybrid           | hybrid             | fusion                  |

| Pitch           | 2μm → 1μm                         | 2μm → 1μm              | 5μm → 3μm          | 2μm → <1μm      | 2μm → <1μm               | 9μm → 2μm        | 2μm                | By scanner              |

| Maturity        | HVM                               | HVM                    | R&D                | R&D             | R&D                      | Ramp Up          | Ramp Up            | Ramp Up                 |

| Example         |                                   |                        |                    |                 |                          |                  |                    |                         |

|                 | Sony (System+)                    | YMTC (System+)         | Xperi (ECTC2020)   | IMEC (PTW21)    | IMEC (PTW21)             | TSMC WoW SoIC    | IMEC Collaboration | IMEC Collaboration      |

资料来源：EVG、半导体行业观察、艾邦半导体网、华安证券研究所整理

## 2.5 混合键合——市场空间

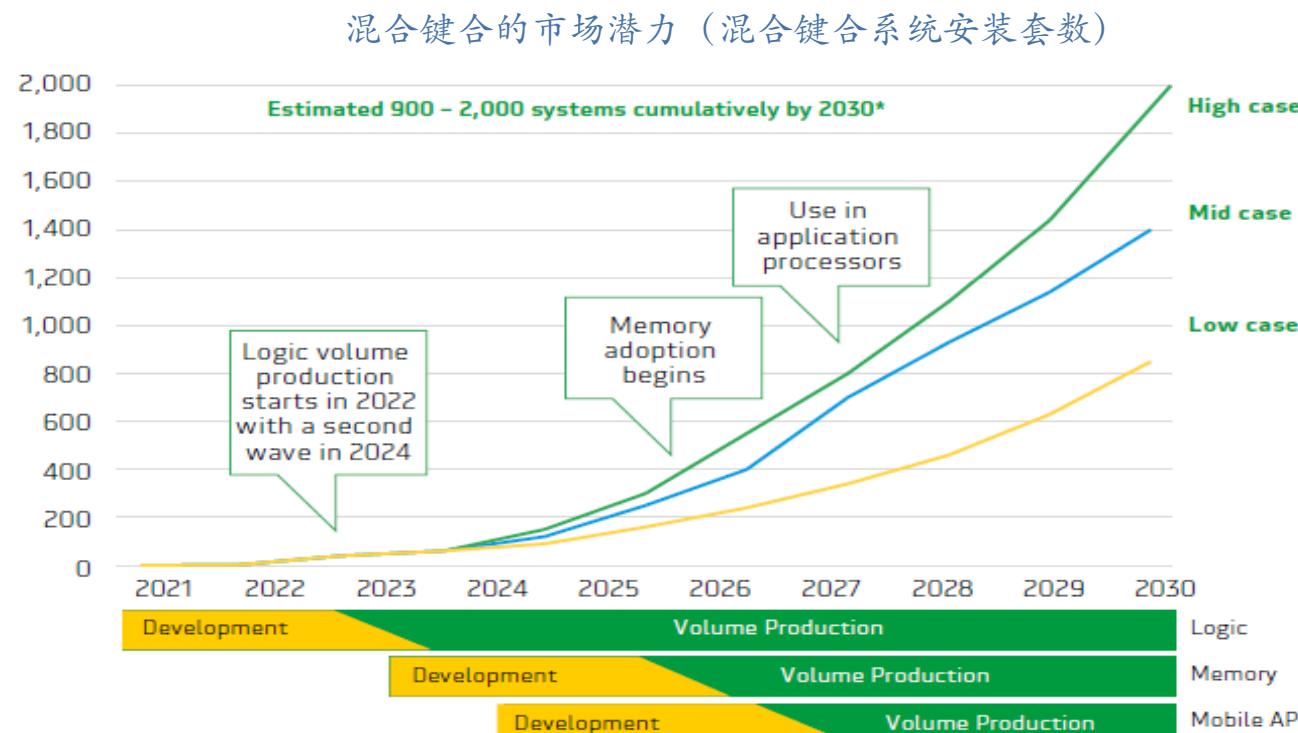

- 根据BESI，目前混合键合已成功用于数据中心和其他高性能计算应用的高端逻辑器件的商业化生产，随着IDM、代工厂和分包商越来越多地将该技术用于HBM4/5、ASIC逻辑设备、共封装光学和消费者移动/计算应用，预计混合键合在未来三年内将出现显著的增长。BESI预测2025-2026年将迎来混合键合在存储芯片的使用，到2030年混合键合市场（不包括共同包装的光学和复杂的CMOS传感器应用）中性预期将达到1,400套，由于混合键合设备的平均售价显著高于TCB键合系统，每台键合设备的成本在200万至250万欧元之间，我们测算对应2030年市场空间达到28亿至35亿欧元。

资料来源：BESI、华安证券研究所整理

## 2.5 混合键合——W2W 与 D2W

- 具体而言，混合键合可以通过三种方法来完成：一种是晶圆到晶圆（wafer-to-wafer: W2W）键合，这种方式更加成熟，但限制相同芯片尺寸的组合；另一种是芯片到晶圆（die-to-wafer: D2W）键合，它涉及更多的工艺步骤以及将芯片单独放置在载体晶圆或玻璃上（集体芯片到晶圆方法）；第三种芯片到晶圆（Chip-to-Wafer）键合正在研发中。其中，D2W又可以进一步分为集体晶粒到晶圆键合（Co-D2W）和直接贴装晶粒到晶圆（DP-D2W）。

- W2W和D2W由于不同的工艺流程导致两种工艺有各自的优缺点和不同的适用场景。W2W的优势在于更高的对准精度、吞吐量和键合良率；W2W的缺点主要在于无法执行晶圆分类来选择已知良好的芯片，同时顶部芯片和底部芯片的尺寸必须一致，因而限制了异构集成选项的灵活性。D2W的优势在于更加灵活；D2W的缺点主要在于难度较大、良率相对较低，因为每个晶圆有更多的键合步骤，这些额外的步骤会引入更多的颗粒污染，尤其是来自芯片分割和拾放期间键合头的移动的颗粒污染，并且额外的W2W键合步骤会产生更多的对准错误机会。

W2W和D2W的对比

| 工艺类型 | 优势                           | 缺点                                                       | 成本                    | 应用领域                                              | 代表设备厂商                                         |

|------|------------------------------|----------------------------------------------------------|-----------------------|---------------------------------------------------|------------------------------------------------|

| W2W  | ①对准精度更高<br>②吞吐量更大<br>③键合良率更高 | ①无法执行晶圆分类来选择已知良好的芯片<br>②顶部芯片和底部芯片的尺寸必须一致，因而限制了异构集成选项的灵活性 | 生产小尺寸芯片成本有优势，大尺寸芯片成本高 | 广泛应用于大众市场产品，如3DCMOS图像传感器、3DNAND、BowIPU等，未来可能用于HBM | 日本TEL、奥地利EVG、德国SUSS                            |

| D2W  | 更加灵活                         | ①步骤多，难度大<br>②污染和对准错误可能性更高，良率低                            | 大芯片生产成本优势，小芯片生产上更昂贵   | 在CIS和存储中已经有所应用，是未来混合键合的主要选择                       | 荷兰BESI、奥地利EVG、新加坡ASMPT、法国SET、日本Shibaura、德国SUSS |

资料来源：semi analysis、未来半导体、华安证券研究所整理

## 2.5 混合键合——W2W 与 D2W

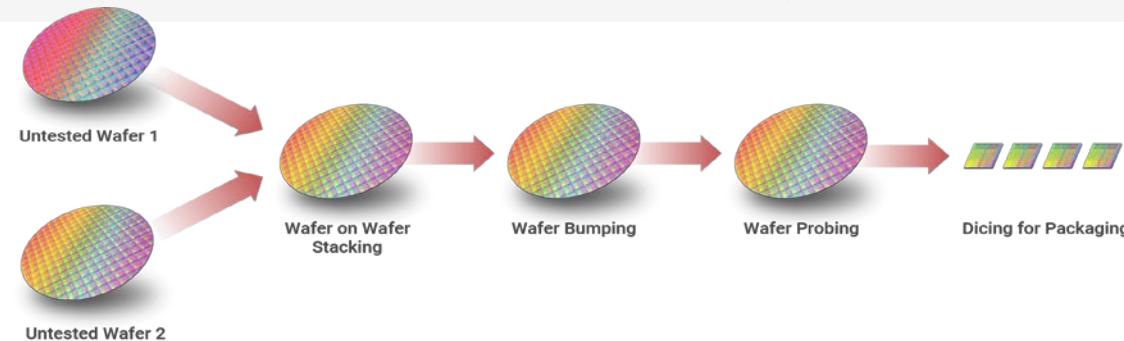

- **W2W键合工艺**是指将两片晶圆高精度对准、接合，实现两片晶圆之间功能模块集成的工艺。晶圆级键合设备可用于存储器堆叠、3D片上系统(SoC)、背照式CMOS图像传感器堆叠以及芯片分区等多个领域，是目前混合键合中能够进行大量生产的技术。

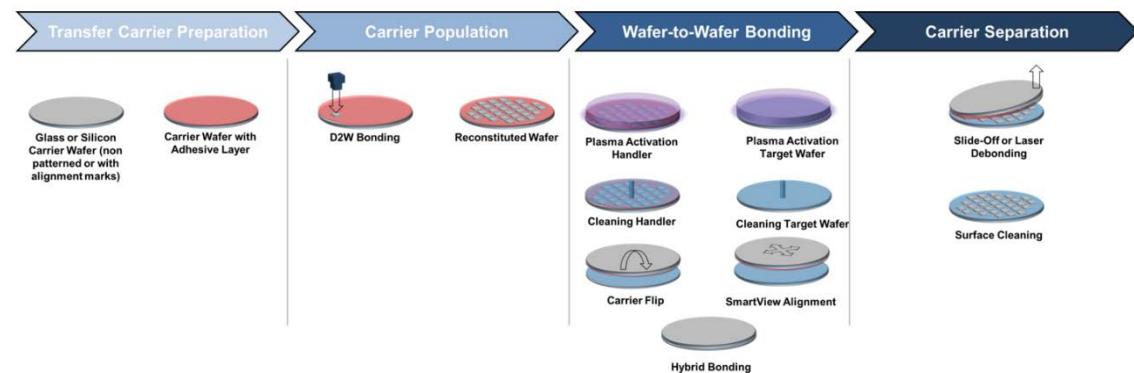

- 在**Co-D2W键合**中，多个芯片在单个工艺步骤中转移到最终晶圆上。Co-D2W键合工艺的制造流程包括载体准备、载体填充、晶片键合（临时和永久）和载体分离四大部分。过去几年中，Co-D2W在硅光通信等应用领域中进行了小批量量产。

- **DP-D2W键合**是另一种用于异质集成应用的混合晶粒到晶圆键合方法，使用拾取和放置倒装芯片键合机将芯片单独转移到最终的晶圆上。DP-D2W键合工艺的制造流程包括三个主要部分：载体填充、芯片清洁和激活、直接贴装倒装芯片。

资料来源：台积电、EVG、华安证券研究所整理

台积电SoIC W2W键合工艺流程

EVG Co-D2W键合工艺流程

EVG DP-D2W键合工艺流程

### 三、AI产业浪潮下的键合技术快速发展

## 3.1 HBM发展

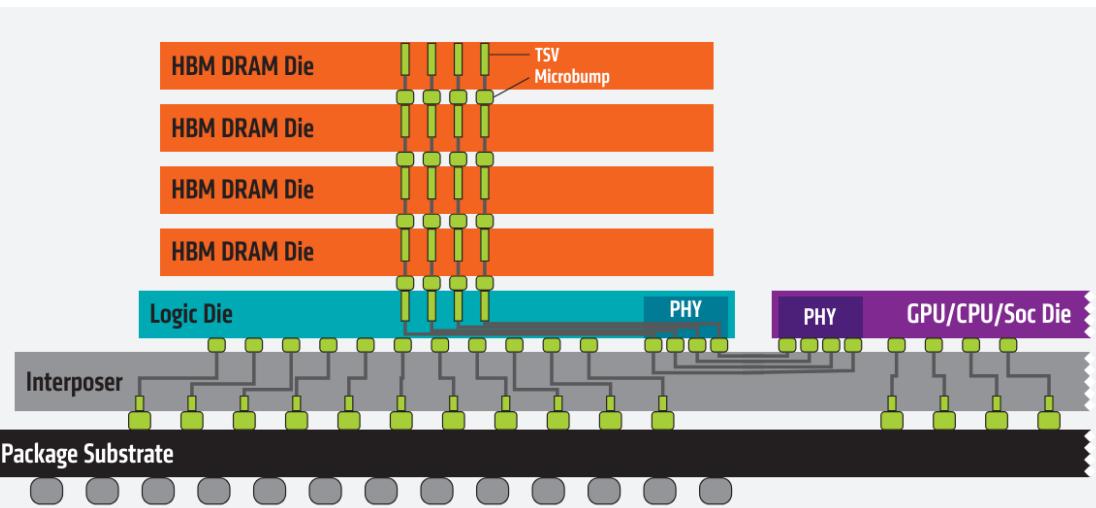

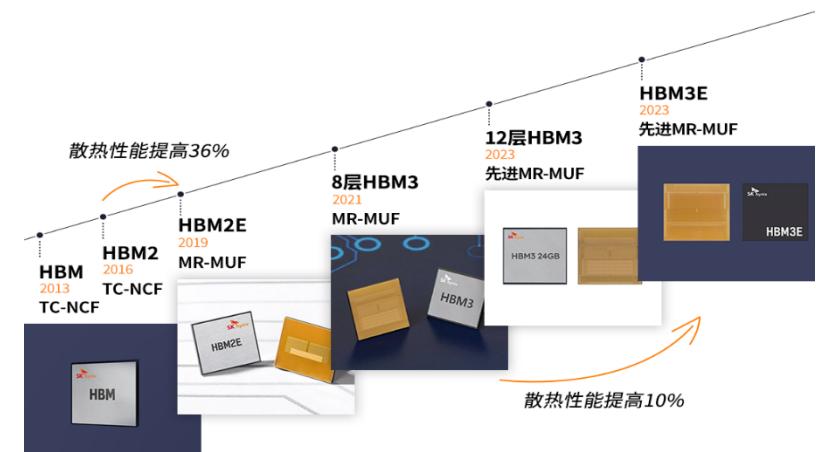

- 高带宽存储器（HBM）是一项先进的高性能技术，它通过使用硅通孔（TSV）垂直堆叠多个DRAM，可显著提升数据处理速度。这一突破性存储器解决方案采用了先进的封装方法，得益于这一封装工艺，HBM产品实现了更高容量，更大的存储带宽和更低的延迟，被广泛应用于高性能计算、数据中心等领域。

- 自2013年第一代HBM诞生以来，随着技术的不断发展，HBM也经历了HBM2（第二代）、HBM2E（第三代）、HBM3（第四代）、HBM3E（第五代）的顺序迭代，最新的HBM3E是HBM3的扩展版本。据韩媒报道，SK海力士的第6代12层HBM4测试良率已达70%。SK海力士于2025年3月19日宣布推出新产品12层HBM4，并且全球首次向主要客户提供了其样品。

HBM的结构

资料来源：AMD、华安证券研究所整理

HBM迭代产品参数演变

| 产品名称  | 时间   | 芯片密度     | 带宽<br>GB/s | 堆叠高度    | 容量       | I/O速率       | 内存接口  |

|-------|------|----------|------------|---------|----------|-------------|-------|

| HBM1  | 2014 | 2Gb      | 128 GB/s   | 4层      | 1GB      | 1Gbps       | 1024位 |

| HBM2  | 2018 | 8Gb      | 307 GB/s   | 4/8层    | 4/8/16GB | 2.4Gbps     | 1024位 |

| HBM2E | 2020 | 8Gb/16Gb | 460 GB/s   | 4/8层    | 8/16GB   | 3.6/3.2Gbps | 1024位 |

| HBM3  | 2022 | 16Gb     | 819 GB/s   | 8层/12层  | 16/24GB  | 6.4Gbps     | 1024位 |

| HBM3E | 2024 | 24Gb     | 1.2 TB/s   | 12层/16层 | 24/36GB  | 9.2Gbps     | 1024位 |

| HBM4  | 2026 | 48Gb     | 1.6/2 TB/s | 12层/16层 | 36/64GB  | /           | 2048位 |

资料来源：半导体行业联盟、华安证券研究所整理

## 3.2 HBM封装中组裝占成本15%

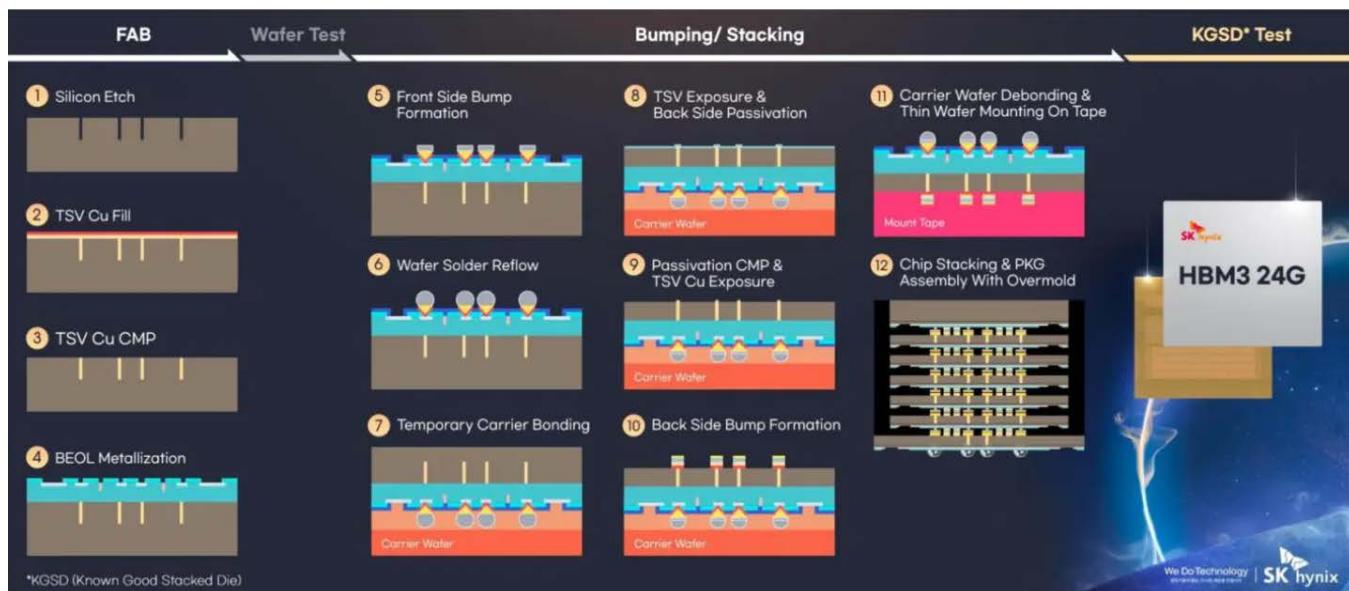

- HBM制造可以分为硅刻蚀、TSV铜填充、TSV铜化学机械抛光技术（CMP）、后端金属化、正面凸点形成、晶圆回流焊、临时载片键合、TSV曝光及背面钝化、钝化CMP及TSV铜曝光、背面凸点形成、晶圆载片脱粘及黏贴承载薄膜、堆叠芯片并通过二次成型工艺进行封装组裝共12道工序。

- HBM制造核心技术是TSV“连接”和封装“堆叠”。根据3D InCites，以4层DRAM存储芯片与一层逻辑芯片堆叠的HBM为例，在99.5%的封装良率下，组裝（采用TC-NCF法）在总成本中的占比为15%。

SK海力士的HBM工艺流程

资料来源：SK海力士、北京集成电路学会、华安证券研究所整理

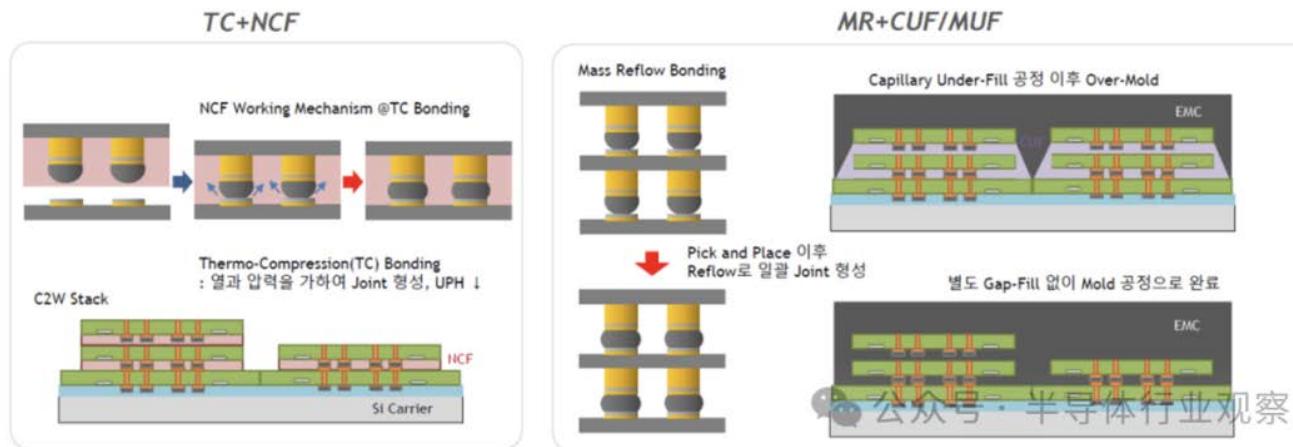

### 3.3 HBM的键合方式演变

- 在堆叠键合技术上，热压键合相对成熟，混合键合引领未来。

- ✓ HBM产品开发之初主要采用“TSV+Bumping”+TCB键合方式堆叠（TSV一般由晶圆厂完成，封测厂可在堆叠环节进行配套）。

- ✓ TC-NCF（热压非导电薄膜）是早期的主流工艺。但随着堆叠层数的增加，散热效率变差，SK海力士在HBM2E中率先引入MR-MUF（批量回流模压底部填充）技术，并在最新的HBM3E中率先使用改进的MR-MUF工艺，其HBM3E良率达到80%。三星和美光仍以TC-NCF技术为主。

- ✓ 在更高层数的HBM生产中三大厂商预期将使用混合键合。

SK海力士的HBM堆叠工艺路线

|                     |          | HBM3   |                 | HBM3e     |                 | HBM4            |      | HBM4e           |      | HBM5        |                |

|---------------------|----------|--------|-----------------|-----------|-----------------|-----------------|------|-----------------|------|-------------|----------------|

| Stacking            |          | 8hi    | 12hi            | 8hi       | 12hi            | 12hi            | 16hi | 12hi            | 16hi | 16hi        | >20hi          |

| NVIDIA AI GPU       |          | Hopper |                 | Blackwell |                 | Rubin           |      | TBD             |      | TBD         |                |

| NVIDIA CoWoS HBM    |          | 5      |                 | 8         |                 | 8/12            |      | TBD             |      | 3D stacking |                |

| Stacking Technology | SK hynix | MR-MUF | Advanced MR-MUF | MR-MUF    | Advanced MR-MUF | Advanced MR-MUF | TBD  | Advanced MR-MUF | TBD  | TBD         | Hybrid bonding |

|                     | Samsung  | TC-NCF |                 | TC-NCF    |                 | TC-NCF          | TBD  | TC-NCF          | TBD  | TBD         | Hybrid bonding |

|                     | Micron   | TC-NCF |                 | TC-NCF    |                 | TC-NCF          | TBD  | TC-NCF          | TBD  | TBD         | Hybrid bonding |

资料来源：SK海力士、华安证券研究所整理

## 3.4 MR-MUF VS TC-NCF

- TC-NCF（非导电胶膜）技术在各层DRAM之间嵌入NCF，并通过热压工艺（TC Bonding）从上至下施加热压，NCF在高温下融化，起到连接凸点并固定芯片的作用。MR-MUF技术在每次堆叠DRAM时，会先通过加热进行临时连接，最终在堆叠完成后进行回流焊以完成键合，随后填充环氧模塑料（EMC），使其均匀渗透到芯片间隙，起到支撑和防污染的作用。

- 根据SK海力士，与TC-NCF技术相比，MR-MUF技术能够同时对HBM产品中所有的垂直堆叠芯片进行加热和互联，且可将有效散热的热虚设凸块数量增加四倍，加上EMC卓越的机械性、电气绝缘性及耐热性，使得HBM2E的散热性能比上一代HBM2提高了36%，效率和性能均有提升。

- 在传统MR-MUF工艺中，通常使用助焊剂（Flux）去除微凸点上的氧化膜，随后进行清洗。然而，随着端口数量增加，堆叠层数增加，微凸点之间的间距缩小，导致助焊剂清洗不彻底，可能影响芯片的可靠性，无助焊剂TCB开始应用。从倒装键合到助焊剂TCB，封装I/O间距从200μm缩小到30μm，而无助焊剂TCB将进一步缩小间距尺寸至20μm，最大可达10μm，当I/O间距小于10μm时，就需要混合键合。

MR-MUF和TC-NCF 技术图示

资料来源：海力士、半导体行业观察、华安证券研究所整理

MR-MUF技术对IBM产品散热性能的影响

## 3.5 HBM带来TCB键合设备快速增长

- 根据Trend Force数据预测，2024年HBM需求位年增长率近200%，2025年有望再翻倍。SK海力士与美光曾公开表示，两家2024年的HBM已经售罄，就连2025年的HBM产量也几乎被预订一空。随着HBM和3D封装的商业化，TC键合机市场正在快速增长。HBM厂商的迅速扩产带来了近年来键合设备厂商的订单和收入持续增长。海力士在HBM的份额稳居第一，带来其主要供应商韩美半导体的收入大幅增长。

| HBM厂商 | 2023年底HBM /TSV产能 | 2024年底HBM /TSV产能   | 供应商                   | 采购订单                                                          | 订单时间    |

|-------|------------------|--------------------|-----------------------|---------------------------------------------------------------|---------|

| 海力士   | 45,000片/月        | 120,000-125,000片/月 | 韩美半导体                 | 12层HBM3E(第五代)产品的TC键合机108亿韩元 (5432万元人民币)                       | 2025.01 |

|       |                  |                    |                       | 签署了价值1500亿韩元的TC键合设备供应合同，累计金额已达3587亿韩元                         | 2024.06 |

|       |                  |                    |                       | 第三代HBM工艺设备，型号为DUAL TC BONDER GRIFFIN214.83亿韩元，累计订单金额超过2000亿韩元 | 2024.03 |

|       |                  |                    | 韩华精密机械                | 向SK海力士供应两台TC键合机                                               |         |

|       |                  |                    | ASMPT                 | 订购30多台TC键合设备                                                  | 2024.10 |

| 美光    | 3,000片/月         | 20,000片/月          | 日本新川公司 (Shinkawa) 、东丽 |                                                               |         |

|       |                  |                    | 韩美半导体                 | 价值226亿韩元的TC Bonder采购订单                                        | 2024.4  |

|       |                  |                    | ASMPT                 | 提供了用于hbm生产的TC 键合机。双方已开始联合开发下一代键合机。                            | 2024.6  |

| 三星    | 45,000片/月        | 130,000片/月         | 三星电子旗下子公司SEMES        | SEMES在一年内出货了100台TC键合设备                                        | 2024    |

|       |                  |                    | 日本新川公司 (Shinkawa)     | 订购了16台2.5D键合设备                                                | 2023.12 |

资料来源：半导体行业观察、ASMPT、trendforce、韩美半导体、华安证券研究所整理

## 3.6 HBM技术升级驱动混合键合应用

- 三大HBM厂已确定将在HBM3e 12hi及HBM4 12hi世代延续使用Advanced MR-MUF及TC-NCF堆叠架构，并已确定将在HBM5 20hi世代中使用Hybrid Bonding技术，对于是否于HBM4 16hi采用还在考虑中，海力士表示16层HBM4/HBM4E将同步采用先进MR-MUF和混合键合(Hybrid Bonding)两种技术。

- 对于高世代HBM的堆叠高度限制，芯片厚度和间隔受限；I/O数量增长，密度变大；散热要求提升等要求，混合键合技术(Hybrid Bonding)优势在于：1)大幅缩小电极尺寸，从而增加单位面积上的I/O数量，进而大幅降低功耗；2)显著缩小芯片之间的间隙，由此实现大容量封装；3)可以改善芯片散热性能，降低芯片厚度，有效地解决因耗电量增加而引起的散热问题。

- 采用Hybrid Bonding需面对多项挑战：1)原厂投资新设备导入新的堆叠技术，将排挤对Micro Bump的需求，也不再享有原本累积的技术优势。2) Hybrid Bonding尚有微粒控制等技术问题待克服，将提升单位投资金额。3)若Hybrid Bonding需以Wafer to Wafer模式堆叠，若前端生产良率过低，整体生产良率将不具经济效益。

资料来源：Trend Force、YOLE、华安证券研究所整理

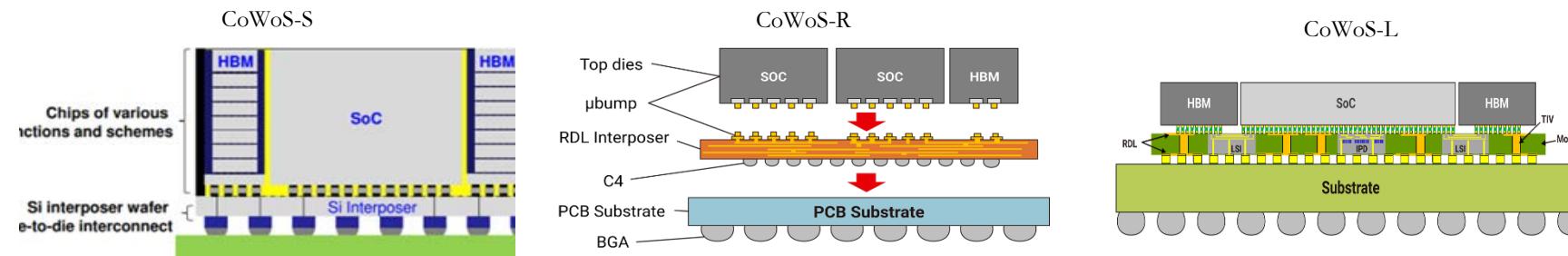

## 3.7 CoWoS带来的TCB键合设备增长

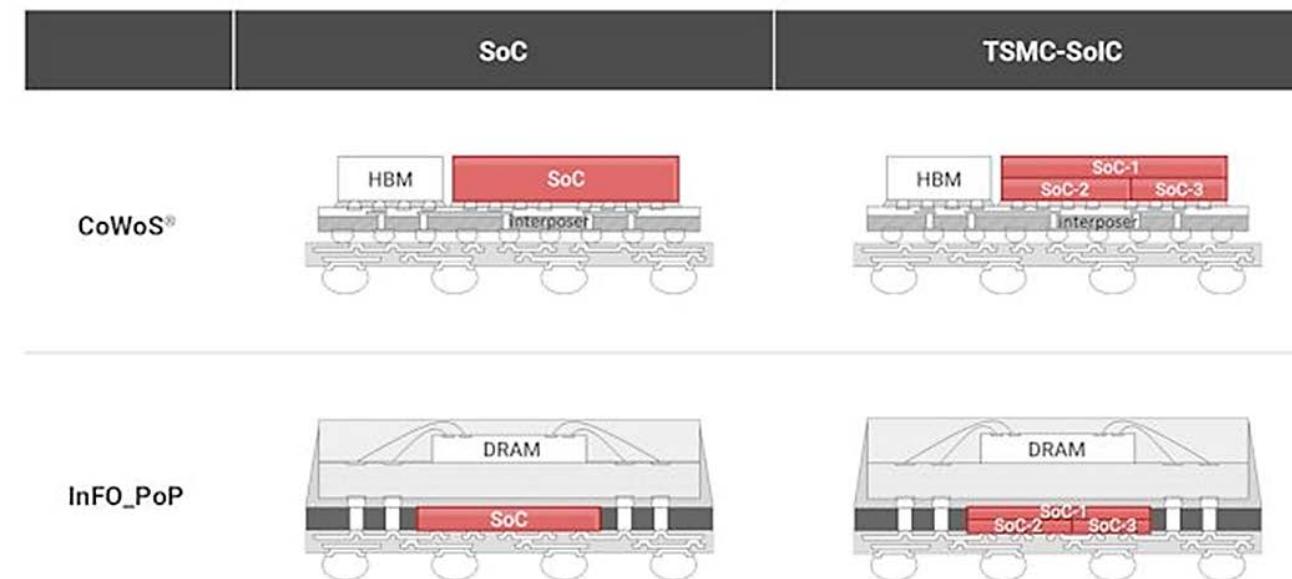

- 在HBM与CPU/GPU逻辑芯片共封装时，CoWoS是主流工艺。由于HBM需要高密度焊盘和短距离连接，这种要求需要通过2.5D封装技术，例如CoWoS来实现，而无法在常规的PCB或封装基板上实现。CoWoS以相对合理的成本提供了最高的互连密度和最大的封装尺寸。目前，大部分的HBM系统都采用CoWoS封装。

- CoWoS是台积电的一种2.5D封装技术，其中多个有源硅芯片被整合到无源硅中介层上，然后将中介层和有源硅连接到包含I/O接口的封装基板上，最终用于PCB上。根据ASMPT，其在芯片到基底(C2S)应用的领先晶圆代工客户及OSAT伙伴获得了可观的TCB订单，作为该客户应用于芯片到基底的TCB工具的唯一供应商。公司2024年新增半导体设备订单同比增长36.7%，达9.36亿美元。

CoWoS的三种类型

资料来源：台积电、华安证券研究所整理

## 3.8 SoIC带来的混合键合设备增长

- 台积电的3D堆叠系统级集成芯片(SoIC)先进封装技术主要客户包括苹果、AMD、AWS和高通等，SoIC-X(无凸块)目前用于特定应用，例如AMD的CPU 3D V缓存技术，以及Instinct MI300系列AI产品。

- SoIC技术基于台积电对混合晶圆键合的实现，混合键合允许将两个先进的逻辑器件直接堆叠在一起，从而实现两个芯片之间的超密集(和超短)连接，主要针对高性能部件。

- 据bits-chips，2023年台积电与Besi及其合作伙伴应用材料签订了一大笔混合键合生产线订单。根据BESI，2023年公司收到2.5D/3D订单；2024年，公司混合键合收入、订单和采用量显著增加，订单增加了一倍以上，且确认了第二个领先的逻辑客户。

SoIC示意图

资料来源：现代电子技术、BESI、华安证券研究所整理

## 3.9 AI服务器驱动的键合设备空间测算

- AI的快速发展带动HBM和CoWoS厂商的快速扩产，进而带来键合设备的广阔空间。我们测算全球AI服务器拉动的HBM需求量对应的bonding设备市场空间从2023年的70.7亿元增长至2025年的143.1亿元，全球CoWoS需求量对应的bonding设备市场空间从2023年的7.1亿元增长至2025年的12.9亿元。我国AI服务器拉动的HBM需求量对应的bonding设备市场空间从2023年的21.2亿元增长至2025年的32.4亿元，我国CoWoS需求量对应的bonding设备市场空间从2023年的2.1亿元增长至2025年的2.9亿元。

- 假设如下：1) 单AI服务器假设搭载8颗GPU，对应HBM数量保守假设维持在6颗；2) HBM堆叠层数保守假设8层，12寸晶圆切割dram数量假设为490颗；3) 根据睿力集成的项目投资书测算HBM万片/月的投资额57亿元；4) 假设单片CoWoS封装39颗GPU；5) 根据甬矽电子募集说明书测算CoWoS万片键合设备投资额3.5亿元；6) 根据BESI数据，以23%的键合设备价值量测算键合设备空间。

| 全球市场                           | 2023年       | 2024年        | 2025年        |

|--------------------------------|-------------|--------------|--------------|

| 全球AI服务器出货量 (万台)                | 118         | 172.28       | 215.35       |

| AI服务器装载GPU数量                   | 8           | 8            | 8            |

| 单GPU对应HBM数量                    | 6           | 6            | 6            |

| HBM需求量 (万颗)                    | 5,664.0     | 8,269.4      | 10,336.8     |

| HBM堆叠层数                        | 8           | 8            | 8            |

| 单晶圆切割DRAM数量                    | 490         | 490          | 490          |

| HBM数量对应万片/月                    | 7.7         | 12.5         | 15.6         |

| 万片HBM封装投资额 (亿元)                | 57          | 57           | 57           |

| 万片HBM封装bonding设备投资额            | 9.177       | 9.177        | 9.177        |

| <b>HBM对应bonding设备市场空间 (亿元)</b> | <b>70.7</b> | <b>114.5</b> | <b>143.1</b> |

| 1片CoWoS封装GPU数量                 | 39          | 39           | 39           |

| CoWoS对应万片/月                    | 2.0         | 2.9          | 3.7          |

| 万片CoWoS对应bonding设备投资额          | 3.5         | 3.5          | 3.5          |

| <b>CoWoS对应bonding市场空间 (亿元)</b> | <b>7.1</b>  | <b>10.3</b>  | <b>12.9</b>  |

| 我国市场                           | 2023年       | 2024年       | 2025年       |

|--------------------------------|-------------|-------------|-------------|

| 中国AI服务器出货量                     | 35.4        | 42.1        | 48.8        |

| AI服务器装载GPU数量                   | 8           | 8           | 8           |

| 单GPU对应HBM数量                    | 6           | 6           | 6           |

| HBM需求量 (万颗)                    | 1,699.2     | 2,020.8     | 2,342.4     |

| HBM堆叠层数                        | 8           | 8           | 8           |

| 单晶圆切割DRAM数量                    | 490         | 490         | 490         |

| HBM数量对应万片/月                    | 2.3         | 3.0         | 3.5         |

| 万片HBM封装投资额 (亿元)                | 57          | 57          | 57          |

| 万片HBM封装bonding设备投资额            | 9.177       | 9.177       | 9.177       |

| <b>HBM对应bonding设备市场空间 (亿元)</b> | <b>21.2</b> | <b>28.0</b> | <b>32.4</b> |

| 1片CoWoS封装GPU数量                 | 39          | 39          | 39          |

| CoWoS对应万片/月                    | 0.6         | 0.7         | 0.8         |

| 万片CoWoS对应bonding设备投资额          | 3.5         | 3.5         | 3.5         |

| <b>CoWoS对应bonding市场空间 (亿元)</b> | <b>2.1</b>  | <b>2.5</b>  | <b>2.9</b>  |

资料来源：中商产业研究院、trendforce、国际电子商情、甬矽电子、BESI、腾讯科技、华安证券研究所整理

## 3.10 国内先进封装产业发展带来国产设备机遇

- 2024年12月，美国商务部工业和安全局（BIS）修订了《出口管理条例》（EAR），新的出口限制包括限制向中国出口先进高带宽存储器（HBM）。根据新的 3A090.c，IFR将管制“Memory bandwidth density” 大于2GB/s/mm<sup>2</sup>的HBM。当前生产的所有HBM都超过了此阈值。即对于目前几乎所有现行生产的HBM，均不能出口到中国。

- 国内厂商正加快HBM、2.5D/3D封装的突破与产能建设，高端先进封装整体仍处于产业化发展的前期。产业的国产化突破，为国产关键设备厂商提供了有利机遇，将有望迎来自身产品突破+下游产业放量的双重机遇。

| 公司   | 先进封装进展                                                                                                                                                      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 武汉新芯 | 2024年发布了《高带宽存储芯粒先进封装技术研发和产线建设》招标项目，将利用三维集成多晶圆堆叠技术，打造更高容量、更大带宽、更小功耗和更高生产效率的国产高带宽存储器(HBM)产品。拟新增设备16台套，拟实现月产出能力>3000片(12英寸)。                                   |

| 芯浦天英 | 2024年6月，计划投资至少171亿人民币建造一座先进封装厂，新工厂位于浦东，预估将于2026年中投产。该新厂将专注于各种先进封装技术，如用硅穿孔（TSV）互联实现内存堆栈，制造应用在人工智能（AI）的高频宽存储器。该工厂预估封装产能达3万片/月。                                |

| 盛合晶微 | 三维多芯片集成封装项目总投资100.9亿元，建成后将形成月产8万片金属Bump(凸块工艺)产品及1.6万片三维多芯片集成封装产品加工的生产能力。另外，其超高密度互联多芯片集成封装暨J2C厂房项目建成后，将新增洁净室面积3万平方米，有力地支撑公司的三维多芯片集成加工和超高密度互联三维多芯片集成封装等项目的发展。 |

| 甬矽电子 | 2025年1月该公司发布公告，拟发行可转债募集资金不超过12亿元，用于多维异构先进封装技术研发及产业化项目等，完全达产后将形成封测Fan-out系列和2.5D/3D系列等多维异构先进封装产品9万片/年的生产能力。                                                  |

资料来源：半导体行业联盟、国际电子商情讯、全球半导体观察、华安证券研究所整理

## 四、设备厂商和投资标的梳理

## 4.1 键合设备的竞争格局

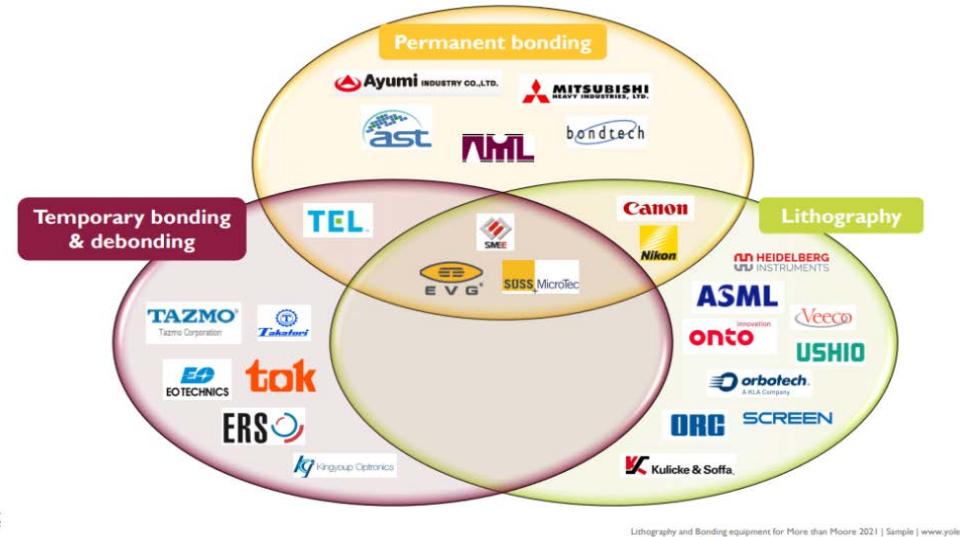

- 晶圆键合设备领域主要由国际巨头主导。根据 QY Research 头部企业研究中心调研，全球范围内晶圆键合设备生产商主要包括EV Group、SUSS MicroTec、Tokyo Electron、Applied Microengineering、Nidec Machine Tool, Ayumi Industry、Bond tech.、Aimechatec、U-Precision Tech、TAZMO等。2023年，全球前五大厂商占有大约86.0%的市场份额。先进封装产业在我国快速增长，先进封装设备国产化率仍低，HBM产业链在关键设备端国产化率不足5%。

永久键合、临时键合和解键合、光刻领域主要设备厂商

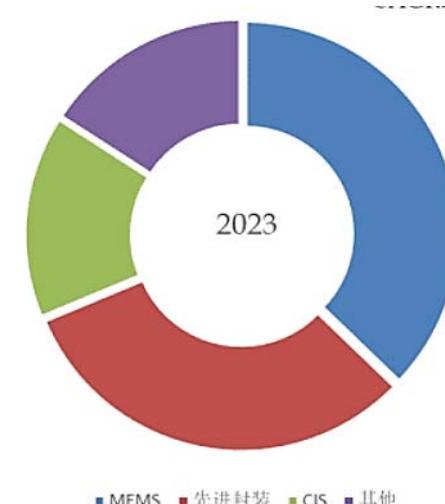

2023年键合设备市场需求组成

资料来源：YOLE、华安证券研究所整理

资料来源：QY Research、华安证券研究所整理

## 4.2 晶圆键合设备的主要供应商梳理

- 随着AI驱动下先进封装的快速放量，以韩美半导体为代表的TC Bonding设备厂商，以Besi为代表的Hybrid Bonding设备厂商，都获得了快速的增长。国内键合设备以进口为主，特别是先进封装键合设备，国内设备厂商也在加快键合设备的研发和推进，国产替代叠加行业下游突破，有望带来共振的发展机遇。

| 设备商      | 国家   | 设备进展                                                                                                                               |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------|

| K&S      | 美国   | 全球半导体封测设备的头部厂商之一，从半导体贴片机和焊线机起步，逐步通过战略性收购和自主研发，逐步增加了先进封装键合机、电子装配、楔焊机等产品，同时配合其核心产品进一步扩大了耗材的产品范围。                                     |

| Besi     | 荷兰   | 全球先进封装领域固晶/键合机龙头，混合键合机8800运用混合键合技术，精准度可以到达0.2微米以上，产能效率在1500UPH左右。                                                                  |

| ASMPT    | 新加坡  | 混合键合机包括LITHOBOLT系列，主要支持D2W混合键合工艺。                                                                                                  |

| SUSS     | 德国   | 晶圆键合系统主要包括XB8、8B6/8Gen2XBS200、XBS300XBC300 Gen2等系统，最大晶圆尺寸304.8 mm(12英寸)，对准精度能够满足包≤500 m，括共晶、直接键合等各种晶圆键合工艺需求。                       |

| EV Group | 奥地利  | 目前先进封装领域纳米技术晶圆级键合及光刻技术领域公认的技术引领者，EVG公司提供的键合机品种多样，包括适合阳极键合、共晶键合金属扩散键合、直接键合、聚合物键合、熔融与混合键合和瞬时液相键合的小批量、半自动晶圆键合解决方案。                    |

| HANMI    | 韩国   | HBM用TC Bonder获得美光、海力士等重复订单。                                                                                                        |

| 拓荆科技     | 中国大陆 | 混合键合W2W设备及D2W键合表面预处理设备均已获得重复订单，键合套准精度量测产品也已出货。                                                                                     |

| 芯慧联      | 中国大陆 | 2024年11月6日，芯慧联芯首台D2W混合键合设备SIRIUS RT300及首台W2W混合键合设备CANOPUS RT300顺利出货。                                                               |

| 华卓清科     | 中国大陆 | 面向HBM芯片制造的核心环节，自主研发出多款系列高端装备，包括：混合键合设备(UP-UMA®HB300)、熔融键合设备(UP-UMA®FB300)、芯粒键合设备(UP-D2W-HB)、激光剥离设备(UP-LLR-300)、激光退火设备(UP-DLA-300)。 |

| 快克智能     | 中国大陆 | 公司面向先进封装的TCB键合设备正按照既定目标推进中，预计2025年二季度完成样机研发。                                                                                       |

| 芯源微      | 中国大陆 | 公司提前布局自主研发的全自动临时键合及解键合机，主要针对 Chiplet 技术解决方案，可应用于 InFO、CoWoS、HBM 等 2.5D、3D 技术路线产品，获得了多家大客户订单。                                       |

| 芯碁微装     | 中国大陆 | 公司键合设备能够实现热压键合，目前支持的最大晶圆尺寸为8英寸，采用半自动化操作，可运用于先进封装、MEMS等多种场景用。                                                                       |

| 迈为股份     | 中国大陆 | 公司成功开发出全自动晶圆临时键合机、全自动混合键合机等多款新产品。                                                                                                  |

资料来源：半导体产业研究、WIND、半导体行业观察、拓荆科技公告、芯源微公告、芯语、芯慧联公众号、快克智能互动易、华安证券研究所整理

## 4.3 海外相关投资标的复盘——1) 韩美半导体Hanmi

- **韩美半导体 (Hanmi Semiconductor)** 成立于1980年，初期生产芯片载体模具与封装注塑等塑封设备。2017年开始与SK海力士共同研发用于HBM封装及2.5D封装的Dual TC Bonder。2017年公司与SK海力士共同开发了TC键合机，为SK海力士的MR-MUF工艺提供设备。2023年公司发布新一代Dual TC Bonder超级型号GRIFFIN和高级型号DRAGON，两者皆采用TSV方法制造的半导体芯片堆叠在晶圆上的双机台键合设备，可用于当前HBM用TC的两种主要解决方案TC+NCF与TC+MUF。同时推出的TC Bonder CW适用于台积电CoWoS工艺。

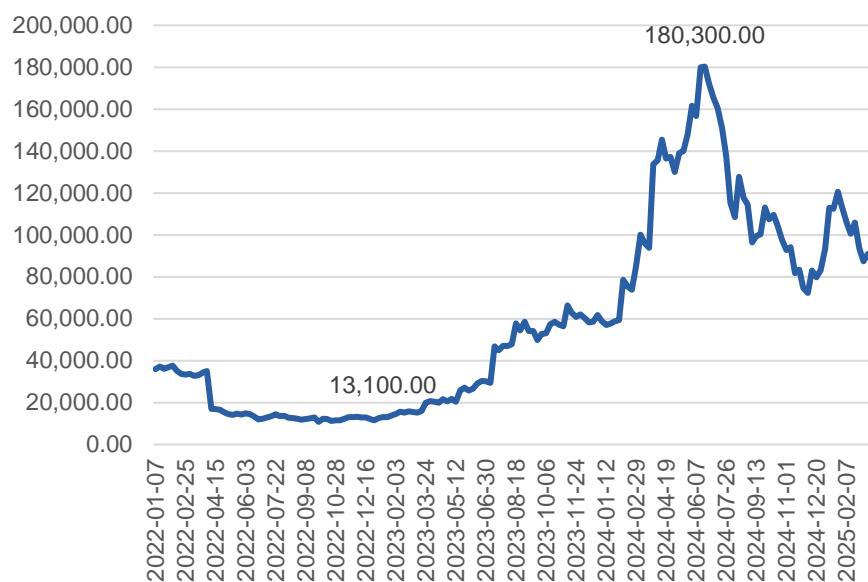

- **订单、收入和股价的上涨：**从2023年初到2024年6月，公司股价上涨超过1300%，这一时期，HBM供不应求进入扩产期，带动公司收入和订单高增。截至2024年6月，公司从SK海力士获得的HBM TC键合机订单累计金额达3587亿韩元，一台TC键合机价格约20亿韩元，也获得美光的订单。以1: 200的汇率计算，公司的营业收入也从2023年的8亿元增长到2024年的28亿元，并提出2025年60万亿元的销售目标。

公司股价收盘价 (前复权) (韩元)

公司键合类产品

| 分类                | 产品情况                                                                                                                                                                                               |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TC BONDER         | HBM等生产时所需的Thermal Compression粘合设备<br>(世界上第一个DUALBonding方式，与SK海力士共同开发)<br>- Dual TC Bonder DRAGON<br>- Dual TC Bonder GRIFFIN<br>- Dual TC Bonder TIGER<br>- TC Bonder 3.0 CS<br>- TC Bonder 3.0 CW |

| 6-SIDE INSPECTION | 对单个HBM芯片(Die)及键合后的HBM芯片进行视觉检查，将缺陷率降至最低，是TC BONDING前后工程的必备设备，可提高HBM产量和生产率，检查精度大幅提高，有望成为未来销售贡献的主力设备。                                                                                                 |

| FLIP CHIP BONDER  | 配备双拾取器(Dual Picker)和双贴合器(Dual Bonder)的Flip-Chip Packaging用键合设备                                                                                                                                     |

资料来源：Hanmi、WIND、华安证券研究所整理

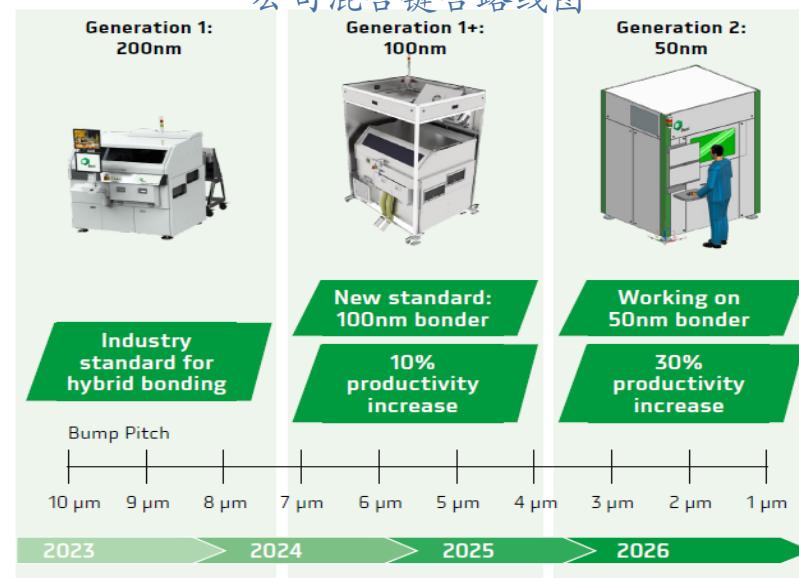

## 4.3 海外相关投资标的复盘——2) BESI

- BE Semiconductor Industries N.V.为半导体和电子行业高级封装解决方案的开发、制造、营销、销售和服务，公司2024年81%的收入来自于晶圆键合事业部，50%的订单来自于AI相关封装。2024年公司混合键合收入同比增长2倍，订单增加1倍以上，下游客户从9个增加到15个，并且确认了第二个领先的逻辑客户。

- 2021年至2024年，公司累计混合键合订单已经超过100套，2024年首批100nm精确度的混合键合设备出货，并计划在2025年底实现50nm精确度的混合键合设备。公司无助焊剂的TCB设备已经有2台出货。混合键合在高端逻辑器件的商业化生产带来公司的收入和订单持续增长，HBM4/5、ASIC逻辑等将带来新的增量。

- 据公司首席执行官布里克曼表示，八年前台积电要求Besi开始为其技术开发键合机。自2020年10月以来，Besi和Applied公司通过在新加坡建立卓越中心(CoE)来进行技术开发。2021年，在COVID危机期间的半导体热潮中，Besi宣布，英特尔和台积电都承诺购买50台混合键合，订单真正开始增长是在2023年。公司股价在21年增长横盘后，于22年底开始上涨，到24年3月涨幅超190%。

资料来源：BESI、WIND、华安证券研究所整理

## 4.4 国内相关投资标的——1) 拓荆科技

- 公司作为国内高端半导体设备领域的领军企业，继续专注于薄膜沉积设备和混合键合设备的自主研发与产业化。PECVD、ALD、SACVD、HDPCVD、Flowable CVD 及混合键合设备等系列产品量产规模不断扩大。2024年公司实现营业收入410,345.39万元，同比增长51.70%；归属于母公司所有者的净利润68,845.83万元，同比增长3.91%。2023年混合键合设备首年实现营收0.64亿元，毛利率50.84%，成为新的增长点。

- 公司推出了应用于晶圆级三维集成领域的混合键合（Hybrid Bonding）设备产品系列，该设备还能兼容熔融键合（Fusion Bonding）。混合键合系列产品还包括芯片对晶圆键合表面预处理（Die to Wafer Bonding Preparation and Activation）产品以及键合套准精度量测产品（Bonding Metrology）。

- 2023年公司首台晶圆对晶圆键合产品Dione300顺利通过客户验证，并获得复购订单，实现了产业化应用，成为国产首台应用于量产的混合键合设备，目前该设备的性能和产能已达国际领先水平。根据公司2024年半年报，公司推出的芯片对晶圆混合键合前表面预处理产品已经获得客户重复订单；公司新推出的键合套准精度量测产品 Crux300 也获得了客户订单。

### 相关产品介绍

| 分类         | 产品型号      | 产品图片 | 产品应用情况                                                |

|------------|-----------|------|-------------------------------------------------------|

| W2W键合      | Dione 300 |      | 主要应用于晶圆级三维集成、存储芯片制造领域，已实现产业化应用，可实现12寸晶圆对晶圆的混合键合和熔融键合。 |

| D2W键合表面预处理 | Propus    |      | 主要应用于芯片对晶圆三维集成领域，已实现产业化应用，可实现混合键合前晶圆及切割后芯片的表面活化与清洗。   |

| 键合套准精度量测   | Crux 300  |      | 主要应用于晶圆级三维集成领域，可实现晶圆对晶圆混合键合和芯片对晶圆混合键合后的键合精度量测。        |

资料来源：公司公告、华安证券研究所整理

## 4.4 国内相关投资标的——2) 百傲化学

百傲化学是国内精细化工领域的龙头企业，主营业务为异噻唑啉酮类工业杀菌剂原药剂的研发、生产和销售。公司2024年2月与苏州芯慧联半导体科技有限公司签订了《战略合作协议》和《半导体设备业务合作协议》。公司将与苏州芯慧联合作开展包括但不限于以下先进半导体设备的技术创新及研发迭代：全球领先的涂胶显影设备、先进高端型湿法电镀设备、创新自主研发的半导体自动化设备、高技术壁垒的晶圆键合设备、尖端的湿法清洗设备等。

根据芯慧联公众号，2024年11月6日，芯慧联首台D2W混合键合设备**SIRIUS RT300**及首台W2W混合键合设备**CANOPUS RT300**顺利出货。

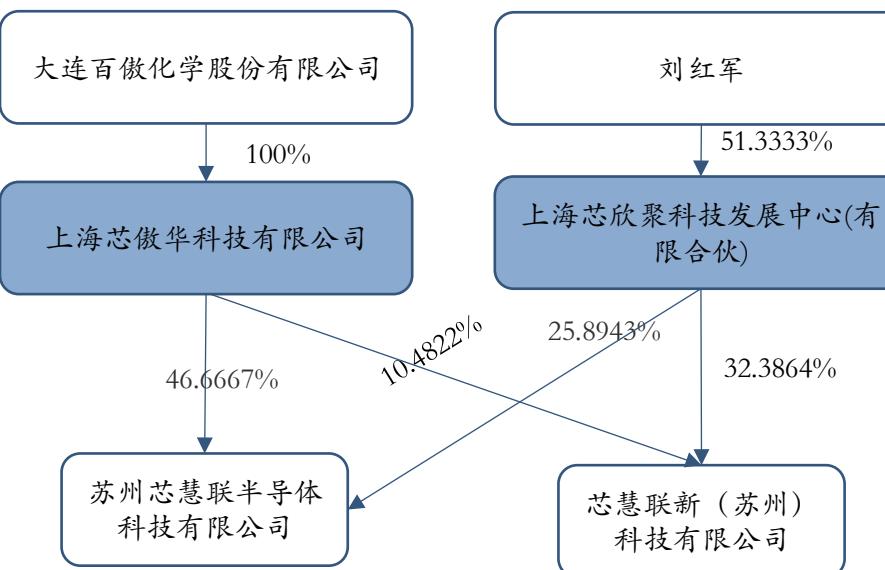

百傲化学&芯慧联股权梳理：

1. “芯慧联”派生出“芯慧联新”，主要应用于HBM（高带宽存储器）、3D闪存生产制造等3D化IC应用领域的晶圆键合设备相关业务及资产已经划转至芯慧联新名下。

2. 百傲化学全资子公司芯傲华参股持有“芯慧联新”10.4822%股权。

3. 百傲化学全资子公司芯傲华直接持有“芯慧联”46.6667%股权，并通过接受表决权委托方式合计控制其54.6342%股权的表决权。

资料来源：Wind、公司公告、华安证券研究所整理

百傲化学&芯慧联股权梳理示意图（截至2025年2月28日）

## 4.4 国内相关投资标的——2) 百傲化学

➤ 3DSIXI晶圆混合键合设备是高度自动化和集成化的键合设备，其广泛适用于CIS、3DNAND、DRAM、先进封装及其他市场。多种可定制的诸如EFEM、等离子活化、清洗、检测、对准及键合等块集成于一台全自动设备中。通过自有算法补正，可以达到晶圆间的高精度对准。

➤ **产品特性**

- 适用于晶圆熔融键合及混合键合

- 晶圆尺寸:12寸

- 适用于不同薄膜材料

- 紧凑性高，占地小

- 设备内可集成对准精度检测和气泡缺陷检测

- 生产效率:可根据需求定制。

➤ 晶圆熔融键合设备是高度自动化和集成化的键合设备，其广泛适用于BSI、半导体光学及其他市场。多种可定制的诸如EFEM、等离子活化、清洗、检测、对准及键合等模块集成于一台全自动设备中。通过配置多个等离子活化工艺腔体来达到更高的生产效率。

➤ **产品特性**

- 适用于晶圆熔融键合晶圆尺寸:8寸/12寸

- 适用于不同基板材料:硅、玻璃

- 适用于不同薄膜材料

- 紧凑性高，占地小

- 生产效率:可根据需求定制

资料来源：芯慧联官网、华安证券研究所整理

## 4.5 标的估值梳理

| 公司    | 代码        | 股价(元)<br>2025/3/19 | 市值<br>2025/3/19 | 2023年收入<br>(亿元) | 2023年净利润<br>(亿元) | 2023年毛利率 | PE -2023 | 2024年收入<br>(亿元) | 2024年净利润<br>(亿元) | PE -2024 |

|-------|-----------|--------------------|-----------------|-----------------|------------------|----------|----------|-----------------|------------------|----------|

| Besi  | BESLAS    | 847.27             | 687.53          | 45.52           | 13.92            | 64.92    | 49.38    | 47.77           | 14.31            | 48.04    |

| HANMI | 042700.KS | 439.75             | 424.86          | 7.90            | 13.28            | 49.94    | 32.00    | 27.77           | 7.58             | 56.03    |

| ASMPT | 0522.HK   | 55.37              | 230.58          | 137.31          | 6.60             | 39.28    | 34.93    | 124.55          | 3.19             | 72.37    |

| 拓荆科技  | 688072.SH | 172.22             | 481.75          | 27.05           | 6.63             | 51.01    | 72.71    | 41.03           | 6.88             | 69.98    |

| 芯源微   | 688037.SH | 98.43              | 197.81          | 17.17           | 2.51             | 42.53    | 78.93    | 17.70           | 2.11             | 93.79    |

| 芯碁微装  | 688630.SH | 66.12              | 87.11           | 8.29            | 1.79             | 42.62    | 48.58    | 9.54            | 1.65             | 52.82    |

| 迈为股份  | 300751.SZ | 91.35              | 255.24          | 80.89           | 9.14             | 30.51    | 27.93    | 112.38          | 11.43            | 22.33    |

| 百傲化学  | 603360.SH | 34.25              | 172.77          | 10.66           | 3.28             | 52.03    | 52.61    | -               | -                | -        |

| 快克智能  | 603203.SH | 25.85              | 64.41           | 7.93            | 1.91             | 47.30    | 33.72    | 10.18           | 2.64             | 24.40    |

注：

- 1、Besi、HANMI、ASMPT以2025/3/19人民币汇率中间价换算。

- 2、迈为股份2024年收入利润数据以wind一致预期

- 3、快克智能已覆盖，2024年收入利润采用盈利预测数据。

资料来源：WIND、外汇管理局、华安证券研究所整理

## 风险提示

- 1.半导体行业供需波动风险。

- 2.先进封装行业进展及下游应用不及预期的风险。

- 3.国产封装厂商及键合设备厂商发展不及预期的风险。

- 4.国际贸易政策变化的风险。

- 5.相关企业存货和应收账款减值风险。

- 6.市场竞争加剧的风险。

- 7.公司核心技术人员变动引发的风险。

- 8.核心零部件供应的风险。

- 9.测算市场空间的误差风险。

- 10.研究依据的信息更新不及时，未能充分反映公司最新状况的风险。

# 重要声明及评级说明

## 重要声明

### 分析师声明

本报告署名分析师具有中国证券业协会授予的证券投资咨询执业资格，以勤勉的执业态度、专业审慎的研究方法，使用合法合规的信息，独立、客观地出具本报告，本报告所采用的数据和信息均来自市场公开信息，本人对这些信息的准确性或完整性不做任何保证，也不保证所包含的信息和建议不会发生任何变更。报告中的信息和意见仅供参考。本人过去不曾与、现在不与、未来也将不会因本报告中的具体推荐意见或观点而直接或间接接收任何形式的补偿，分析结论不受任何第三方的授意或影响，特此声明。

### 免责声明

华安证券股份有限公司经中国证券监督管理委员会批准，已具备证券投资咨询业务资格。本报告中的信息均来源于合规渠道，华安证券研究所力求准确、可靠，但对这些信息的准确性及完整性均不做任何保证。在任何情况下，本报告中的信息或表述的意见均不构成对任何人的投资建议。在任何情况下，本公司、本公司员工或者关联机构不承诺投资者一定获利，不与投资者分享投资收益，也不对任何人因使用本报告中的任何内容所引致的任何损失负任何责任。投资者务必注意，其据此做出的任何投资决策与本公司、本公司员工或者关联机构无关。华安证券及其所属关联机构可能会持有报告中提到的公司所发行的证券并进行交易，还可能为这些公司提供投资银行服务或其他服务。

本报告仅向特定客户传送，未经华安证券研究所书面授权，本研究报告的任何部分均不得以任何方式制作任何形式的拷贝、复印件或复制品，或再次分发给任何其他人，或以任何侵犯本公司版权的其他方式使用。如欲引用或转载本文内容，务必联络华安证券研究所并获得许可，并需注明出处为华安证券研究所，且不得对本文进行有悖原意的引用和删改。如未经本公司授权，私自转载或者转发本报告，所引起的一切后果及法律责任由私自转载或转发者承担。本公司并保留追究其法律责任的权利。

## 投资评级说明

以本报告发布之日起6个月内，证券（或行业指数）相对于同期相关证券市场代表性指数的涨跌幅作为基准，

A股以沪深300指数为基准；新三板市场以三板成指（针对协议转让标的）或三板做市指数（针对做市转让标的）为基准；香港市场以恒生指数为基准；美国市场以纳斯达克指数或标普500指数为基准。定义如下：

### 行业评级体系

增持—未来6个月的投资收益率领先市场基准指数5%以上；

中性—未来6个月的投资收益率与市场基准指数的变动幅度相差-5%至5%；

减持—未来6个月的投资收益率落后市场基准指数5%以上；

### 公司评级体系

买入—未来6-12个月的投资收益率领先市场基准指数15%以上；

增持—未来6-12个月的投资收益率领先市场基准指数5%至15%；

中性—未来6-12个月的投资收益率与市场基准指数的变动幅度相差-5%至5%；

减持—未来6-12个月的投资收益率落后市场基准指数5%至；

卖出—未来6-12个月的投资收益率落后市场基准指数15%以上；

无评级—因无法获取必要的资料，或者公司面临无法预见结果的重大不确定性事件，或者其他原因，致使无法给出明确的投资评级。

# 谢谢！

欢迎关注华安机械团队