证券研究报告 半导体设备/行业深度报告 领先大市(维持)

## 传统工艺升级&先进技术增量,争设备之滔滔不绝

——先进封装系列报告之设备

分析师: 熊 军 S0910525050001

分析师: 宋 鹏 S0910525040001

2025年06月20日

本报告仅供华金证券客户中的专业投资者参考请仔细阅读在本报告尾部的重要法律声明

### 核心观点

- 毕 发 集 团 控 股 公 司

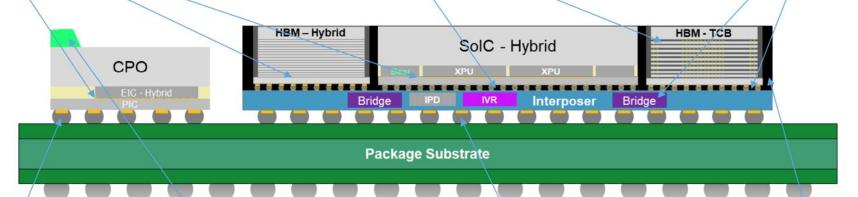

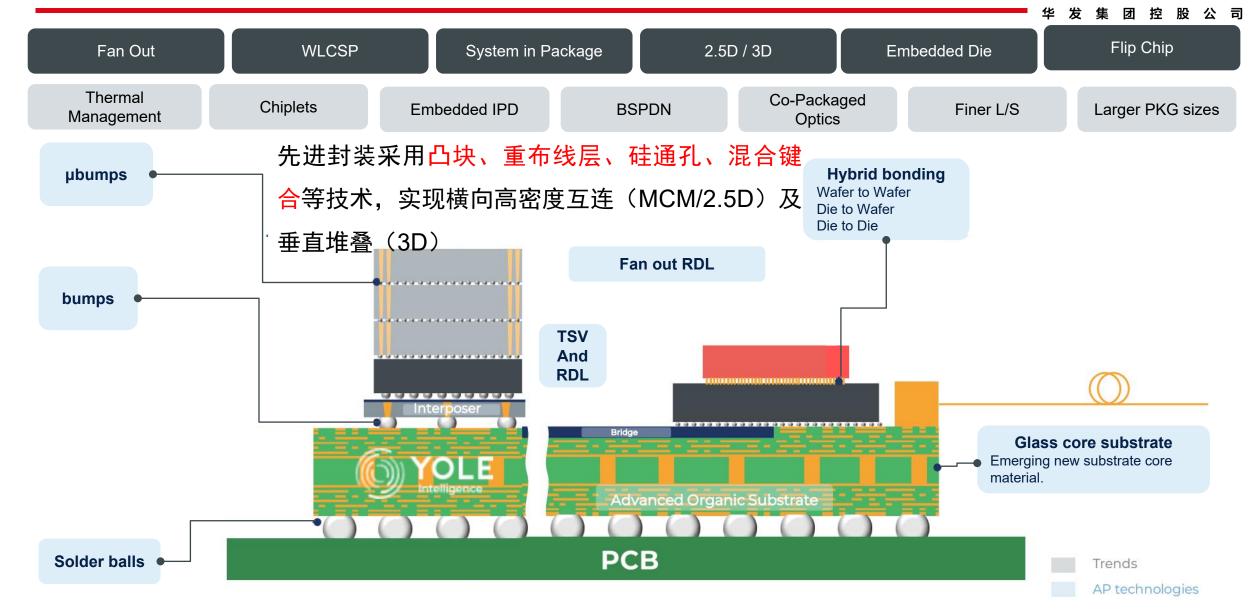

- ◆ 尖端先进封装需求持续增长,AI相关仍为主要驱动。得益于生成式人工智能和高性能计算(HPC)这两大长期趋势有力推动,叠加移动和消费市场回暖以及汽车先进封装解决方案的拓展,将为先进封装市场规模增长注入动力。先进封装技术也沿着多元化方向发展,2.5D/3D 封装成为 AI 芯片的核心封装方案;系统级封装(SiP)通过微型化集成技术,在可穿戴设备、AR/VR领域占据优势;扇出型封装(FOPLP)加速布局,以更低成本和更大灵活性满足5G与消费电子需求;混合键合技术作为下一代高密度集成的关键,各个头部厂家等正推动其量产进程。根据Yole预测,全球先进封装市场规模将从2023年的378亿美元增至2029年的695亿美元。这一增长主要得益于 AI、高性能计算及 5G/6G 技术对算力密度的极致需求,以及数据中心、自动驾驶等领域对低功耗、高可靠性封装的迫切需要。

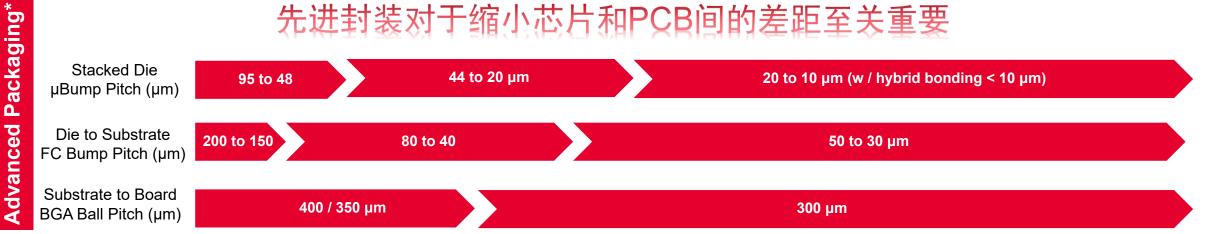

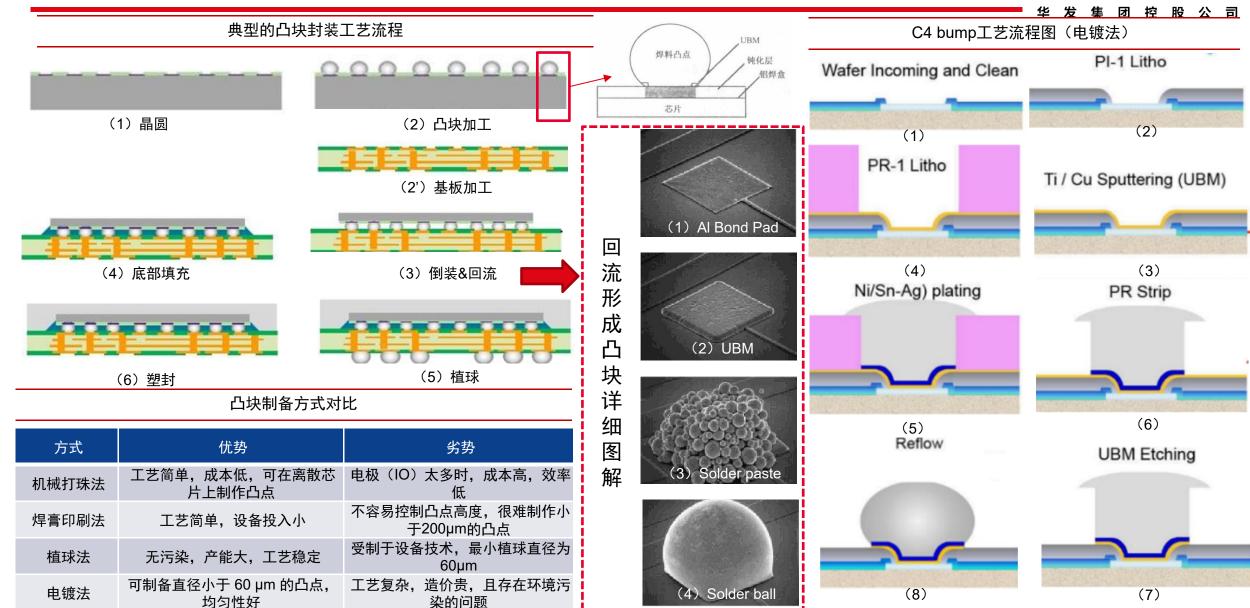

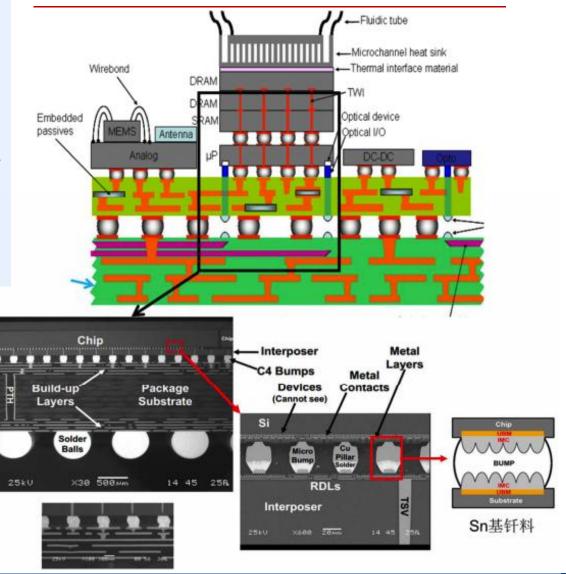

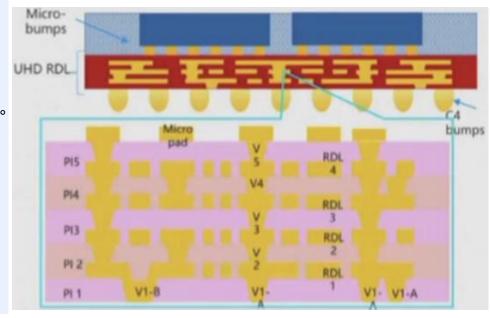

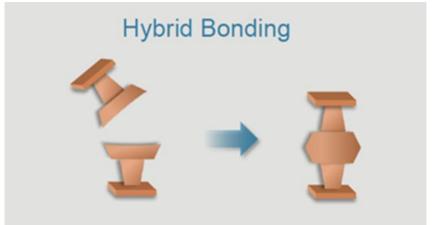

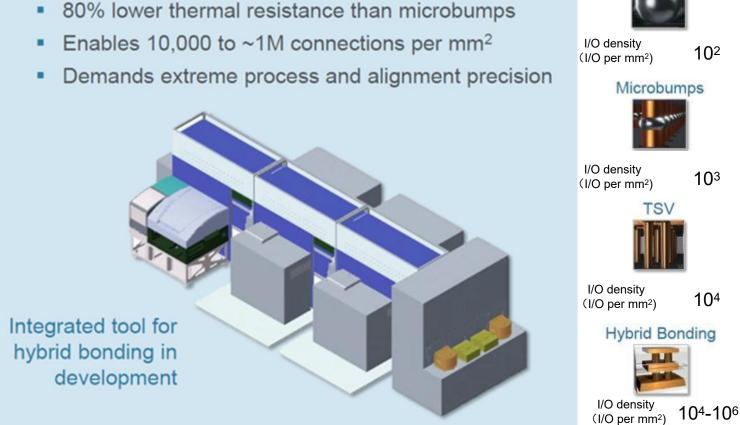

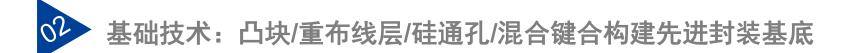

- ◆ 凸块/重布线层/硅通孔/混合键合构建先进封装基底。(1)Bump: 朝着更小节距、更小直径方向不断发展。目前,三维系统封装技术中微凸点互连是关键技术,其是利用在芯片上制备可润湿的微凸点,与基板上的区域对准,并通过微互连工艺使其连接,实现最短的电连接通路,从而大幅度提高封装密度。(2)RDL: 改变IC线路接点位置。根据未来半导体披露,头部厂商封装业务RDL L/S(线宽和线间距)将从2023/2024年的2/2µm发展到2025/2026的1/1µm,再跨入到2027年后的0.5/0.5µm。(3)硅通孔: 在硅片上垂直穿孔并填充导电材料,实现芯片间立体互连。在2.5D封装中TSV充当多颗裸片和电路板之间桥梁,其中CoWoS为2.5D封装中最突出代表,在3D中TSV用于堆叠,HBM为3D封装最典型应用。(4)混合键合:利用范德华力实现,不需额外施加能量键合。混合键合通过金属(例如,铜)和氧化物键合的组合来连接芯片。其主要优点在于减少凸块间距和接触间距,从而增加相同区域内的连接密度。这反过来又可以实现更快的传输速度并降低功耗。

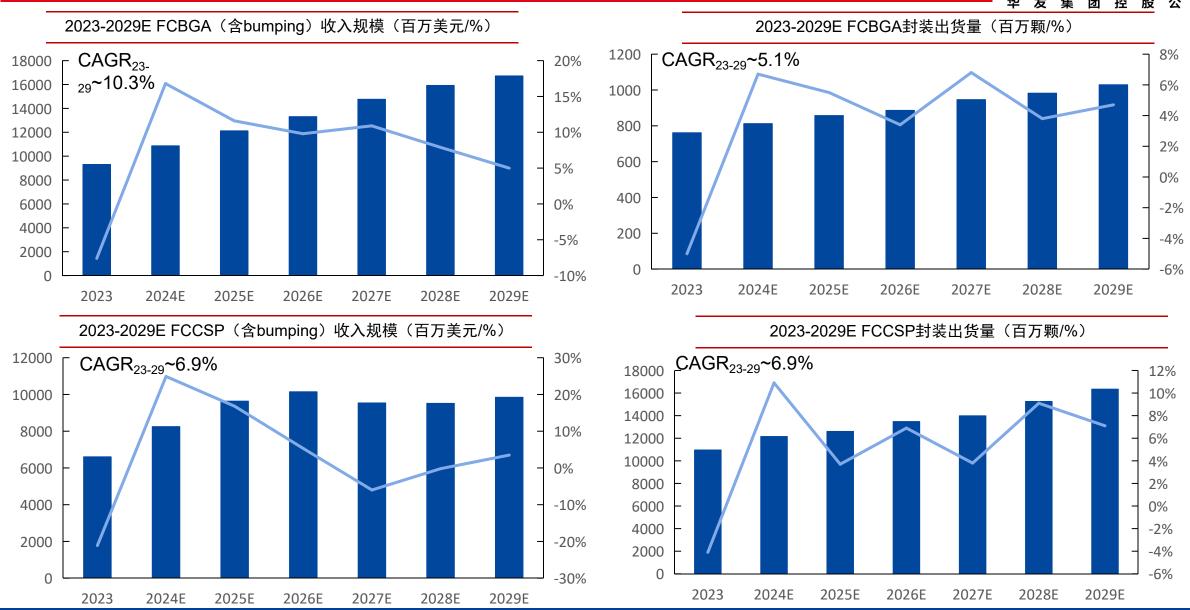

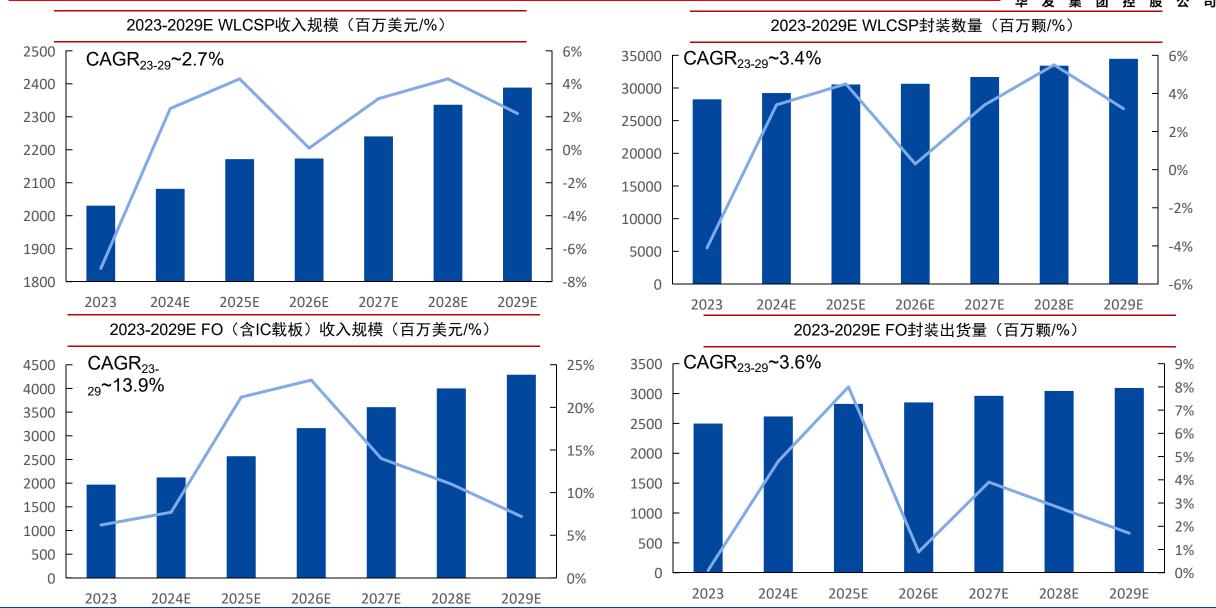

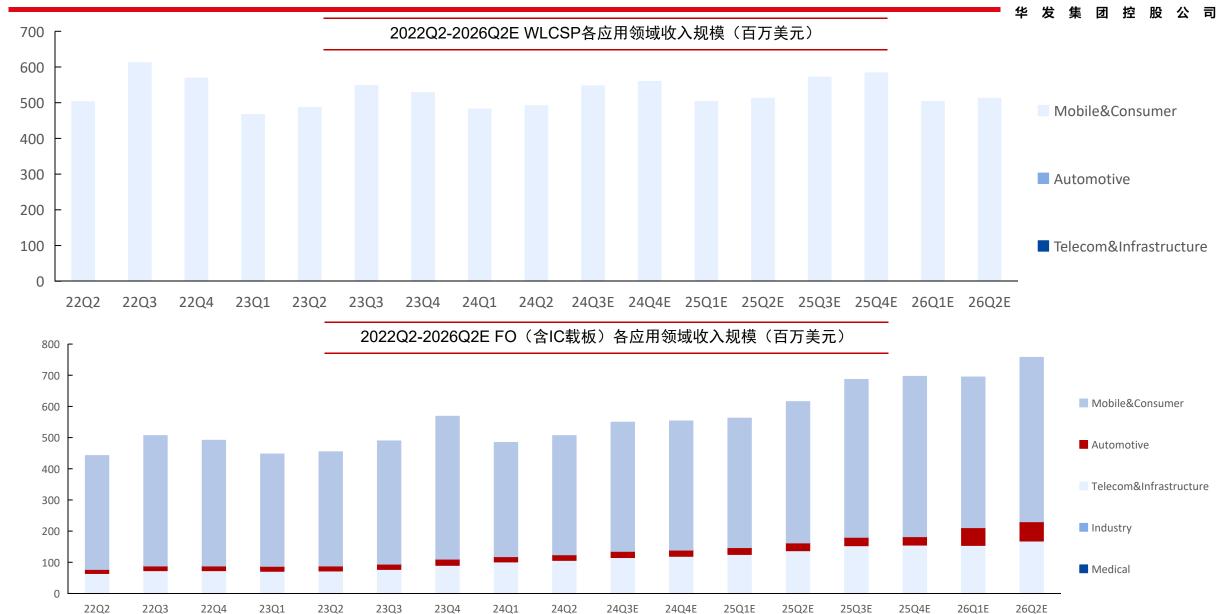

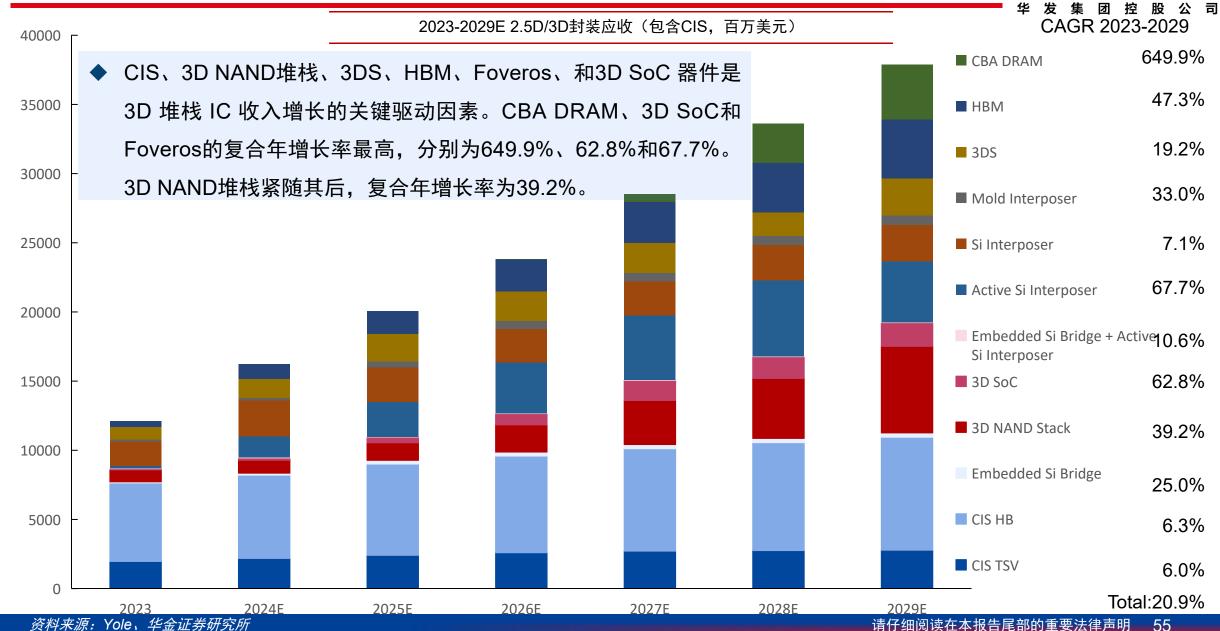

### 核心观点

- FC/WLP/2.5D/3D四大方案助力封装技术迭代结构升维。(1)FC:信号路径优化、散热性能提升、I/O引脚密度增加。根据 Yole数据,2024Q2 FCBGA营收为23亿美元,环比增长6.8%,同比增长18%。由于人工智能需求的增长以及更多采用 FCBGA的2.5D/3D封装,预计未来几个季度市场将保持健康增长:FCCSP未来两年收入将有所增长,主要原因是存储需求修 正及AI相关需求维持高位。(2)WLP:先在整片晶圆上同时对众多芯片进行封装、测试,最后切割成单个器件,并直接贴装 到基板或PCB上,生产成本大幅降低。根据Yole数据,2029年WLCSP预计规模为24亿美元;FO(含IC基板)预计规模为43 **(3)多芯片互联:**①2.5D:利用CoWoS封装技术,可使得多颗芯片封装到一起,通过硅中介板互联,达到封装体 积小,功耗低,引脚少等效果。②3D:HBM在前端制程完成后,增加TSV制程,TSV的深度是根据三维堆叠时芯片的厚度而 确定的,目前通常在20-30µm左右。③嵌入式:是通过硅片进行局部高密度互连。与传统2.5封装没有TSV,因此EMIB技术具 有正常的封装良率、无需额外工艺和设计简单等优点。根据Yole数据,2029年2.5D/3D(封装形式包含嵌入式,产品包含CIS) 规模有望达378.58亿美元。

- ◆ 投资建议:先进封装技术的迭代对先进封装设备提出更高要求,推动行业进入增量发展新阶段。据TechInsights 数据,2024年全球先进封装设备市场规模达31亿美元,创历史新高。随着先进封装装备技术快速升级,前道工艺后移,推动刻蚀、薄膜沉积、电镀等设备需求快速增加。国内设备厂商依托本土产业链优势,在细分领域实现突破。建议关注:ASMPT、北方华创、中微公司、芯源微、拓荆科技、盛美上海、华海清科、芯碁微装、新益昌、光力科技、华封科技(未上市)。

- ◆ **风险提示**:新技术、新工艺、新产品无法如期产业化风险;市场需求波动风险;国际贸易摩擦风险;供应链风险。

- № 堆叠互联: FC/WLP/2.5D/3D四大方案助力封装技术迭代结构升维

- 设备: 传统工艺升级&先进技术促前道设备增量

- 相关标的

- 06 风险提示

先进封装:尖端先进封装需求持续增长,AI相关仍为主要驱动

基础技术: 凸块/重布线层/硅通孔/混合键合构建先进封装基底

堆叠互联: FC/WLP/2.5D/3D四大方案助力封装技术迭代结构升维

设备: 传统工艺升级&先进技术促前道设备增量

相关标的

风险提示

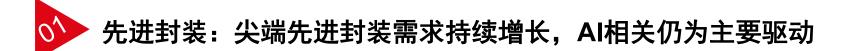

### 1.1发展历程: 迎来以3D封装为代表高密度封装时代

#### 诵孔插装时代 表面安装器件时代

技术特点:插孔安装在 技术特点:引线代替针脚,引线 PCB上,引脚节距固定, 为翼形或J形,封装体的尺寸 引脚数增加伴随封装尺╻固定而周边引脚节距根据需要 「变化。

寸的增大。

#### 面积阵列表面封装时代

技术特点: 焊球代替引线, 按面积阵列形式分布 的表面贴装。

安装密度: 40-60引脚/引脚/cm<sup>2</sup>

多引线的集成电路芯片的封装问题。

超越传统意义的安装密度。

优点:降低能耗,提高集成度。

封装体内于垂直方向叠放两个以上芯片。

3D TSV

优点:解决了多功能、高集成度、高速低功耗、

3D堆叠

高密度封装时代

技术特点:在不改变封闭体安装面积的前提下,在同一个

TO DIP SOP **QFP**  **BGA CSP**

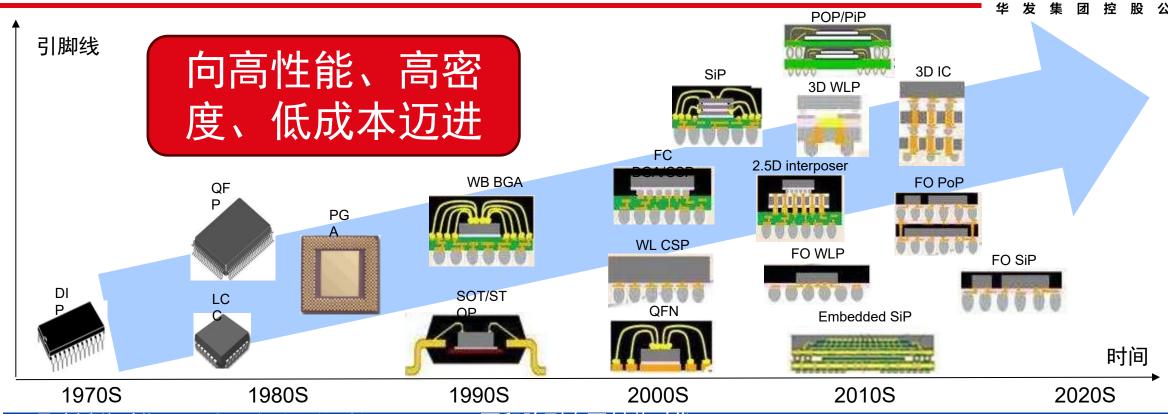

## 1.2高性能封装: I/O密度>16 I/Os per mm² & Pitch<130μm 1 毕氩业秀

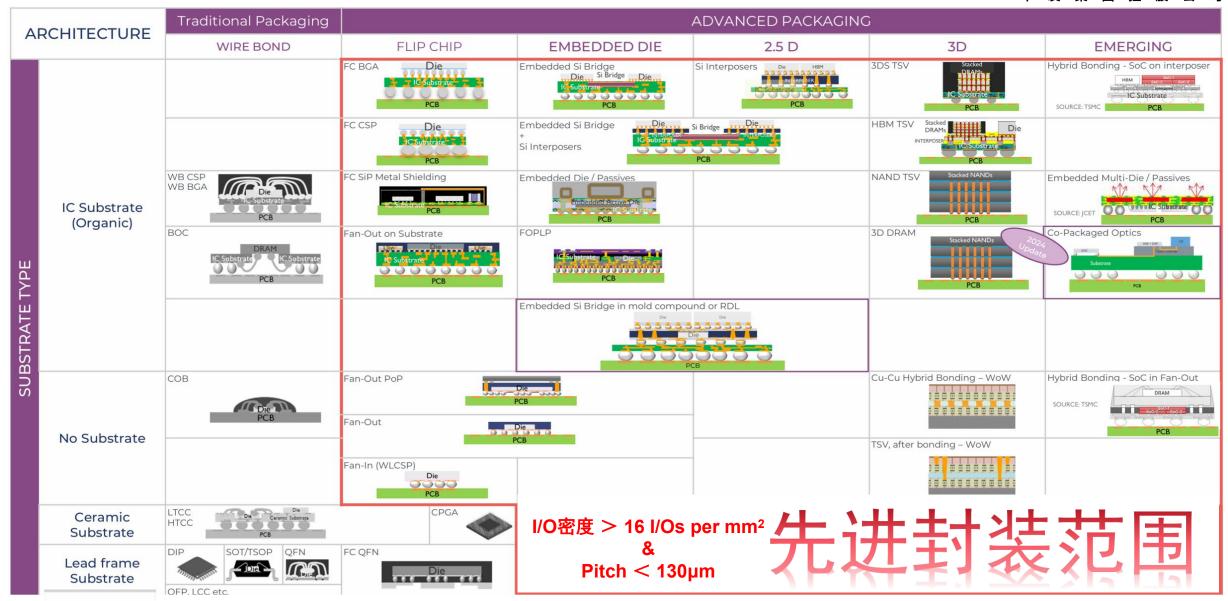

## 1.3先进封装规模: 29年有望达800亿美元, 2.5D/3D增长最为迅速

华 发 集 团 控 股 公 司

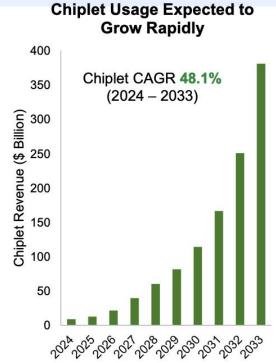

◆ 根据Yole数据,先进封装市场规模有望从2023年的390亿美元攀升至2029年的800亿美元,其复合年增长率可达12.7%。由于2023年半导体行业表现较为疲软,先进封装市场受到波及,市场规模同比下降3.5%。得益于生成式人工智能和高性能计算(HPC)这两大长期趋势有力推动,叠加移动和消费市场回暖以及汽车先进封装解决方案的拓展,将为先进封装市场规模增长注入动力。在先进市的细分领域中,凭借新技术的广泛应用以及其提供的高价值解决方案,2.5D/3D封装有望在未来五年内以20.9%的增速脱颖而出,或成为推动整个市场发展关键力量。

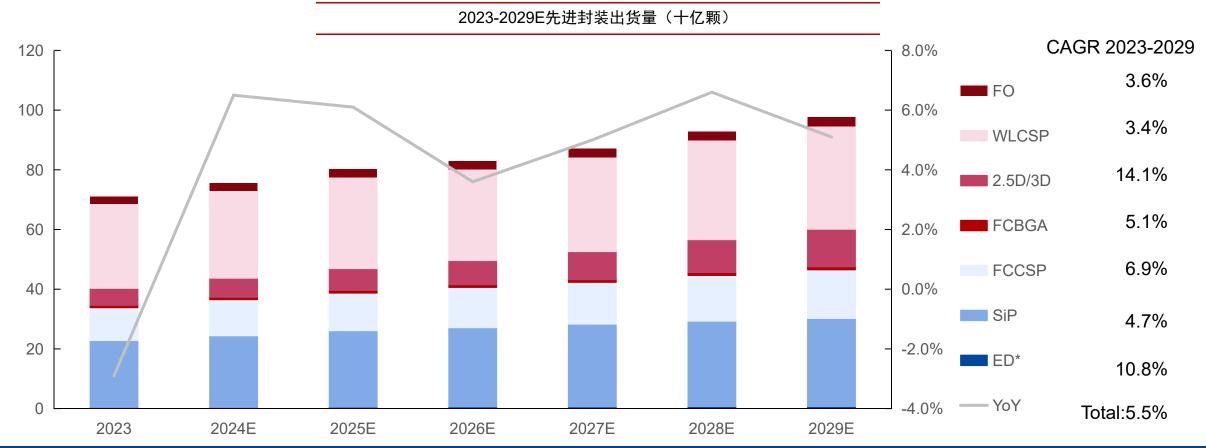

# 1.4先进封装出货量: 29年有望达976亿颗, WLCSP/SiP/FCCSP等出货量领先

华发集团控股公司

◆ 根据Yole数据,先进封装出货量有望从2023年的709亿颗攀升至2029年的976亿颗,其复合年增长率可达5.5%。其中,WLCSP(晶圆级芯片尺寸封装)、SiP(系统级封装)和FCCSP(倒装芯片级封装)在出货量方面处于领先地位。虽然2023年先进封装出货量下降2.9%。随着特定终端市场需求回暖以及先进封装技术的持续应用,未来几年先进封装出货量有望维持健康增长。

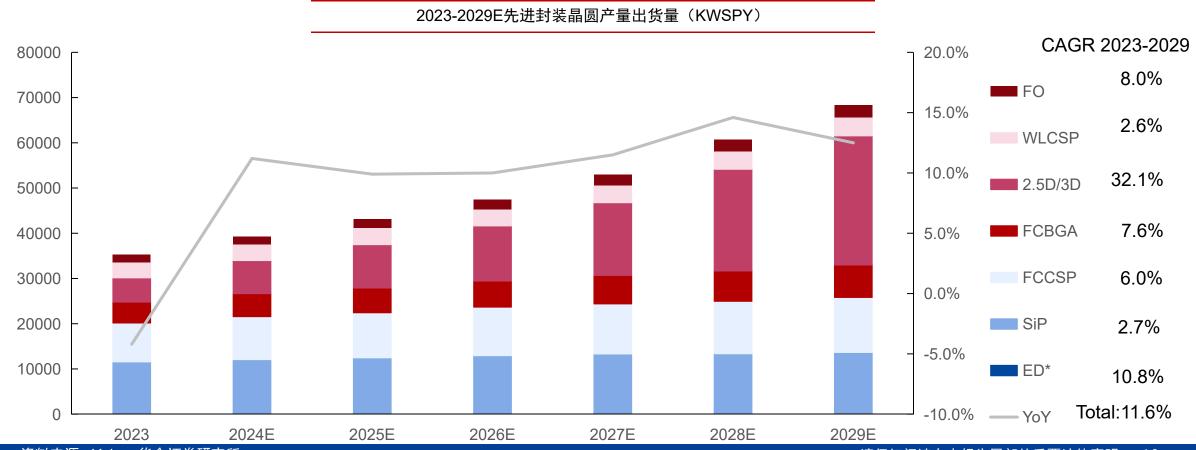

# 1.5先进封装晶圆产量:短期以SiP/FCCSP为主,27年2.5D/3D 封装有望放量

华发集团控股公司

◆ 根据Yole数据,2023年至2029年期间,先进封装晶圆总产量(等效300mm)预计将以11.6%的复合年增长率持续增长。其中,SiP和FCCSP在短期内仍将占据主要市场份额;2.5D/3D技术的增长速度最为迅猛,其复合年增长率高达32.1%,主要系受益于人工智能及高性能计算的应用,促使芯片面积增大(无论是以SoC还是Chiplet的形式)。

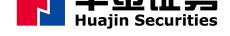

### 1.6技术路线:先进制程→纳米级,先进封装→微米级

### 1.6技术路线:摩尔定律放缓加速3D IC采用

发 集 团 控 股 公 司

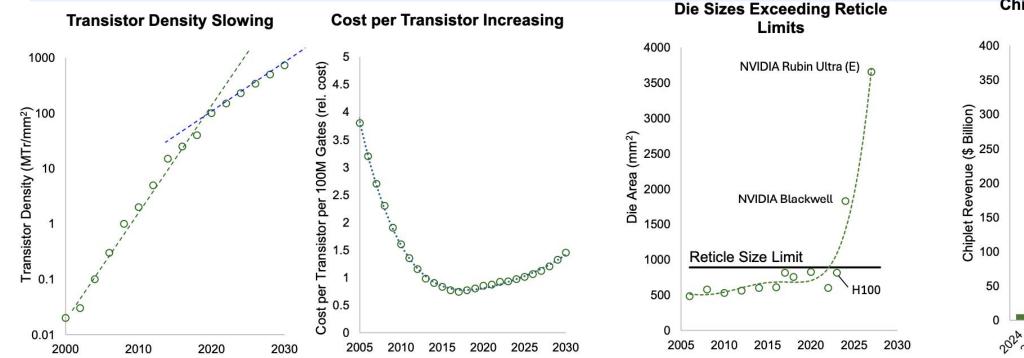

- ◆ 随着制程工艺推进,成本经济效益逐步降低。从成本方面来看,随着先进制程推进,芯片每平方毫米成本不断上升,但随着晶体管密度提升,同样数量晶体管所占芯片面积不断下降,故单位数量晶体管成本实际一直在下降。如英特尔14nm、10nm及7nm工艺晶体管成本有所下降,但下降幅度加速放缓。根据IBS数据,随着制程工艺推进,单位数量的晶体管成本的下降幅度在急剧降低,从16nm到10nm,每10亿颗晶体管的成本降低23.5%,而从5nm到3nm成本仅下降4%。

- ◆ 随着数据量呈指数级增长和商业应用扩展,摩尔定律正在放缓,客户采用通过混合键合和TCB连接的芯片,以优化每个节点的设备功能并降低成本。

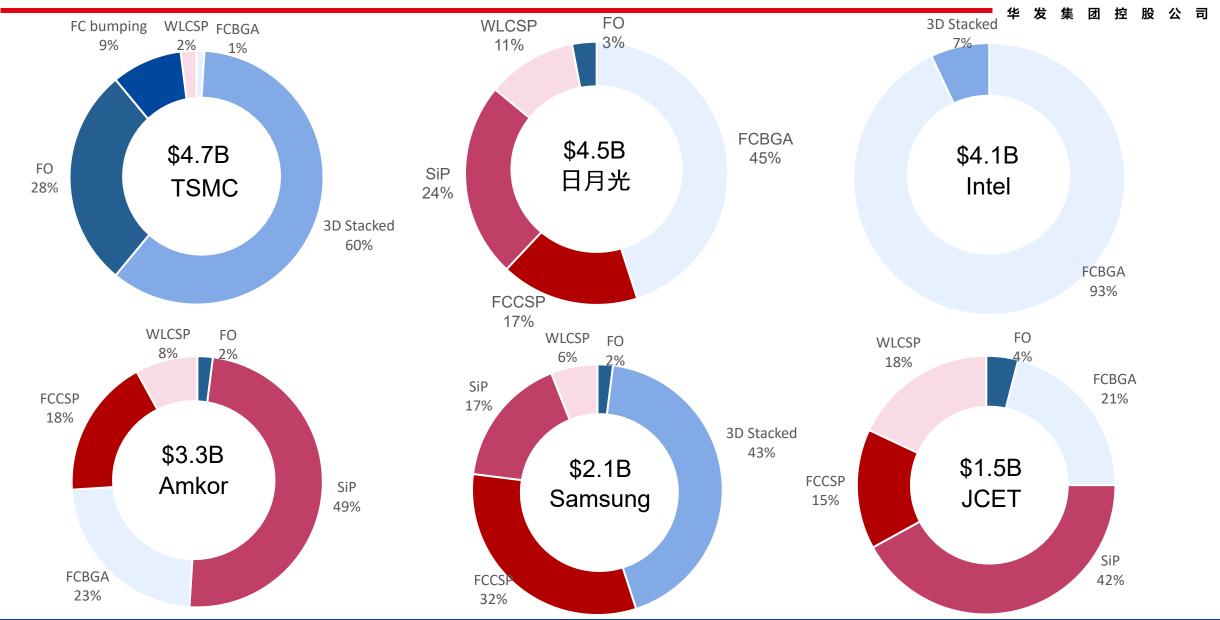

## 1.7格局:台积电/三星以堆叠为主,日月光/安靠以FC/SiP为主 华宝证秀

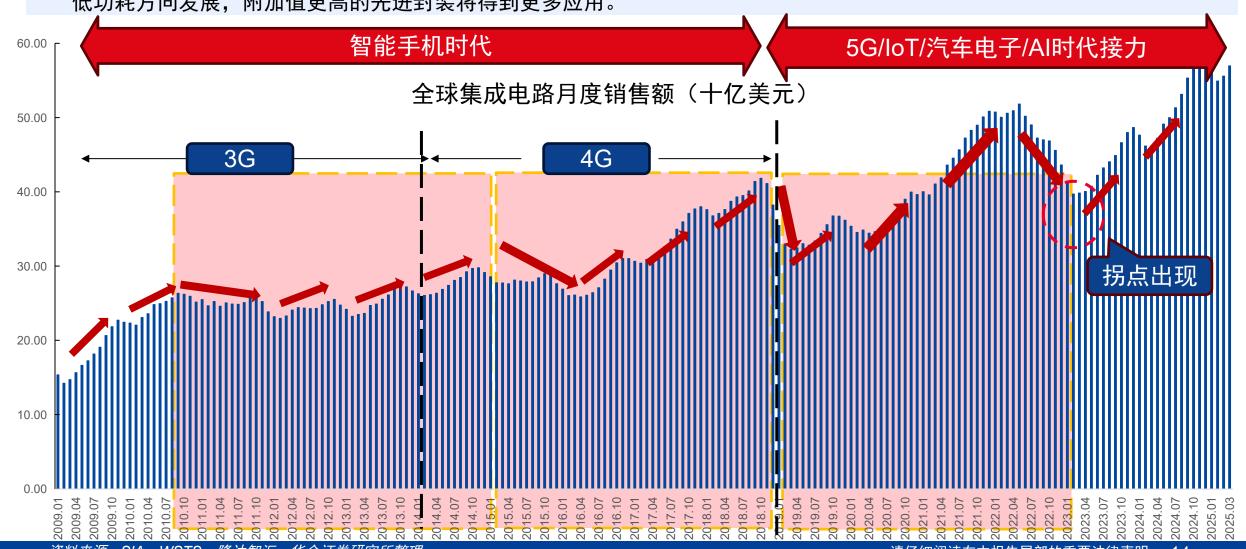

### 1.8市场:全球集成电路月度销售额拐点出现,有望带动封

华 发 集 团 控 股 公 司

◆ **市场拐点出现,有望带动封装市场增长。**未来,在新兴市场和半导体技术发展带动下,集成电路继续向着小型化、集成化、 低功耗方向发展,附加值更高的先进封装将得到更多应用。

装市场

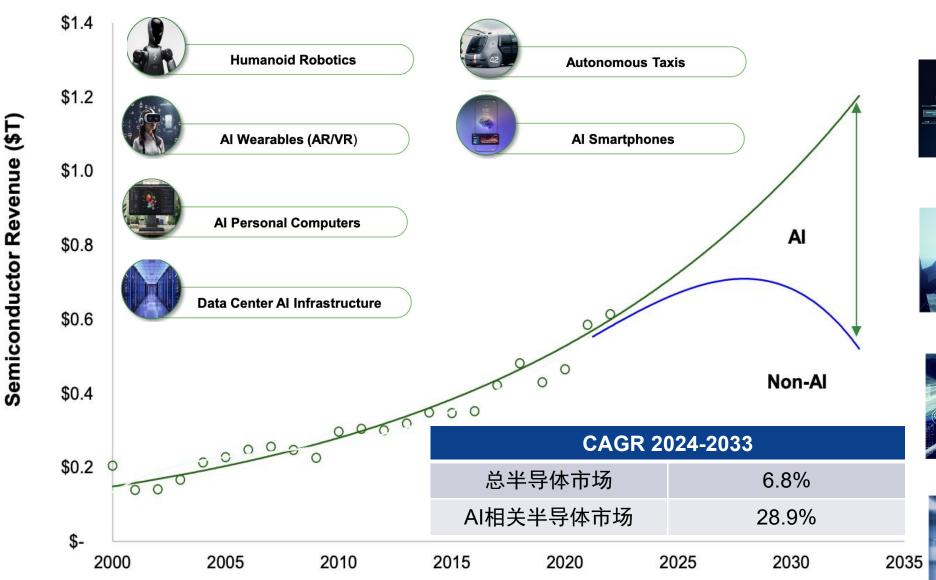

### 1.9驱动:人工智能正在推动半导体收入长期增长

- AI在PC中的应用

- 硅光子技术

- - AR/VR 头戴设备

- 摄像头技术

- 5G-A→6G

- 电气化

- 网联化

- 信息娱乐

- 智能电网

- 工业物联网

- 清洁能源

### 1.9驱动: AI芯片封装需要多种先进封装解决方案

#### **Hybrid Bonding**

3DIC stacking < 9µm pitch HBM stacking ≥ 16 High Photonics

### Thermo-compression Bonding

C2W chiplet stacking HBM stacking ≤ 16 High 3D bridge attach

#### CoW Flip-chip and Fan-out

CoW flip-chip of logic & memory

High-density fan-out

Embedded bridge die attach

### Flip-chip CoS

Advanced mass reflow flipchip attach > 40 um pitch

#### **Photonics**

High precision optical component placement

#### Interposer Attach

oS bonding of large interposers up to 110 mm

#### **Chiplet Molding**

CoW encapsulation CoWoS molded underfill

## 1.10扩产: 正在进行或计划中封装项目投资合计约千亿美元 1 华金 Huajin Se

| Packaging Fab Project                           | Initiated | Cost (\$B) | Status      |

|-------------------------------------------------|-----------|------------|-------------|

| TSMC AP7 CoWoS & SoIC - Chiayi,<br>Taiwan,China | 2024      | 15         | In Progress |

| TSMC AP – Arizona, USA                          | 2025      | ~10.0      | Planned     |

| TSMC AP8 CoWoS – Tainan,<br>Taiwan,China        | 2024      | 7.7        | In Progress |

| Intel - Penang, Malaysia                        | 2022      | 7.1        | On Hold     |

| Intel - Wroclaw West, Poland                    | 2023      | 4.6        | On Hold     |

| Intel Fab 11x - New Mexico, USA                 | 2021      | 4          | Ramping     |

| Intel – Chengdu, China                          | 2025      | 0.3        | Planned     |

| SK Hynix HBM - Indiana, USA                     | 2024      | 3.9        | Planned     |

| SK Hynix M15 Expansion - South Korea            | 2024      | 1          | In Progress |

| Samsung - Cheonan, South Korea                  | 2024      | 8.1        | Planned     |

| Samsung - Texas, USA                            | 2024      | 4          | Planned     |

| Micron - Singapore                              | 2025      | 7          | Planned     |

| Micron - Gujarat, India                         | 2023      | 2.8        | In Progress |

| Micron - Xi'an, China                           | 2023      | 0.6        | In Progress |

| STMicro – Catania, Italy                        | 2024      | 5          | Planned     |

| Packaging Fab Project                             | Initiated | Cost (\$B) | Status      |

|---------------------------------------------------|-----------|------------|-------------|

| SPIL – Changhua & Yunlin, Taiwan, China           | 2025      | 3.3        | In Progress |

| SPIL P1 - Pulau Pinang, Malaysia                  | 2024      | 1.3        | In Progress |

| SPIL – Houli Plant, Douliu Plant,<br>Taiwan,China | 2024      | 0.1        | In Progress |

| Silicon Box - Italy                               | 2024      | 3.6        | Planned     |

| Tata TSAT - Assam, India                          | 2024      | 3.2        | Planned     |

| Amkor Technology – Arizona, USA                   | 2024      | 2          | Planned     |

| SJ Semi AP – Jiangyin, China                      | 2023      | 1.4        | In Progress |

| JCET WLP – Jiangsu, China                         | 2024      | 1.4        | In Progress |

| HT Tech AP – Nanjing, China                       | 2024      | 1.4        | In Progress |

| TFME AP – Tongda, China                           | 2024      | 1          | In Progress |

| Hana Micron – Vietnam                             | 2025      | 1          | Planned     |

| GlobalFoundries AP – New York, USA                | 2025      | 0.6        | Planned     |

| Amkor + AICEP – Portugal                          | 2024      | 0.4        | In Progress |

| Foxconn EU                                        | 2025      | 0.3        | Planning    |

| JCET (automotive) - Shanghai, China               | 2023      | 0.2        | In Progress |

### 1.11近期展望:尖端先进封装需求持续增长,AI仍为主要驱动

| 华金              | 证为        |

|-----------------|-----------|

| <b>Huajin S</b> | ecurities |

| 公司   | 指引时间   | 指引详情                                                                                                                                                                                                                       |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 2025Q2 | 封测营收:环比增长9%-11%<br>封测毛利率:环比增长140-180基点                                                                                                                                                                                     |

| 日月光  | 景气度    | 前沿先进封装服务继续保持强劲增长,25Q1总体保持满负荷状态。行业方面,除汽车行业外,其他行业都在逐步复苏,就汽车行业而言,高端汽车产品目前的势头较好,传统的MCU和低端产品目前仍在经历一定程度库存调整。                                                                                                                     |

|      | 2025Q2 | 营收: 13.75亿美元-14.75亿美元<br>毛利率: 11.5%-13.5%                                                                                                                                                                                  |

| 安靠   | 景气度    | 随着人工智能应用向边缘设备转移,预计智能手机领域的创新会率先在高端市场加速,尤其是在应用处理器和连接应用领域,这两者都需要先进封装技术。尽管汽车和工业终端市场仍在从疲软的终端市场需求和高库存水平中复苏,但对先进封装解决方案的需求依然强劲,主要驱动力是ADAS和信息娱乐功能在各车型中的普及。在消费市场,长期驱动因素包括可穿戴设备和互联设备日益增长的需求。                                          |

|      | 2025Q2 | 告别25Q1运营低谷,25Q2公司业绩将持续增长。                                                                                                                                                                                                  |

| 力成科技 | 景气度    | 25Q2: AI相关产品需求放量,FC产能满载,新产品开发动能强劲;因应美国半导体关税政策的不确定性,客户已提前启动备货机制,提高成品库存,以弹性因应后续变化,此举大幅增加客户2Q25急单比率,相对六月后的备货可能趋保守;DRAM方面,预期第二季将逐季成长,主要客户调整库存近尾声,此外,AI应用相关的新产品持续驱动PC、智能手机甚至汽车市场需求。NAND方面,第二季封测订单成长,预期第三季手机及PC更换潮助益下,需求呈现上升的态势。 |

先进封装:尖端先进封装需求持续增长,AI相关仍为主要驱动

基础技术: 凸块/重布线层/硅通孔/混合键合构建先进封装基底

堆叠互联: FC/WLP/2.5D/3D四大方案助力封装技术迭代结构升维

设备: 传统工艺升级&先进技术促前道设备增量

相关标的

风险提示

### 2.0先进封装连接技术

### 2.1Bump:晶圆制造环节延伸,为FC前提

### 2.1Bump: 朝着更小节距、更小直径方向不断发展

半 发 集 团 控 股 公 司

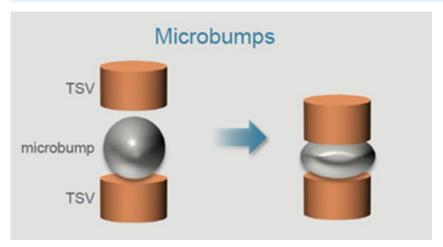

◆ 三维封装核心是芯片在垂直方向上进行堆叠,在异构集成、信号传输、封装尺寸、散热上具有显著优势,而作为实现垂直互连桥梁的微凸点发挥了重要作用。目前,三维系统封装技术中微凸点互连是关键技术,其是利用在芯片上制备可润湿的微凸点,与基板上的区域对准,并通过微互连工艺使其连接,实现最短的电连接通路,从而大幅度提高封装密度。三维系统封装中包含许多互连技术,其中C4可控塌陷芯片连接由于可实现基板到中介层间的连接,在倒装芯片互连技术尤为关键。

#### 凸块演进图

Old

Technology

|           | SnPb C4 Bump | Pb-Free C4 Bump | Cu Pillar +<br>Pb-free Cap | Cu µ-Pillar +<br>Pb-free Cap |

|-----------|--------------|-----------------|----------------------------|------------------------------|

| Structure |              | SnAg            | SnAg<br>Cu                 | SnAg                         |

| Diameter  | 75 – 200 μm  | 75 – 150 μm     | 50 – 100 μm                | 10 – 30 μm                   |

三维系统封装中微凸点(µ-bump)互连技术

**Current Technology**

**Next-Generation**

Technology

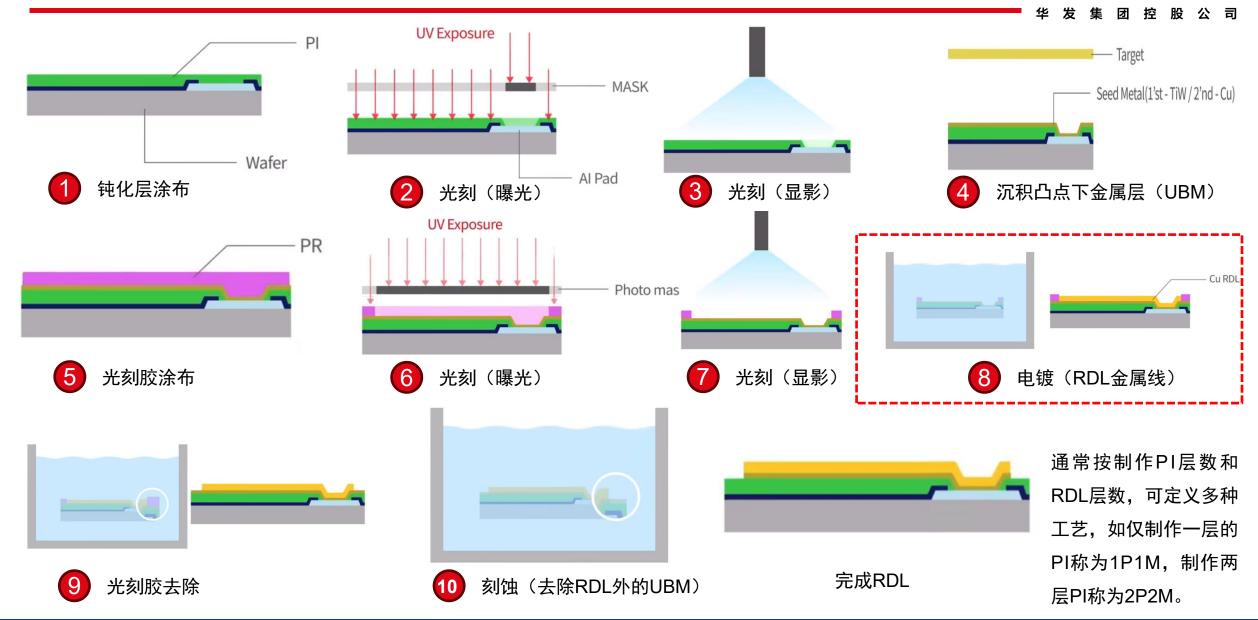

### 2.2RDL: 改变IC线路接点位置

华 发 集 团 控 股 公 司

典型RDL结构

- ◆ RDL是实现芯片水平方向互连关键技术,可将芯片上原来设计I/O焊盘位置通过晶圆级金属布线工艺变换位置和排列,形成新的互连结构。

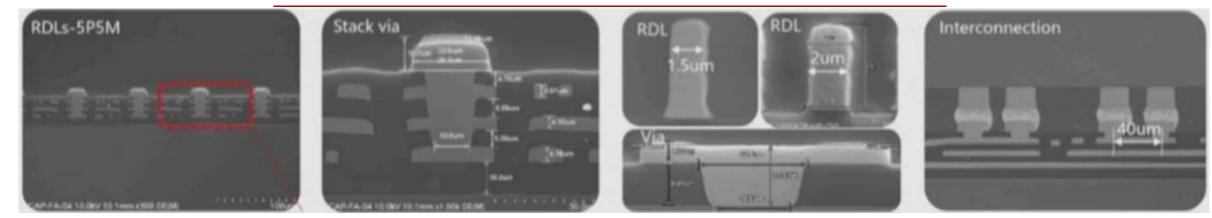

- 根据未来半导体披露,4层RDL已经成熟,良率已达到99%的水平,约85%的 封装需求可以通过4层RDL来满足,未来几年,布线层数从4层增加到8层以上。 头部厂商封装业务RDL L/S(线宽和线间距)将从2023/2024年的2/2μm发展 到2025/2026的1/1μm,再跨入到2027年后的0.5/0.5μm。

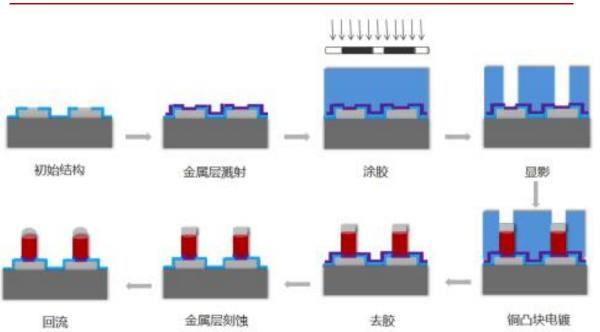

- ◆ RDL通常涉及半加成工艺,包括电介质沉积、湿法或干法蚀刻、阻挡层和籽晶层沉积以及镀铜。需要掩膜设备、涂胶机、溅射台、光刻机、刻蚀机以及其他配套工艺。

典型RDL结构

### 2.2RDL: 改变IC线路接点位置

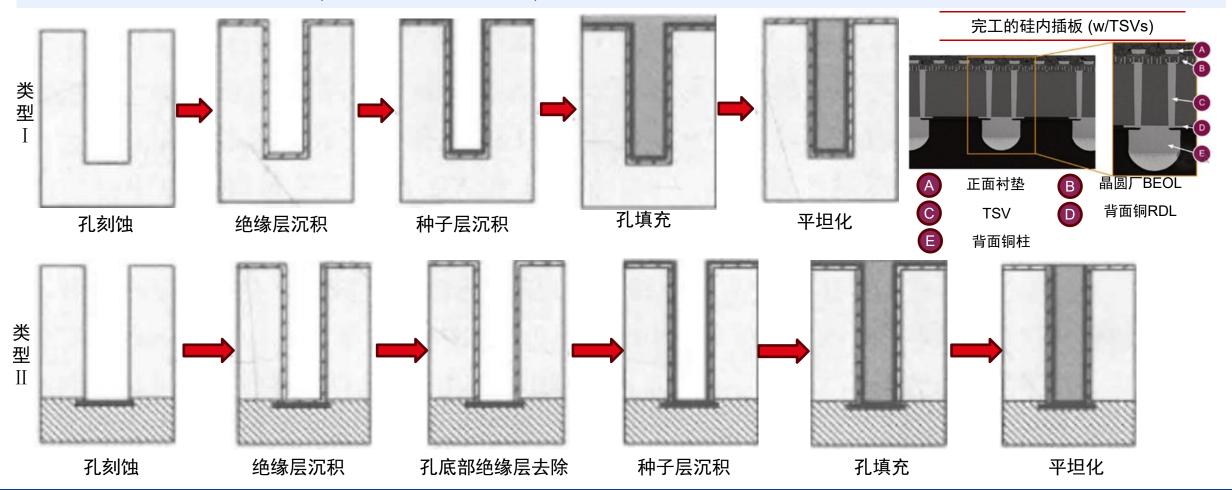

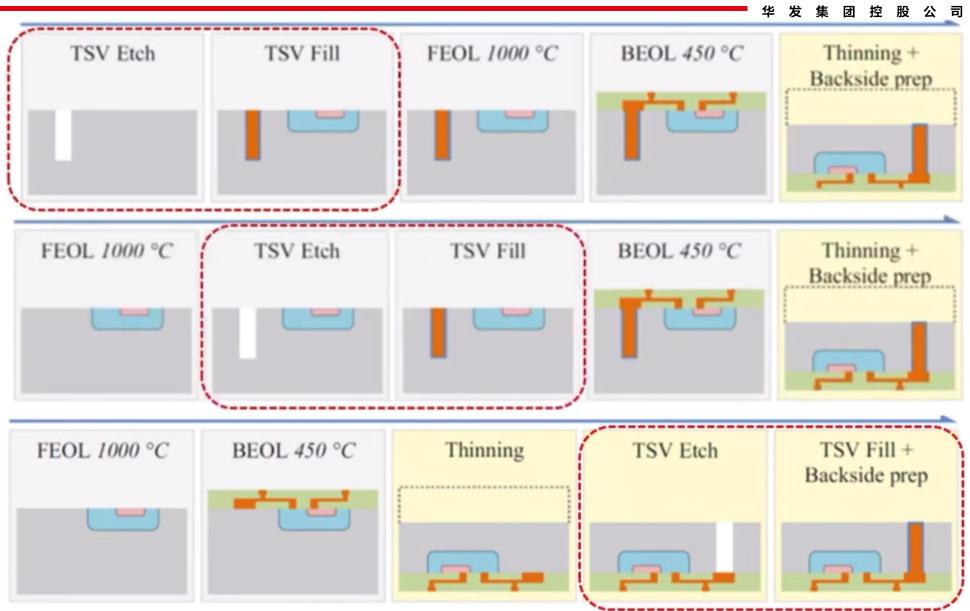

# 2.3TSV: 在硅片上垂直穿孔并填充导电材料,实现芯片间立体互连

毕 发 集 团 控 股 公 司

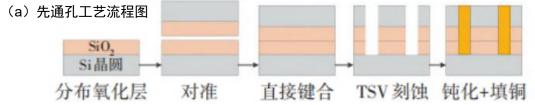

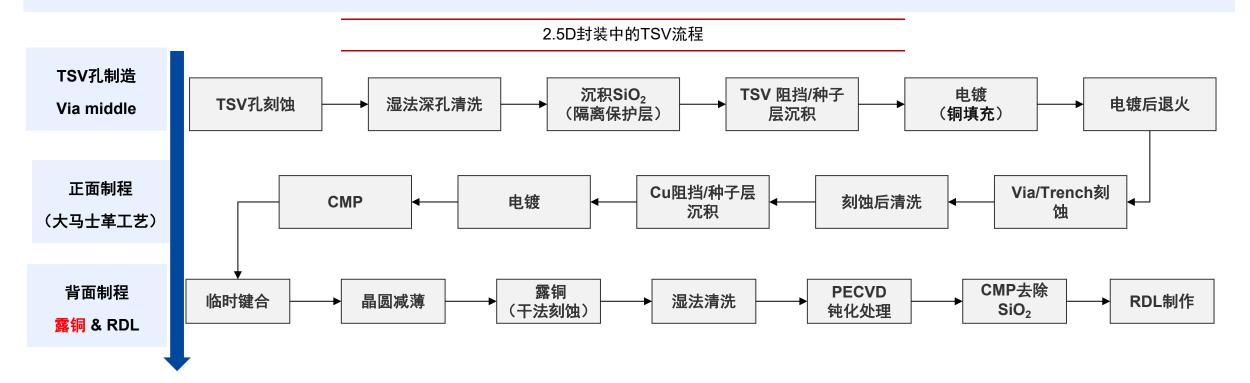

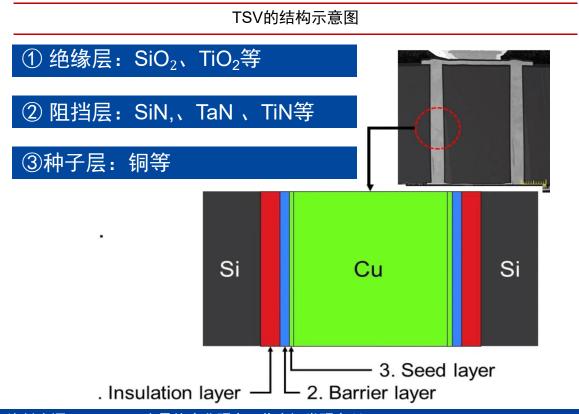

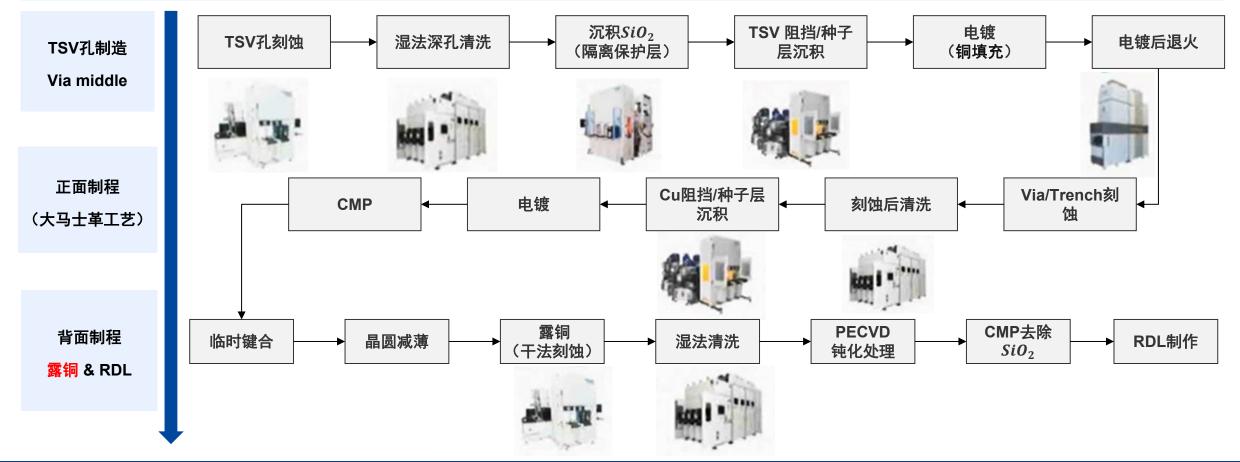

◆ TSV制造的主要工艺步骤包括孔刻蚀、绝缘层沉积、扩散阻挡层/种子层沉积、导电材料填充及表面平坦化等。TSV制造可以分为两种类型,类型I是孔底部不需要直接导电连接的制造类型,类型II是孔底部需要直接导电连接的制造类型。对于孔底部需要直接导电连接的类型,在完成绝缘层沉积后,需要选择性地将孔底部绝缘层去除。

## 2.3TSV:在硅片上垂直穿孔并填充导电材料,实现芯片间

#### Via First

立体互连

填充材料必须要能经受住高于 1000℃全部热加工工艺,故常 用填充材料是多晶硅,不需要 种子层,且绝缘层可以采用传 统氧化工艺制作。

### Via Middle (最普遍)

制作通孔时,CMOS**结构已经** 完成并钝化,不会再经历高温工艺,因此可以使用电性能和热性能比多晶硅更优良的**Cu作** 为通孔填充材料。

#### Via Last

晶圆在通孔形成前已经减薄到 其最终厚度,刻蚀TSV后不便 进行Cu填充(铜膨胀系数大), 采用将Si片固定在载片或者底 部晶圆上,进行减薄后,再进 行TSV刻蚀和填充。

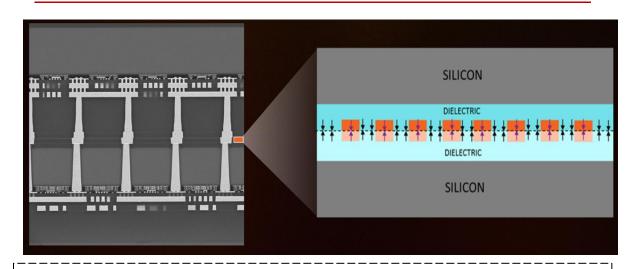

### 2.4混合键合:通过金属和氧化物键合的组合来连接芯片

半 发 集 团 控 股 公 司

◆ Hybrid Bonding是一种芯片连接技术,不同于封装中使用的主流Bump(焊料凸块)键合。混合键合通过金属(例如,铜)和氧化物键合的组合来连接芯片。其主要优点在于减少凸块间距和接触间距,从而增加相同区域内的连接密度。这反过来又可以实现更快的传输速度并降低功耗。

### 2.4混合键合:利用范德华力实现,不需额外施加能量键合

长 发 集 闭 控 股 公 司

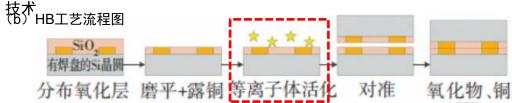

◆ HB技术在SiO₂界面键合之前进行大马士革布线,将Cu焊盘和SiO₂共存的异质界面磨平后面对面键合,彻底省略TSV工艺。 HB 是通过分子间作用力(范德华力)实现的,通常使用化学机械抛光(CMP)对大马士革布线层进行表面处理,CMP过程还可以减少Cu线路腐蚀和Cu凹陷。当Cu和SiO₂的光滑界面相互接触时,Cu和SiO₂的原子/分子形成牢固的范德华力,这个过程在热力学上是自发的,并不需要额外施加能量来驱动键合。此外,由于Cu和SiO₂原子/分子键合机理相同,理论上可以实现Cu-Cu、SiO₂-SiO₂、Cu-SiO₂三种界面的同步键合。

#### TSV先通孔工艺与HB工艺流程图

HB始于SiO $_2$ - SiO $_2$ 界面直接键合,最初将硅晶圆背面 SiO $_2$ 与有大马士革布线的硅晶圆正面SiO $_2$ 磨平后压合到一起,制备了TSV 后在上方进行大马士革布线。TSV 先通孔工艺可以省略 FC 工艺的植球、回流、底填等步骤,相对更加高效,但依然要让铜穿过硅片,对上下晶圆的大马士革布线进行互连,该工艺同样离不开 TSV 技术

为增强表面结合力,通常需要增加等离子体活化工序,然后再通过高精度的倒装热压工序,实现多界面之间的混合键合

AMD 3D V-Cache横截面

AMD 3D V-Cache采用台积电的SoIC-X的die-to-wafer混合键合。顶部和底部硅之间的键合界面是混合键合层,存在于硅芯片的金属层的顶部。

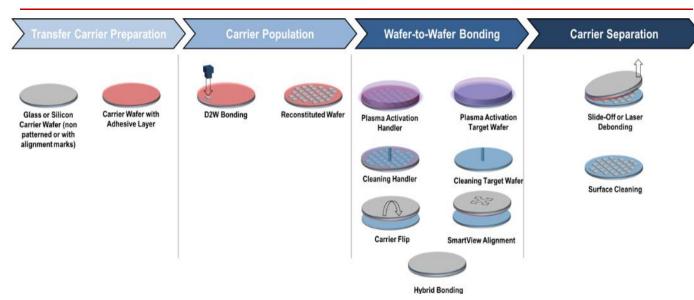

### 2.4混合键合: W2W Vs. D2W

华发集团控股公司

▶ W2W键合良率更高的原因在于对准和键合步骤是分开的。在W2W工具中,有一个单独的腔室来执行对齐。一旦顶部和底部晶圆对齐,就会被移入键合室(处于真空中),形成初始预键合。W2W的关键在于它是一个更加干净的过程,步骤更少。在对准和键合之前,可以清洁晶圆以去除大部分

颗粒。但W2W无法执行晶圆分类来选择已知良好

的芯片 (KGD)。这会导致将有缺陷的芯片粘合到

良好的芯片上,从而导致良好硅的浪费。

◆ D2W可以是一个 "collective"工艺,其中 KGD 对 齐并首先临时粘合到重构的载体晶圆上。然后将 重构的载体晶圆键合到基础晶圆上以进行实际的 预键合。这是为了像W2W一样将对准和粘合分开, 并允许在最终预粘合、键合之前进行清洁步骤, 以清除已积累的任何污染物。缺点是涉及额外步 骤,并且额外的W2W键合步骤会产生更多对准错 误机会。

### W2W Vs.D2W

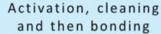

### Wafer to Wafer Hybrid Bonding

Die remain on wafer

Grinding and thinning, sent to packaging

- CIS

- 3D NAND

#### Die to Wafer Collective Hybrid Bonding

Die to be bonded are prepared, diced, then placed on carrier wafer

Activation, cleaning and then bonding

Remove carrier wafer, leaving bonded die on target wafer

- CIS

- SRAM on Logic

#### Die to Wafer Sequential Hybrid Bonding

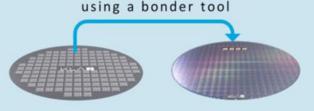

Singulated die are transferred to carrier for activation and cleaning

Direct placement of die using a bonder tool

- CIS

- SRAM on Logic

- HBM

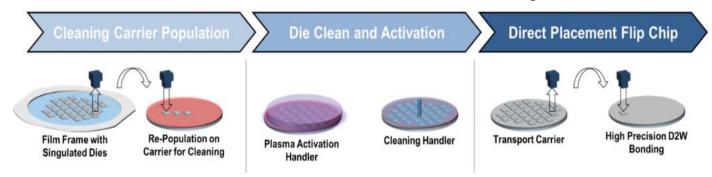

### 2.4混合键合: Co-D2W Vs.DP-D2W

华发集团控股公司

- ◆ Hybrid Bonding技术最早实际应用于SONY公司高端 CMOS Image Sensor产品。通过把图像传感器晶圆、数据存储及处理芯片的晶圆直接键合,实现大规模图像数据高效并行传输,后来该技术被广泛应用于逻辑芯片及存储芯3D互连。由于需要解决不同裸片尺寸芯片间直接键合,混合键合应用从Wafer to Wafer(W2W)基础上发展出Die to Wafer(D2W),即将切割好裸片一个个贴到另一个完整晶圆上,和晶圆上的裸片实现键合。

- ◆ Co-D2W:将切割好Die用临时键合方式粘到Carrier 晶圆上,随后整片和另一片产品晶圆整片键合再解键。 该技术类似于W2W,相对成熟,但一次D2W叠加一 次W2W方式容易累计误差,Carrier晶圆处理成本高, 且对Die厚度变化范围有较高要求。

- ◆ DP-D2W:将切好Die一颗颗放置于另一片产品晶圆对应位置。该路线位置精度将会提高且对Die厚度变化容忍度高,但有颗粒控制等问题。

晶圆混合键合(D2W)技术两种技术路径

Co-D2W: Collective Die-to-Wafer Bonding

DP-D2W: Direct Placement Die-to-Wafer Bonding

### 2.4混合键合: Co-D2W Vs.DP-D2W

华 发 集 团 控 股 公 司

|                        | Die-to-Wafer Cost |            |                   |                    |       |       |                      |            |                           |                                         |                       |                             |

|------------------------|-------------------|------------|-------------------|--------------------|-------|-------|----------------------|------------|---------------------------|-----------------------------------------|-----------------------|-----------------------------|

| Height /<br>Width (mm) | Area (mm²)        | Wafer Cost | Dies Per<br>Wafer | D0 (Defects / cm²) | Yield | GDPW  | Cost Per Die<br>Bond | Bond Yield | Good<br>Packages<br>Yield | Good<br>Packages Per<br>Bonded<br>Wafer | Total<br>Process Cost | Cost Per<br>Good<br>Package |

| 5                      | 35                | \$16,000   | 2,694             | 0.052              | 99%   | 2,659 | \$5                  | 85%        | 84%                       | 2,260                                   | \$45,295.00           | \$20.04                     |

| 7.1                    | 50                | \$16,000   | 1,319             | 0.052              | 97%   | 1,286 | \$5                  | 85%        | 83%                       | 1,093                                   | \$38,430.00           | \$35.16                     |

| 9.5                    | 90.25             | \$16,000   | 713               | 0.052              | 95%   | 681   | \$5                  | 85%        | 81%                       | 578                                     | \$35,405.00           | \$61.25                     |

| 12.25                  | 150.00            | \$16,000   | 417               | 0.052              | 93%   | 386   | \$5                  | 85%        | 79%                       | 328                                     | \$33,930.00           | \$103.45                    |

| 15                     | 225               | \$16,000   | 270               | 0.052              | 89%   | 240   | \$5                  | 85%        | 76%                       | 204                                     | \$33,200.00           | \$162.75                    |

| 18                     | 324               | \$16,000   | 181               | 0.052              | 85%   | 153   | \$5                  | 85%        | 72%                       | 130                                     | \$32,765.00           | \$252.04                    |

| 21.5                   | 462.25            | \$16,000   | 122               | 0.052              | 79%   | 96    | \$5                  | 85%        | 67%                       | 82                                      | \$32,480.00           | \$396.10                    |

| 25                     | 625               | \$16,000   | 86                | 0.052              | 73%   | 63    | \$5                  | 85%        | 62%                       | 54                                      | \$32,315.00           | \$598.43                    |

| 100    | 4 8 8 |       |      |

|--------|-------|-------|------|

| Wafer  |       | Votor | Coct |

| vvalei |       | valer |      |

| Height / Widt<br>(mm) | h Area (mm²) | Wafer Cost | Dies Per<br>Wafer | D0 (Defects / cm²) | Yield | Cost Per<br>Wafer Bond<br>Step | Bond Yield | Good<br>Package Yield | Good<br>Packages Per<br>Bonded Wafer | Total Process<br>Cost | Cost Per<br>Good Package |

|-----------------------|--------------|------------|-------------------|--------------------|-------|--------------------------------|------------|-----------------------|--------------------------------------|-----------------------|--------------------------|

| 5                     | 25           | \$16,000   | 2,694             | 0.052              | 99%   | \$50                           | 95%        | 93%                   | 2,494                                | \$32,050.00           | \$12.85                  |

| 7.1                   | 50           | \$16,000   | 1,319             | 0.052              | 97%   | \$50                           | 95%        | 90%                   | 1,190                                | \$32,050.00           | \$26.93                  |

| 9.5                   | 80.25        | \$16,000   | 713               | 0.052              | 95%   | \$50                           | 95%        | 87%                   | 617                                  | \$32,050.00           | \$51.94                  |

| 12.25                 | 150.00       | \$16,000   | 417               | 0.052              | 93%   | \$50                           | 95%        | 81%                   | 328                                  | \$32,050.00           | \$94.54                  |

| 15                    | 225          | \$16,000   | 270               | 0.052              | 89%   | \$50                           | 95%        | 75%                   | 203                                  | \$32,050.00           | \$157.88                 |

| 18                    | 324          | \$16,000   | 181               | 0.052              | 85%   | \$50                           | 95%        | 68%                   | 123                                  | \$32,050.00           | \$260.57                 |

| 21.5                  | 462.25       | \$16,000   | 122               | 0.052              | 79%   | \$50                           | 95%        | 59%                   | 72                                   | \$32,050.00           | \$445.14                 |

| 25                    | 625          | \$16,000   | 86                | 0.052              | 73%   | \$50                           | 95%        | 50%                   | 44                                   | \$32,050.00           | \$728.41                 |

- № 堆叠互联:FC/WLP/2.5D/3D四大方案助力封装技术迭代结构升维

- OA 设备: 传统工艺升级&先进技术促前道设备增量

- 05 相关标的

- 06 风险提示

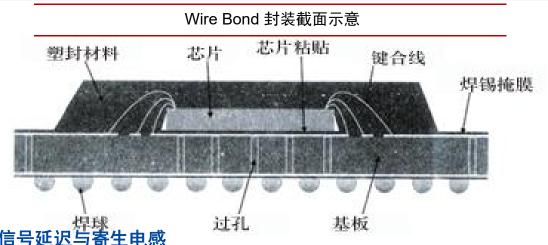

### 3.1.1FC Vs.引线键合:信号路径优化、散热性能提升、I/O引脚密度增加

倒装芯片(Flip Chip)技术是一种将芯片正面朝下、通过凸点(bump)直接与基板连接的封装方式。不同于引线键合的周 边布线,倒装芯片采用区域阵列式分布的连接方式,大大提高互连密度,缩短了信号传输路径。倒装芯片技术也被称为倒装 键合或覆晶接合。

#### ①信号路径优化

省去键合丝, 信号直接通过凸点与基板连接, 缩短信号路径, 有效减了信号延迟和 寄生电感, 为高速数据传输提供可能。

#### ②散热性能提升

芯片与封装基板之间的直接连接, 使得热量能够更高效地传导至基板, 并通过散热 系统散发出去,显著提高散热性能,为高性能、高功耗芯片的稳定运行提供保障。

#### ③I/O引脚密度增加

倒装芯片技术允许在芯片表面布置更多、更密集的凸点,从而实现更高的I/O引脚密 度,有效节省封装面积,为小型化、集成化提供技术支持,特别适用于高性能、高 集成度的应用场景。

#### ①信号延迟与寄生申感

键合丝不仅增加信号传输的路径长度,还引入不可忽视的寄生电感,这对于高速信 号传输而言,无疑是一大障碍。

#### ②散热性能

线键合方式下,芯片产生的热量需要通过芯片背面的散热路径传导至封装基板,效 率相对较低,限制了芯片在高功率密度应用中的表现。

#### ③引脚密度与面积限制

受限于键合丝的物理尺寸和布局空间,线键合技术的I/O引脚密度难以大幅提升,难 以满足日益增长的集成度需求。

### 3.1.2FC所需设备/材料供应商

• DISCO

Accretech

Okamoto

#### 华发集团控股公司

### **Back grinding and CMP**

Dicing

EQUIPMENT: mechanical, laser

MATERIALS: slurry EQUIPMENT

- FujiFilm

- Fujimi

DISCO

Accretech

ASM PT

- Dupont

- CMC Materials

- Resonac

### **Encapsulant**

#### MATERIALS: Epoxy

- Henkel

- Nagase

- Sumimoto

- Hitachi

- Shin- Etsu

# Die Die

#### Pick & Place

#### **EQUIPMENT**

- Besi

- Hanmi

- Hanwha

- SEMES

- Toray

- Shibaura

- ASM PT

- TDK

- Kulicke&Soffa

# Dielectric: underfill, passivation and photoresists

#### **MATERIALS: Dielectrics**

- Merck

- Fujifilm

- JSR

- Asahi Kasei

- Shin-Etsu

- Sumitomo

- Dupont

- AGC

- Toray

- HD Microsystems

- Nippon Kayaku

- TOK

### Lithography

#### **EQUIPMENT:**

- Veeco

- SUSS MicroTec

- ORC

- Nikon

- Canon

- SMEE

- Onto Innovation

- EVG

### **Test & Inspection**

#### **EQUIPMENT**:

- Onto Innovation

- Confovis

- Camtek

- CyberOptics

- FormFactor

- Unity SC

- KLA

#### **Metallization: RDL**

EQUIPMENT: PVD/PECVD EQUIPMENT: Plating

- KLA/SPTS

- Evatec

- Tango Systems

- ULVAC

- Canon

- AMAT

- NEXX/TEL

- Veeco

- Lam Research

- Shibaura

### Atotech

- SEMSYSCO

- TEL

- Ebara

- AMAT

#### MATERIALS: Underfill

- Henkel

- NAGASE

- SUMIMOTO

- Toray

- Hitachi

- NAMICS

### 3.1.3规模: FCBGA/FCCSP出货量稳步增长

长 发 集 闭 控 股 公 司

1000

500

### 3.1.3应用:消费电子为FCBGA及FCCSP首要应用市场

25Q1E

25Q2E

22Q3

22Q4

23Q1

23Q2

23Q3

23Q4

24Q1

24Q2

24Q3E

22Q2

25Q3E 25Q4E 26Q1E 26Q2E

Mobile&Consumer

毕 发 集 团 控 股 公 司

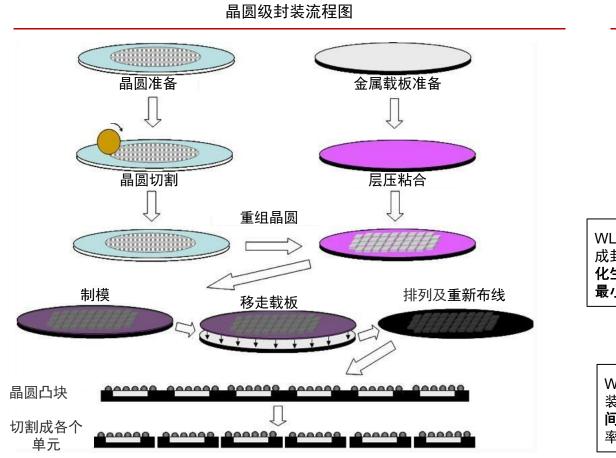

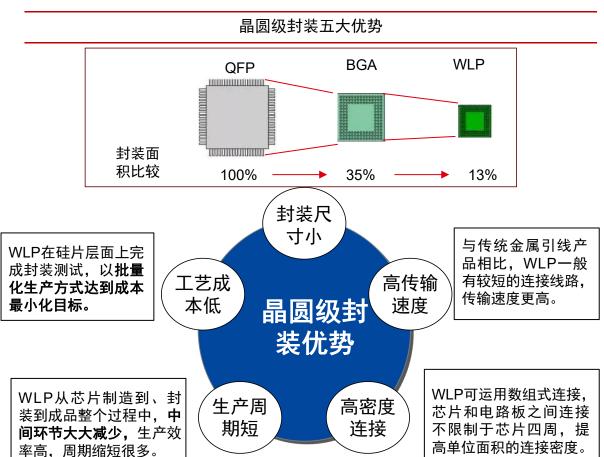

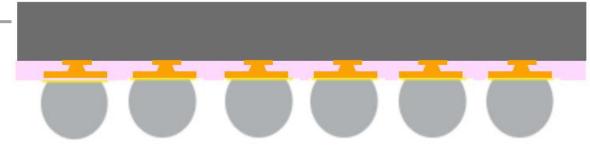

- ◆ 晶圆级封装是指先在整片晶圆上同时对众多芯片进行封装、测试,最后切割成单个器件,并直接贴装到基板或PCB上,生产 成本大幅降低。

- ◆ 由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。

### 3.2.1分类: WLP依据芯片/封装大小划分扇入/出

4 发 集 团 控 股 公 司

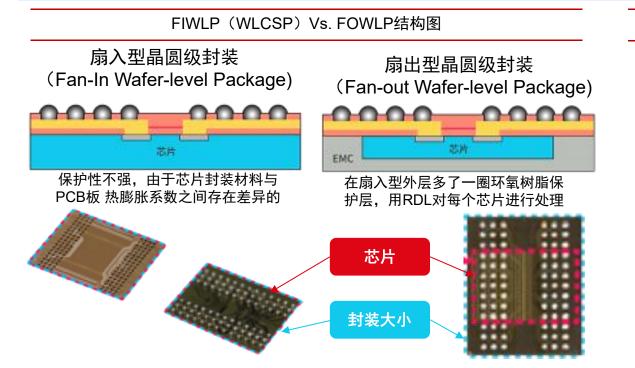

- ◆ "扇(Fan)"指芯片大小。扇入型晶圆级封装(FI-WLP):芯片大小与封装大小相同,且封装用锡球在芯片大小内;扇 出型晶圆级封装(FO-WLP):封装尺寸大于芯片尺寸且部分锡球在芯片之外。

- ◆ FI-WLP具有真正裸片尺寸的显著特点,通常用于低输入/输出(I/O)数量(一般小于400)和较小裸片尺寸工艺当中; FO-WLP初始用于将独立的裸片重新组装或重新配置到晶圆工艺中,并以此为基础,通过批量处理、构建和金属化结构,Fan-Out的Bump可以长到Die外部,封装后IC也较Die面积大(1.2倍最大)。

FIWLP (WLCSP) Vs. FOWLP bump分布

# 3.2.1分类: FOWLP依据Chip/RDL工艺先后类别进一步划分

华发集团控股公司

◆ FOWLP封装技术主要分为Chip first以及Chip last (RDL first),而Chip first可再分为Die face 及Die face down。Chip-first是在生成RDL之前,先将Die附着在一个临时或者永久材料架构上的工艺、而Chip-last则是先生成RDL,再导入Die。封装厂商若要做出精良扇出型封装,只能采用Chip last技术路线。

### FOWLP三大子类封装流程

### RDL on carrier Face-down die attach Face-up attach Cu-stud die Molding Face-down attach, reflow Molding Expose Cu studs Molding Carrier removal Carrier removal RDL and ball attach RDL and ball attach Carrier removal Ball attach Chip first, Die face down Chip last, Die face down Chip first, Die face up (eWLB、日月光集团FOCoS) (安靠科拉 SWIFT) (InFO)

### FOWLP三大子类对比

|        | Chip first, Die face<br>down | Chip first, Die face<br>up | Chip last, Die face<br>up |

|--------|------------------------------|----------------------------|---------------------------|

| 示意图    | CHIp                         | EMC<br>Cu Piller polymer   |                           |

| 翘曲控制   | Good                         | Better                     | Best                      |

| 晶片偏移控制 | Good                         | Better                     | Best                      |

| 铜凸块    | No                           | Yes                        | Yes                       |

| 回流焊    | No                           | No                         | Yes                       |

| 底部填充   | No                           | No                         | Yes                       |

| 晶片表面保护 | No                           | Yes                        | Yes                       |

| 成本     | High                         | Higher                     | Highest                   |

- (1)芯片只会在合格的RDL上倒装芯片,可避免芯片损失,适用于高价格的高端芯片。

- (2) 芯片通过倒装方式直接与RDL连接,消除了芯片偏移问题。

- (3) 超细RDL线宽线距实现HDFO, RDL线宽线距能力<2um。

# 3.2.2WLCSP所需设备/材料供应商

**EQUIPMENT**

Accretech

Okamoto

• DISCO

### **Back grinding and CMP**

MATERIALS: slurry

- FujiFilm

- Fujimi

- Dupont

- CMC Materials

- Resonac

### **Dicing**

**EQUIPMENT**: mechanical, laser

- DISCO

- Accretech

- ASM PT

### Pick & Place

### **EQUIPMENT**

- Besi

- Hanmi

- Hanwha

- SEMES

- Toray

- Shibaura

- ASM PT

- TDK

- Kulicke&Soffa

# Dielectric: underfill, passivation and photoresists

MATERIALS: Dielectrics

- Merck

- Fujifilm

- JSR

- Asahi Kasei

- Shin-Etsu

- Sumitomo

- Dupont

- AGC

- Toray

- HD Microsystems

- Nippon Kayaku

- TOK

### Lithography

### **EQUIPMENT:**

- Veeco

- USHIO

- SUSS MicroTec

- Nikon

- Canon

- SMEE

- Onto Innovation

- EVG

### **Test & Inspection**

### **EQUIPMENT**:

- Onto Innovation

- Confovis

- Camtek

- CyberOptics

- FormFactor

- Unity SC

- KLA

### **Metallization: RDL**

EQUIPMENT: PVD/PECVD EQUIPMENT: Plating

- KLA/SPTS

- Evatec

- Tango Systems

- ULVAC

- Canon

- AMAT

- NEXX/TEL

- Veeco

- Lam Research

- Shibaura

- Atotech

- SEMSYSCO

- TEL

- Ebara

- AMAT

### MATERIALS: Underfill

- Henkel

- NAGASE

- SUMIMOTO

- Toray

- Hitachi

- NAMICS

# 3.2.2FOWLP所需设备/材料供应商

### 团 控 股 公 司

### **Mold Compound Encapsulant**

### MATERIALS: Epoxy **Mold Compound**

- Nagase

- Henkel

- Sumitomo

- Nitto-Denko

- Hitachi

- Panasonic

- Shin-Etsu

### **EQUIPMENT**: **Molding Tool**

- ASM

- Towa

- Yamada

- Hanmi

- Besi

# Temporary bonding/debonding solution MATERIALS: Laminated adhesive MATERIALS: Class bard corrier

# tapes

- Nitto Denko

- JSR

- **Brewer Science**

- 3M

- Shin-Etsu

- Wacker

- TOK

- **HD Microsystems**

- Nissan Chemical

### MATERIALS: Glass hard carrier

- Cornina

- Schott

- AGC

- NGK

- NEG

### **EQUIPMENT:**

- EVG

- ERS electronic

- SUSS MicroTec

- Tazmo

- TEL

- **EO** Technics

- Kingyoup Optronic

### Lithography

### **EQUIPMENT:**

- Veeco

- SUSS MicroTec

- ORC

- Nikon

- Canon

- SMEE

- Onto Innovation

- **EVG**

Besi

Amicra

Capcon

### **Test & Inspection**

### **EQUIPMENT:**

Onto Innovation

**ASM PT**

Shinkawa

Kulicke&Soffa

- Camtek

- Unity SC

- **Nanometrics**

- Xradia

- KLA

# **Metallization: RDL**

### EQUIPMENT: PVD/PECVD EQUIPMENT: Plating

- KLA / SPTS

- Evatec

- Tango Systems

- ULVAC

- Canon

- AMAT

- NEXX/TEL

- Veeco

- Lam Research

- Shibaura

- Atotech

- SEMSYSCO Novellus/TEL

- Ebara

- AMAT

### **Dielectric:** passivation and photo-resists

### **MATERIALS: Dielectrics**

- Merck

- Toray

- Fujifilm

- HD

JSR

- Microsystems

- Shin-Etsu

- Asahi Kasei Nippon Kayaku TOK

- Sumitomo

- Dupont

- AGC

Pick & Place(EQUIPMENT)

Hanmi

Shibaura

Toray

# 3.2.3规模: 29年WLCSP预计规模为24亿美元; FO预计规模为43亿美元■

# 3.2.4应用:晶圆级封装严重依赖移动和消费终端市场

# 3.3.1 2.5D封装 Vs.3D封装

华 发 集 团 控 股 公 司

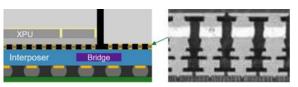

- ◆ 2.5D封装:将处理器、记忆体或是其他芯片,并列排在硅中介板上,经由微凸块连结,让硅中介板之内金属线可连接不同芯片电子讯号;再透过硅穿孔(TSV)来连结下方金属凸块,再经由导线载板连结外部金属球,实现芯片、芯片与封装基板之间互连。

- ◆ 3D封装和2.5D封装的主要区别在于: 2.5D封装是在中介层Interposer上进行布线和打孔, 而3D封装是直接在芯片上打孔和布线, 连接上下层芯片。

#

# (Micro bump) 金屬凸塊 (Solder bump) 2.5D封裝 記憶體 の穿孔(TSV) 対装外殻 の中介板 導線載板 外部金屬球

2.5D与3D封装内部结构图

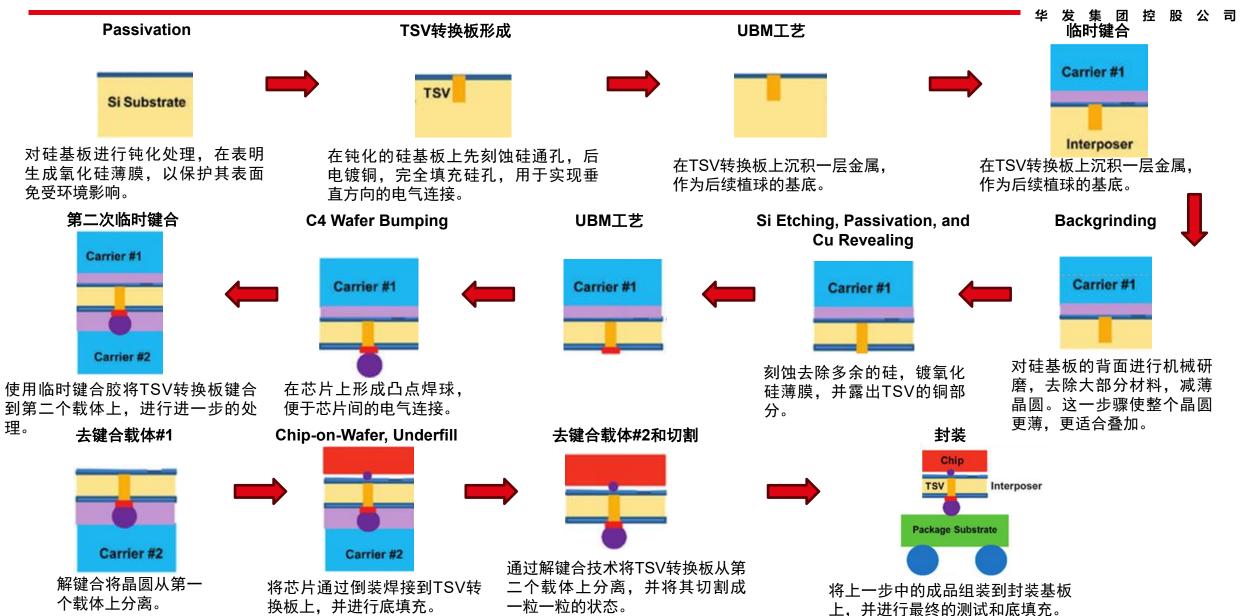

### 3.3.2 2.5D封装:应用实例——CoWoS

华发集团控股公司

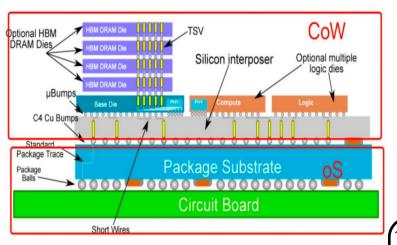

◆ CoWoS严格来说属于2.5D 先进封装技术,CoWoS封装技术主要分为CoW和oS两段。其中,CoW主要整合各种Logic IC(如CPU、GPU、AISC等)及HBM存储器等,另外,oS部分则将上述CoW以凸块(Solder Bump)等接合,封装在基板上,最后再整合到PCBA,成为服务器主机板的主要运算单元,与其他零部件如网络、储存、电源供应单元(PSU)及其他I/O等组成完整的AI 服务器系统。CoWoS由台积电主导,基于interposer(中间介质层)实现的2.5D封装技术,较MCM可提供更高互联带宽及更低互联延时,从而获得更强性能,被广泛应用于GPU芯片中。

### 3.3.2 2.5D封装:应用实例——CoWoS

### 3.3.2 2.5D封装: 应用实例——CoWoS

长 发 集 闭 控 股 公 司

◆ 利用CoWoS封装技术,可使得多颗芯片封装到一起,通过硅中介板互联,达到封装体积小,功耗低,引脚少等效果,故主要目标群体为人工智能、网络和高性能计算应用。CoWoS-S采用硅中介层,为高性能计算应用提供最佳性能及最高晶体管密度;CoWoS-R类似InFO技术,利用RDL中介层进行互连,更强调小芯片间互连;CoWoS-L使用夹层与LSI(局部硅互连)芯片进行互连,使用RDL层进行电源与信号传输,提供最灵活集成。由于基板最小线宽较大(100um),多个die封装且IO较多时,线密度远远不够,故需更小走线密度硅中介板(10um)在中间过渡。

### CoWoS-S(左) Vs.CoWoS-R(中) Vs.CoWoS-L(右)

1.RDL内插器最多由6L铜层组成,用于最小布线。间距为4微 米(2微米线宽/间距)。

- 2、RDL互连提供良好信号及电源完整性性能,以实现高传输 数据速率。

- 3、RDL层和C4/UF层提供良好缓冲效果,减少SoC与衬底间 水膨胀系数失配问题。

# 3.3.2 3D封装:应用实例——HBM

华发集团控股公司

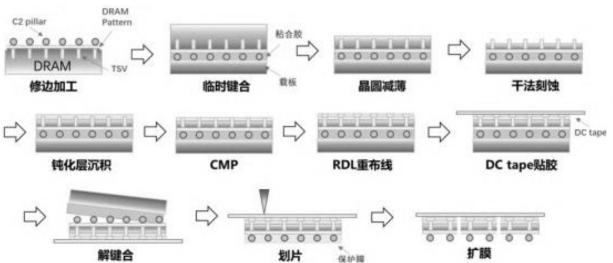

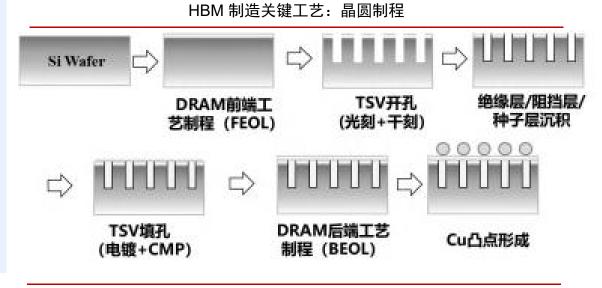

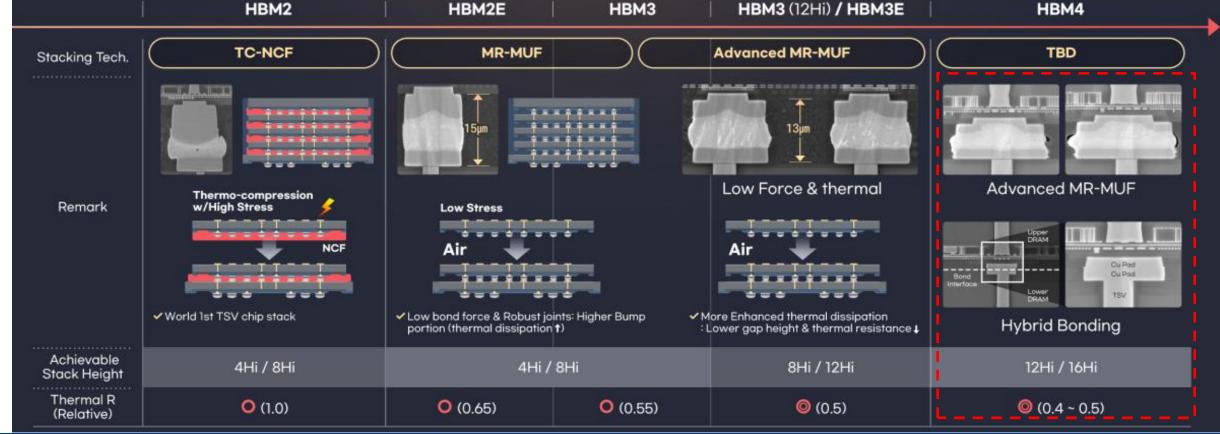

◆ 与传统DRAM晶圆工艺不同,HBM在前端制程(FEOL,包括有源器件和存储单元等功能层)完成后,增加TSV制程,该TSV制程主要包括光刻和干刻、多种沉积镀膜技术、TSV填孔(包括电镀和化学机械抛光 CMP)等工艺步骤。TSV的深度是根据三维堆叠时芯片的厚度而确定的,目前通常在20~30µm左右。完成TSV制程后,会再次进入传统DRAM后端制程进行金属布线,最后形成微凸点。

HBM 制造关键工艺:三维堆叠制程——核心晶圆准备(Die preparation)

HBM 制造关键工艺: 三维堆叠制程——D2W(Die to Wafer)

解键合

塑封膜研磨

修边加工

划片

# 3.3.2 3D封装:应用实例——HBM

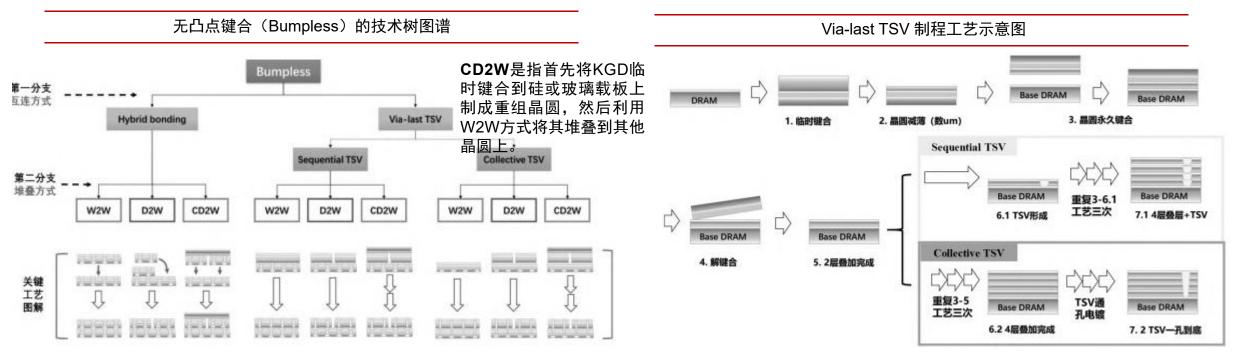

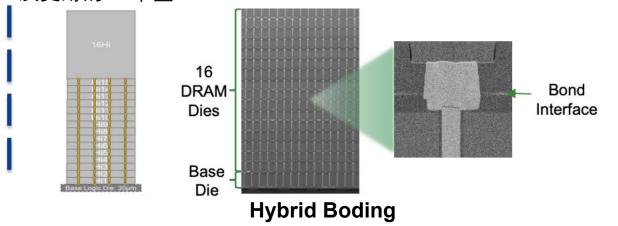

纟 发 集 团 控 股 公 司

- ◆ Bumpless技术大幅度提高HBM性能。增加叠层数和IO总数可有效地提升HBM的内存容量和带宽。堆叠颗粒间的垂直间距是决定可堆叠层数和 I/O密度的关键参数。由于HBM的总厚度是根据系统尺寸而确定的,因此垂直间距越短,可堆叠层数就越多,内存容量越大。另一方面,IO密度与IO的直径成反比,而IO的直径与TSV的纵横比有关。更短的垂直间距有助于减小IO的直径,从而提高IO密度。

- ◆ Via last TSV可分为两种类型: ①Sequential TSV是指交替实施堆叠和TSV的制程,在每层晶圆TSV形成(工艺6.1)之后再叠层(工艺 7.1)。 其优点在于易于管控TSV形貌,且上下叠层电气连通性良好;②Collective TSV是指在完成所有颗粒或晶圆的堆叠后(工艺 6.2)再统一进行 TSV通孔(工艺7.2)的制程,其优点在于TSV工艺只实施一次,简化整个工艺制程,为制作成本效益高的HBM提供有效解决方案。

# 3.3.2 3D封装:应用实例——HBM

华发集团控股公司

| 状态   | 态    互连方式       |                | 堆叠方式         | 性能   | <b></b> | 良率景    | <b>影响</b> | Д    | <b>戈本</b> |

|------|-----------------|----------------|--------------|------|---------|--------|-----------|------|-----------|

| 1人花  |                 |                | <b>华堂</b> 万式 | 叠层间距 | 叠层间电通性  | 晶圆良率影响 | 键合易行性     | 晶圆制程 | 三维堆叠制程    |

| 量产技术 | Cu pilla        | ar bump        | D2W          | ***  | ***     | 无      | ***       | ***  | ***       |

|      |                 |                | W2W          | **** | ****    | 有      | ****      | ***  | ***       |

|      |                 | 键合<br>bonding) | D2W          | **** | ****    | 无      | *         | ***  | **        |

|      | (1. j           | CD2W           | ****         | **** | 无       | **     | ***       | *    |           |

|      | Via-last<br>TSV |                | W2W          | **** | ****    | 有      | ****      | **** | ***       |

| 前沿技术 |                 | Sequential     | D2W          | **** | ****    | 无      | **        | **** | **        |

|      |                 |                | CD2W         | **** | ****    | 无      | ***       | **** | *         |

|      |                 |                | W2W          | **** | **      | 有      | ****      | **** | ****      |

|      |                 | Collective     | D2W          | **** | **      | 无      | **        | **** | ***       |

|      |                 |                | CD2W         | **** | **      | 无      | ***       | **** | **        |

注: ★数越多表示优势越大

# 3.3.2 3D封装:应用实例——HBM

HBM制造对后段工艺设备提出了极高要求,尤其是芯片堆叠 环节中的热压键合(TCB)技术,其精度和良率直接决定 HBM芯片的封装质量、产能与成本。

Fluxless TCB-NCF

混合键合支持小于10µm的互连间距,与传统的基于凸块的堆叠相比,可提供更低的电阻和电容、更高的密度、更佳的热性能以及更薄的3D堆叠。

|      |                                                                 | НВМ3 | НВМ3е | HBM4 | НВ   | M4e    | HBM5    |

|------|-----------------------------------------------------------------|------|-------|------|------|--------|---------|

| 发布   | 年份                                                              | 2023 | 2024  | 2025 | 2026 |        | 2028    |

| 设备   | 机遇                                                              |      |       | C2W  | ТСВ  | Hybrid | Bonding |

| 芯片数量 | TCB                                                             | 8    | 12    | 16   | 1    | 6      | -       |

| 心力效里 | Hybrid                                                          |      |       |      | 1    | 6      | ≥20µm   |

| 互连   | 间距                                                              | 25µm | 22µm  | 20µm | 18   | μm     | <15µm   |

| 基础芯  | 出芯片技术    ≥12nm IDM buffer die      ≤ 4nm advanced foundry logic |      |       |      |      |        |         |

# 3.3.2 2.5D/3D封装所需设备/材料供应商

### 团 控 股 公 司

### DRIE

### MATERIALS: gasses EQUIPMENT: Etcher

AirLiquide

ADEKA

LAM Research

MERCK

AMEC

STREM

KLA / SPTS **AMAT**

LINDE

Naura

### **Back grinding and CMP**

### MATERIALS: slurry

- FujiFIIm

- Fujimi

- Dupont

- **CMC** Materials

- Resonac

### **EQUIPMENT**

- Ebara

- Accretech

### **Temporary bonding/debonding solution: Thinning**

### MATERIALS: adhesive tapes MATERIALS: Glass or Silicon EQUIPMENT:

- Nitto Denko

- Brewer Science

- Shin-Etsu

Pick & Place

**EQUIPMENT**

Hanmi

Toray

Shibaura

SEMES

**ASM PT**

Shinkawa

Kulicke&Soffa

Besi

- **HD Microsystems**

- Nissan Chemical

- Corning

- Schott

- AGC

- **Global Wafers**

- Siltronics

- Sumko

- EVG

- SUSS MicroTec

- TEL

- TOK

### **Dicing**EQUIPMENT: mechanical, plasma, laser

- DISCO **ASM PT**

- Accretech

- Plasma-Therm

### Lithography

### **EQUIPMENT for TSV**

- Canon

- SMEE

- SUSS MicroTec

### **AMAT**

- DISCO

- Okamoto

Test &

Inspection

Onto Innovation

**EQUIPMENT**:

Unity SC

KLA

TEL

**AMAT**

Camtek

### Metallization

### **EQUIPMENT: PVD/PECVD**

- KLA / SPTS

- Canon

- AMAT

- TEL

- Lam Research

### **EQUIPMENT: Plating**

- Atotech

- TEL

- Ebara

- AMAT

- Lam Research

### **Dielectric:** passivation and photo-resists

### **Equipment: Deposition**

- SPTS/Orbotech

- **AMAT**

- LAM Research

- Canon

### MATERIALS: Dielectrics

- Merck

- JSR

- Sumitomo

- Dupont

- **HD Microsystems**

- Nippon Kayaku

- TOK

### 3.3.3 嵌入式封装

华 发 集 团 控 股 公 言

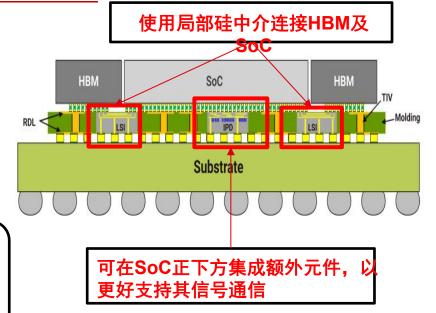

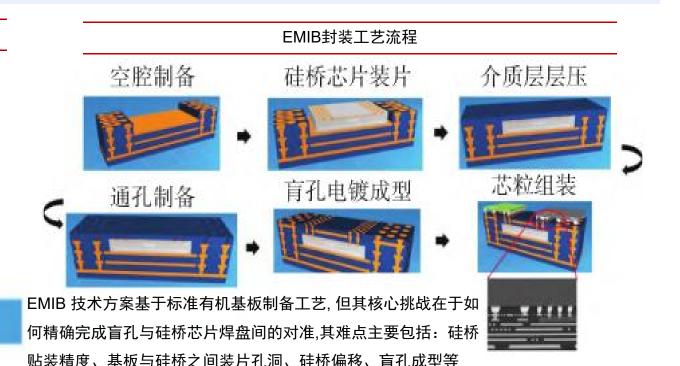

◆ EMIB是属于有基板类封装,因为EMIB也没有TSV,因此也被划分到基于XY平面延伸的先进封装技术。EMIB理念跟基于硅中介层的2.5D封装类似,是通过硅片进行局部高密度互连。与传统2.5封装的相比,因为没有TSV,因此EMIB技术具有正常的封装良率、无需额外工艺和设计简单等优点。传统的SoC芯片,CPU、GPU、内存控制器及IO控制器都只能使用一种工艺制造。采用EMIB技术,CPU、GPU对工艺要求高,可以使用10nm工艺,IO单元、通讯单元可以使用14nm工艺,内存部分则可以使用22nm工艺,采用EMIB先进封装技术可以把三种不同工艺整合到一起成为一个处理器。

# 标准封装互连线 收发芯粒 封装 凸点 封装型封料 Intel® Stretix® 10 FPCA 對裝之板 BMIB

英特尔 EMIB技术相关产品——Stratix10FPGA 产品架构

# 3.3.3 嵌入式封装所需设备/材料供应商

### 华发集团控股公司

### Pick & Place

### **EQUIPMENT**

- Besi

- Amicra

- Capcon

- Hanmi

- Toray

- Shibaura

- ASM PT

- Shinkawa

- Kulicke&Soffa

### **Laser Drill**

### **EQUIPMENT**

- KLA/ Orbotech

- EO Technics

- NIDEC

- MICROMAC

- DISCO

- HANMI

### Metallization

### **EQUIPMENT: PVD/PECVD**

- KLA / SPTS

- Canon

- AMAT

- TEL

- Lam Research

### **EQUIPMENT: Plating**

Atotech

### **Test & Inspection**

### **EQUIPMENT**:

- Onto Innovation

- Camtek

- Unity SC

- Nanometrics

- Xradia

- KLA

### Lithography

### **EQUIPMENT**

- Onto Innovation

- ORC

- SCREEN

- Adtec Engineering

- USHIO

- KLA/Orbotech

### Core:

- Hitachi

- Psnasonic

- MGC

- Doosan

### Prepreg:

- Hitachi

- Panasonic

- MGC

- Doosan

### Buildup

- Ajinomoto

- Duksan

- Doosan

- Hitachi

### Copper Film

**IC Substrate Materials**

- Nippon Denkai

- Mitsui

- Olin Brass

### Photo Resist

- Ashai Kasei

- Hitachi

- JSR Micro

- Fujifilm

### Solder Resist

Hitachi

### **Glass Cloth**

- Ashai Kasei

- Nittobo

- Unitika

# 3.3.4 规模: CIS为2.5D/3D封装主要收入来源, CBA DRAM增速最快

# 3.4 FOPLP:将Die重构在方形载板上进行FO,成本优势明显 1 平置

华金证券

Huajin Securities

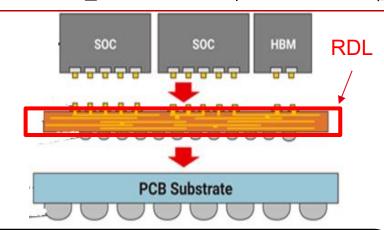

- ◆ 扇出型面板级封装FOPLP是将die重构在更大的方形载板上进行Fan-Out制程的技术,FOPLP能将多个芯片、无源元件互连 集成在一个封装内,提供了更大的灵活性、可扩展性,并通过大批量生产对成本带来显著影响。

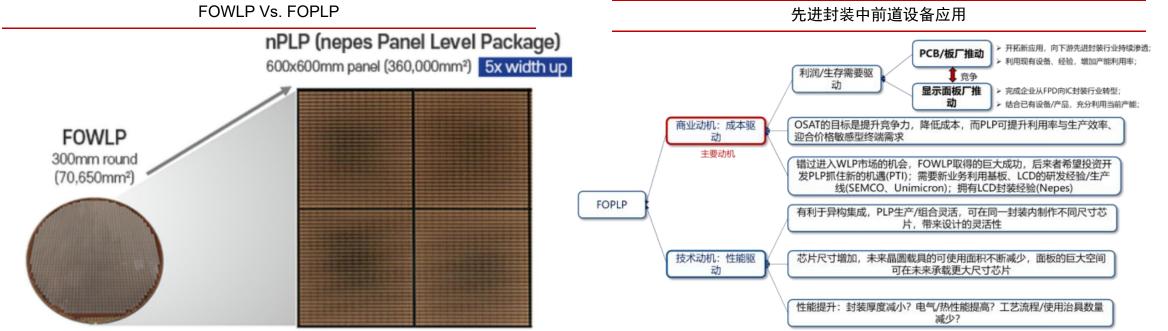

- ◆ 面板级封装的核心竞争力集中体现在成本优势上,也是面板级封装快速发展的最主要驱动因素。以300mm晶圆级封装与515mm×510mm面板级封装对比,面板级封装的芯片占用面积比高达93%,而晶圆级封装仅为64%,这种几何级差距直接引发生产效率(UPH)的显著分化。根据Yole数据显示,扇出型晶圆级封装(FOWLP)技术的面积使用率低于85%,而扇出型面板级封装(FOPLP)面积使用率超过95%,可搭载更多芯片且成本低于FOWLP。从成本数据看,从300mm晶圆级封装转向板级封装可能降低66%成本。FOPLP目前主要应用于中低端市场,随着技术发展,未来可能向高端市场拓展。

先进封装:尖端先进封装需求持续增长,AI相关仍为主要驱动

基础技术: 凸块/重布线层/硅通孔/混合键合构建先进封装基底

堆叠互联: FC/WLP/2.5D/3D四大方案助力封装技术迭代结构升维

设备: 传统工艺升级&先进技术促前道设备增量

相关标的

风险提示

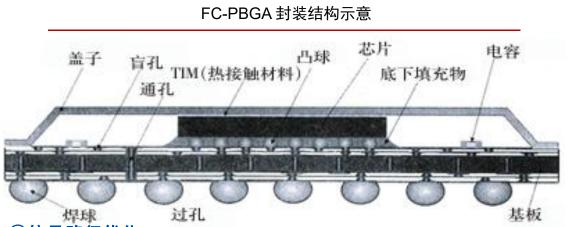

# 4.1设备:晶圆划片前融入封装工艺步骤,前道设备需求加剧

控 股 清洗、光检 植球/电镀 激光刻字 切割成型 注塑 贴片 清洗、光检 引线键合 切割 非先进封装 磨片 清洗机 清洗机 植球机/ 打标机 研磨机 划片机 注塑机 切片机 引线键合机 贴片机 辅助设备 辅助设备 电镀机 植球/电镀 激光刻字 切割成型 光检》 注塑 清洗、光检 贴片 固化 清洗、 切割 磨片 倒装封装 清洗机 清洗机 植球机/ 划片机 打标机 切片机 注塑机 研磨机 回流焊炉 贴片机 辅助设备 辅助设备 申.镀机 清洗、光 注塑 激光刻字 切割成型 固化 划片减薄 贴片 重布线RDL 晶圆植球 晶圆级封装 磨片 检 电镀机、 研磨机、 清洗机 打标机 切片机 固化烤箱 注塑机 研磨机 植球机 贴片机 刻蚀机等 划片机 辅助设备 硅穿孔、 2.5D/3D封 贴片 清洗、光检 注塑 激光刻字 切割成型 注塑 磨片 临时键合 固化 解键合 划片 贴片 重布线RDL 植球 电镀机、 电镀机、 清洗机 贴片机 研磨机 研磨机 解键合机 切片机 贴片机 固化烤箱 注塑机 打标机 切片机 注塑机 ╽┃临时键合机 植球机 刻蚀机等 刻蚀机等 辅助设备

# 4.1设备: 晶圆划片前融入封装工艺步骤, 前道设备需求加剧 🚺 ⋤ 📆

华发集团控股公司

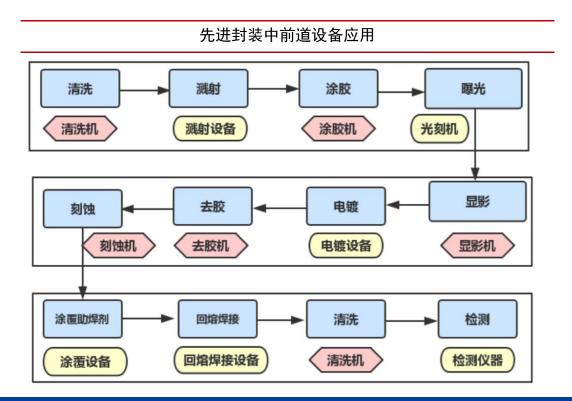

◆ 先进封装处于晶圆制造与封测中的交叉区域。先进封装要求在晶圆划片前融入封装工艺步骤,具体包括应用晶圆研磨薄化、 线路重排(RDL)、凸块制作(Bumping)及三维硅通孔(TSV)等工艺技术。先进封装更多在晶圆层面上进行,采用前道 制造方式来制作后道连接电路,工艺流程的相似性使得两者使用设备也大致相同,其中倒装就要采用植球、电镀、光刻、蚀 刻等前道制造的工艺,2.5D/3D封装TSV技术就需要光刻机、涂胶显影设备、湿法刻蚀设备等,从而使得晶圆制造与封测前 后道制程中出现中道交叉区域。

先进封装开辟"中道"工艺 中道 Middle End 前道 后道 **Front** Back End SiP End CoW Bumping WoW **TSV** 晶圆制造 CoWoS RDL 封测

# 4.2.1减薄机: 在圆片背面采用机械或化学机械方式进行研磨

华发集团控股公司

- 晶圆减薄抛光是为了改善热性能、适应封装需求、增加柔韧性、提高器件性能和良率等目的而进行的。

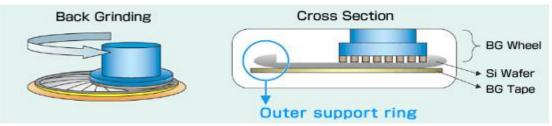

- ◆ 方法: 1、机械磨削: 完全通过物理摩擦力去除晶圆表面的材料,通常有砂轮磨削和研磨两种方式; 2、化学机械研磨(CMP): 研磨液与要抛光的材料先发生轻微化学反应,软化晶圆表面,再用机械研磨去除软化的材料,达到全局平坦化的目的; 3、湿法刻蚀: 使用液态化学药剂来去除晶圆表面的材料; 4、干法刻蚀: 使用等离子体产生的活性基团来去除晶圆表面的材料。

### TAIKO工艺流程图

TAIKO工艺研削

以往的研削

# 4.2.1减薄机: 29年市场有望破13亿美元,日本厂商独占鳌头

华发集团控股公司

◆ 根据未来半导体引用QYResearch数据,2022年全球晶圆减薄设备市场规模约8.3亿美元,预计到2029年增至13.2亿美元,CAGR为6.5%。减薄机复杂程度高、技术攻关难度大、市场准入门槛高,长期被国外厂商高度垄断;全球市场上的主要减薄机生产商包括日本DISCO(迪斯科)、日本TOKYO SEIMITSU(东京精密)、日本KOYO SEIKO(光洋精工)、德国G&N(纽伦堡精密机械)等,全球前三厂商占有85%的市场份额;其中日本DISCO与TOKYO SEIMITSU以出色的产品性能和满意的服务在行业中享有盛誉,2022年两家企业合计市占比已超65%,市场集中度较高。

| 主要企业  | 减薄机产品<br>                                                                                                                      | 图示                                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| DISCO | DISCO的研削机型号包括DFG8340/8540/8541/8561/8640/8830、DGP8761、DAG810。其中,DPG-8761机型在中国大陆市场应用广泛,可稳定地进行厚度在25μm以下的减薄加工。                    | DISCO<br>研削抛光机<br>DGP8761          |

| 东京精密  | 东京精密的减薄研磨机型号为PG3000RMX,可实现15um晶圆高速量产的研磨抛光一体化生产系统。此外,公司还提供高刚性研磨机,分别为HRG3000RM、HRG300/HRG300A、HRG200X。                           | 东京精密<br>减薄研磨机<br>PG3000RMX         |

| G&N   | G&N于1964年开发了世界第一台半导体晶圆研磨机,G&N的减薄研磨机有型号MPS2 R300 CV、MPS R400 CV、MPS R400 CV、MPS R400 CV TWIN、MPS RC Vacuum。可实现TTV≤3um,片差厚度≤2μm。 | G&N<br>減薄研磨机<br>MPS R400 CV        |

| 华海清科  | 华海清科减薄设备有Versatile-GP30和Versatile-GM300。2023年5月,华海清科Versatile-GP300量产机台出机<br>发往集成电路龙头企业,产业化取得重要突破。                             | 华海清科<br>减薄抛光一体机<br>Versatile-GP300 |

| 中国电科  | 中国电科的全自动减薄机型号包括WG1230/1261/1240/1281等,此外还有晶片双面研磨机WP301D、精密研磨机WP4300等。2023年9月,中国电科司8-12寸系列减薄机发货突破百台。                            | 中国电科<br>自动减薄机<br>WG-1220           |

# 4.2.2划片机:将晶圆分割成单个芯片,用于随后的芯片键合

差 发 集 闭 控 股 公 司

|          |                                                |                                                                                                                           | 华发集团控股公司                                                                                                                                 |

|----------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 特征       | 刀片切割 (Blade Dicing)                            | 激光切割 (Laser Dicing)                                                                                                       | 等离子切割 (Plasma Dicing)                                                                                                                    |

| 图示       | 使用高速旋转刀片(通常涂有金) 附石颗粒等磨料),切割半导体 晶圆并分离出单个芯片。     | 高能量激光束被引导到晶圆表面,<br>引发烧蚀/热解的过程,进而沿预<br>定切割线汽化或去除晶圆材料。                                                                      | 该技术使用等离子体(一种由带电粒子组成的电离气体)沿预定的切割线化学去除晶圆材料。                                                                                                |

| 使用范围     | 适用于厚度超过100µm的晶圆                                | 通常用于厚度小于100µm的晶圆                                                                                                          | 主要用于厚度小于30µm的晶圆                                                                                                                          |

| 切割速度     | 10∼50mm/s                                      | 300mm/s                                                                                                                   | 取决于晶圆厚度 (Si: > 20μm/min)                                                                                                                 |

| 芯片强度     | 较低 (碎裂、开裂或变形)                                  | 较低 (激光损伤)                                                                                                                 | 较高                                                                                                                                       |

| 低介电常数适用性 | 不适用 (分层,晶圆使用过程)                                | 适用                                                                                                                        | 适用                                                                                                                                       |

| 优势       | 通用性和与多种半导体材料的兼容性,包括硅、<br>锗和砷化镓。它是一种成熟且成本效益高的技术 | <ul> <li>激光切割是一种非接触式方法,没有物理力施加到晶圆上,减少了切割时的机械应力,降低了碎裂和开裂的风险。</li> <li>激光束可以聚焦到非常小的点,可用于切割复杂的图案,并能够在芯片之间留下最小的间隔。</li> </ul> | <ul> <li>减少晶圆和芯片上机械应力。非接触方法,不涉及任何机械力,适用于脆弱或应力敏感材料,以及具有复杂或精细结构先进半导体器件晶圆。</li> <li>通过调整等离子体参数可以精确控制刻蚀过程,允许进行复杂图案切割并在芯片之间留下最小间隔。</li> </ul> |

| 劣势       | 导致芯片内部精细结构的碎裂、开裂或变形。<br>• 切割过程的摩擦会产生大量热量,可能导致  | 对于大规模生产来说,该过程可能较慢且成本较高。<br>此外,激光类型和参数的选择必须仔细优化,以确<br>保高效的材料去除和最小的热影响区,对于某些材<br>料和厚度来说可能具有挑战性。                             | 过程复杂且耗时,特别是对于厚晶圆或高刻蚀阻力<br>材料。此外,切割所需的专用设备和气体会增加切<br>割过程的总体成本,降低了对大规模生产的吸引力。                                                              |

# 4.2.2划片机: 29年市场有望破25亿美元, 高端市场仍以日本为主

华发集团控股公司

◆ 根据QYResearch调研显示2022年全球划片机市场规模大约为117亿元(人民币),预计2029年全球划片机市场规模将达到 25.2亿美元。在高端精密划片设备领域,日本 DISCO、东京精密 ACCRETECH 占据了该领域较大的市场份额。国产半导体设备与国外产品相比在技术水平上仍有巨大差距,品牌知名度也尚缺,市场竞争能力相对薄弱,在市场中所占的份额很小, 国产半导体设备的替代空间很大。

| 主要企业  | 划片机产品                                                                                                                 | 图示                           |

|-------|-----------------------------------------------------------------------------------------------------------------------|------------------------------|

| DISCO | DISCO的激光切割机型号为DFL系列,刀片切割机型号为DFD系列和DAD系列。2023年12月,DISCO推出全新的SiC(碳化硅)切割设备,可将碳化硅晶圆的切割速度提高10倍,首批产品已交付客户。                  | DISCO<br>激光隐形切割机<br>DFL7362  |

| 东京精密  | 东京精密切割机型号为AD3000/2000/20系列和SS10/20/30系列,激光切割机型号为ML300系列(已停产)。                                                         | 东京精密<br>切割机<br>AD3000T-PLUS  |

| 光力科技  | 光力科技先后在半导体划片机业务板块通过三次海外并购,快速成长为全球排名第三的半导体切割划片设备供应商。光力科技拥有12英寸双轴全自动划片机ADT-8230(定位精度3μm,重复定位1μm)、双轴半自动划片机ADT-6231等系列产品。 | 光力科技<br>双轴全自动划片机<br>ADT-8230 |

| 和研科技  | 和研科技DS系列精密划片机(DS260\9240\9100/9202等型号),以及JS系列全自动切割分选一体机。                                                              | 和研科技<br>划片机<br>DS9260        |

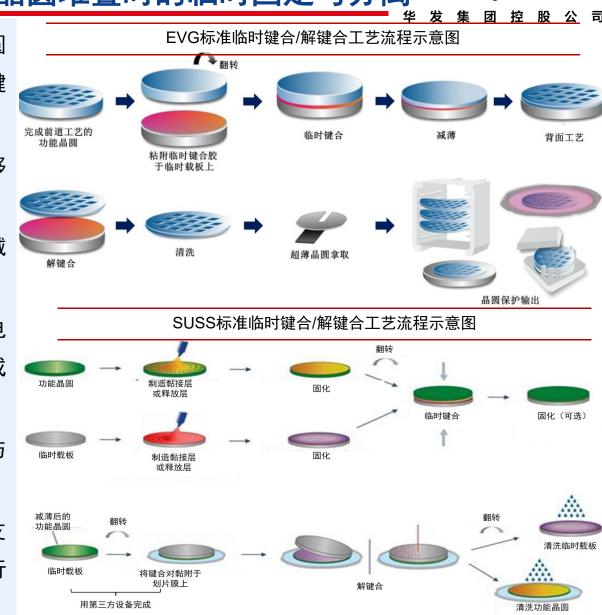

# 4.2.3临时键合/解键合设备:用于3D封装中晶圆堆叠时的临时固定与分离

1 年金证券 Huajin Securities

- 功能晶圆正面完成前道工艺加工后,在临时载板或功能晶圆上通过压合、粘贴或旋涂等方法制造一层中间层材料作为键合黏接剂;

- ◆ 翻转功能晶圆,使其正面与临时载板对准,然后将二者转移 至键合腔进行键合;

- ◆ 完成临时键合后,对功能晶圆进行减薄,减薄一般包括机械研磨、化学抛光等步骤;

- ◆ 完成减薄后,进行深硅刻蚀、扩散阻挡层及种子层沉积、电镀、机械化学抛光、光刻、刻蚀、金属化等背面加工,形成再布线层、TSV等结构;

- ◆ 加工完成后,可以采用不同方式的解键合工艺将功能晶圆与 临时载板分离;

- ◆ 对二者分别进行清洗后,将功能晶圆转移到划片膜或其他支撑系统中,以便进行下一步工艺,临时载板则可以马上进行再次利用。

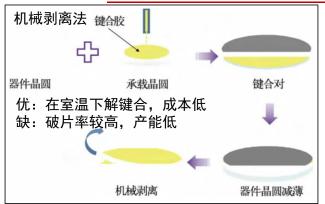

# 4.2.3临时键合/解键合设备: 27年规模有望达1.76亿美元, 仍以进口为主

Huajin Securities

华发集团控股公司

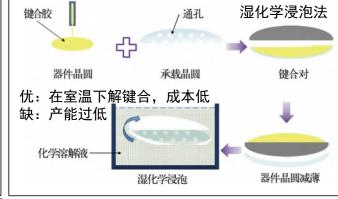

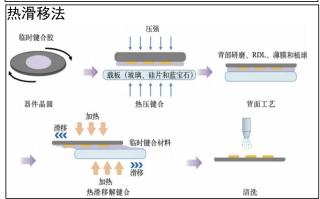

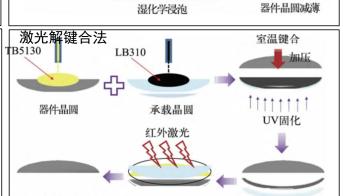

◆ 根据半导体投资联盟引用Yole数据,临时键合/解键合设备市场在2027年有望以7%的CAGR增长到1.76亿美元,目前临时 键合设备市场规模较小,有待下游生产厂商量产技术突破。从解键合设备方面来讲,国内厂商主要为进口设备,如德国 SUSS 研发XBS300 临时键合设备、LD12解键合设备和奥地利 EVG 研发EVG850 系列的临时键合设备和解键合设备。

器件晶圆减薄

### 四种解键合技术原理

优: 工艺简单,成本低

缺:产能低,仅适用小尺寸晶圆解键合

优:产能高,工艺窗口宽,能够满足大于8英寸大尺寸晶圆解键合。缺:设备成本较高

红外激光解键合

### EVG®850 TB Automated Temporary Bonding System

EVG 850临时键合/解键合系统,可临时键合圆片尺寸最高为300mm,可使用超尺寸载板,适用于不同的基材/载体组合。

### EVG®805 Debonding System

EVG 805是一款用于对临时键合和加工晶圆 堆叠进行解键合的系统,该设备支持热脱键 或机械脱键。薄晶圆可卸载到单个基板载体上,以便在设备之间安全可靠地传输。可支 撑最大300mm的晶圆/基板和载体.

无残胶的器件晶圆

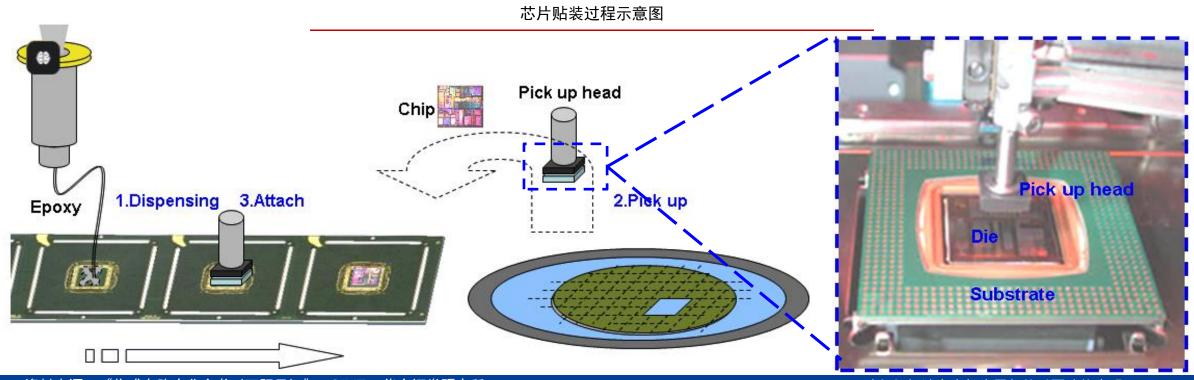

# 4.3.1贴片机:将芯片精确贴装到基板或中介层上

4 发 集 团 控 股 公 司

- ◆ 贴片机主要由承片台、点胶系统、键合头、视觉系统、物料传输系统、上/下机箱及基座等部分组成。键合头完成芯片的拾取 和放置,是完成芯片键合工艺的关键。键合头与承片台相互配合,从蓝膜上准确地拾取芯片,然后与物料传输系统相互配合, 准确地将芯片放置在封装基底涂覆了粘合剂的位置上。接着,对芯片施加压力,在芯片与封装基底之间形成厚度均匀的粘合 剂。

- ◆ 贴片机的关键技术是整机运动控制、芯片拾放和图像识别。对于芯片拾放结果,要求速度快、精度高。

# 4.3.1贴片机: 23年市场规模约10亿美元, ASM/Besi为行业领军企业

华发集团控股公司

◆ 根据松禾资本引用Yole数据,半导体贴片机2023年全球市场规模为10亿美元,2018年-2024年CAGR达到7.43%。贴片机市场基本被国外公司所垄断,2021年ASM和Besi占据全球前两位,CR2在60%左右;国内龙头为华封科技、艾科瑞思、新益昌为主,华封科技在先进封装固晶机领域技术水平较为领先,新益昌以LED贴片机为主。国外固晶机单台售价500万人民币左右,国产固晶机300万人民币左右。

### 贴片机设备比较

|                 | 精度      | 速度UPH   | 价格         |

|-----------------|---------|---------|------------|

| 传统封装贴片机         | 10~25µm | 15~20K  | \$10~20万   |

| 叠层封装贴片机         | 10~25μm | 1.5~3K  | \$30~50万   |

| 倒装封装贴片机         | 5~10µm  | 10~12K  | \$40万      |

| 晶圆级封装贴片机        | 2.5~5µm | 5~8K    | \$60~80万   |

| 2.5D/3D封装贴片机    | 2.5µm   | 2~3K    | \$100~150万 |

| SiP系统级封装贴片<br>机 | 5~10μm  | 100~800 | \$80万      |

| PLP板级封装贴片机      | 3~5µm   | 10K     | \$80~100万  |

- 1) 高集成度高精度:与传统封装相比,先进封装满足芯片高集成度的需求,I/O接口更多,密度更大,精度提高5-7倍;

- **2) 高速度:** 对比传统封装,先进封装中FC封装贴片机提高4倍速度,FO封装贴片机提高三倍速度;

- 3) 高良率: 先进封装贴片机良率大于99%, 为提升利润打好基础。

### 华封科技最新一代高精度贴片机 AvantGo E2

高精度、双动梁4键合头、单轨 道或者双轨道,室温或加热平台

同时处

多种芯片进料方式(晶圆盒, JEDEC料盘, 华夫盘, 卷带机)及自动吸嘴更换,

同时处理多种芯片

独立双晶圆台同时 处理多种芯片

支持最大100x100mm 芯片正、反贴装一体 机

可编程对焦,面向2.5D/3D/叠die/SiP/Chiplet一站式解决方案

键合力120g~5,000g(30g~5,000g, 200g~50Kg可选)并可即时回馈

### 4.3.2TCB: 芯片堆叠中替代倒装回流焊接工艺技术

- 热压键合工艺是属于一种倒装芯片键合工艺,最显著区别于传统的倒装芯片键合工艺是在完成芯片键合工序后,不需要进行 批量回流焊接工序,热压键合过程中通过施加压力和温度在原位数秒内即可实现键合。在键合过程中,温度和压力都需要实 时监控和调整,同时温度、压力和键合头位置需要随键合进程进行复杂工艺调整。

- 通常TCB键合的工艺过程是:首先将助焊剂分配在基板焊盘或芯片的互连凸点上,然后设备的键合头将芯片在机器视觉的引 导下精准地压在基板上对应的焊接位置上,同时将键合头的温度升至焊料熔点以上,最后键合头快速降温至焊料的熔点以下, 当温度降低到设定值时,键合头抬起,键合过程完成。

TCB 键合的 4 种不同工艺

③使用毛细管底部填充技术,即TC-CLF填充

①使用非导电助焊剂,即 TC-NCP

预置填充

这种工艺在键合时需要较长的时间完成键合, 同时当芯片薄至50µm及以下,由于助焊剂控 制要求太高,这种工艺逐渐不适用

②使用非导电膜,即TC-NCF

预置填充

这种工艺目前应用较多,目前是三星和美 光HBM产品封装主要采用的堆叠键合工艺 由于芯片变薄和凸点节距变小, 以及需要 对助焊剂残留物清洗等, 限制毛细管底部 回流填充技术发展应用

④使用液态环氧塑封料作为底部填充,即TC-

シに MUF **后填充**

这种工艺的散热效率和生产效率较高,目前 是韩国海力士主要采用的工艺技术

典型热压键合设备技术指标

| 项目             | 参数说明                              |  |

|----------------|-----------------------------------|--|

| 芯片尺寸/mm×mm     | 2×2~33×33                         |  |

| 晶圆尺寸/mm        | 200~300                           |  |

| 每小时产能/UPH      | 1000(根据不同的产品,热压工艺等,产能稍有浮动)        |  |

| 键合精度/µm        | ±1.5                              |  |

| 键合头共面度         | 1 μm 每 10 mm                      |  |

| 键合Z方向分辨率/µm    | ±1                                |  |

| 键合力/N          | 最大 300                            |  |

| 键合温度/℃         | 键合头温度最大 400, 基台温度最大 200, 温度均匀性 ±5 |  |

| 升降温速率/(°C·s⁻¹) | 升温 200,降温 100                     |  |

市场占有率。

# 4.3.2TCB: 31年全球规模预计超3亿美元,市场以海外六强为主

- ◆ 根据QYResearch数据,2024年全球热压键合机市场规模大约为1.19亿美元,预计2031年将达到3.17亿美元,2025-2031期 间年复合增长率(CAGR)为14.5%。TCB键合机市场目前呈"六强格局",韩国有韩美半导体、SEMES、韩华SemiTech, 日本有东丽(Toray)、新川(Shinkawa),新加坡则有ASMPT,其中,韩美半导体在HBM TCB键合机市场上拥有最高的

- ◆ TCB设备——CoWoS封装的心脏与技术制高点。1、精准连接:以微米级精度将芯片与中介层或基板对准,通过热压实现铜柱凸点(Cu Pillar)的共晶键合; 2、热应力控制:在高温高压下平衡芯片翘曲,避免微裂纹或界面分层; 3、多层堆叠:支持HBM与逻辑芯片的多次键合,确保信号完整性。

全球 TCB 键合设备主要供应商

| 设备厂商     | 设备厂商国家  | 主要客户            |

|----------|---------|-----------------|

| Hanwha   | 韩国      | SK 海力士          |

| Hanmi    | 韩国      | SK 海力士, 台积电, 美光 |

| SEMES    | 韩国      | 三星电子, 美光        |

| Shinkawa | 日本      | 三星电子, 美光        |

| Toray    | 日本      | 三星电子, 美光        |

| ASMPT    | 新加披(总部) | 英特尔, SK 海力士, 美光 |

| BESI     | 荷兰      | 美光              |

| K&S      | 新加坡     | 美光              |

普莱信智能Loong WS-C2W

# 4.3.3 混合键合设备:用于10µm节距以下,下一代HBM理想解决方案

华 发 集 团 控 股 公 司

◆ 经过验证表明, 热压键合工艺通常适用的节距范围是80~40μm, 对于细间距微凸点, 电镀时凸点之间极小的不均匀也会影响良率和性能, 因此10μm节距以下将会采用混合键合技术。混合键合技术互连密度更高, 节距更小, 能效更低, 可以提高芯片间通信速度, 节距可以达到10μm及以下, 是未来应用于下一代HBM产品键合的理想解决方案。目前, 韩国三星与SK海力士正在研发, 预计将会在HBM4产品上使用混合键合技术。

# 4.3.3 混合键合设备: 27年市场规模突破7亿美元, 国内外厂商纷纷入局

华发集团控股公司

◆ 根据隐冠半导体引用Yole数据,2027年W2W和D2W混合键合设备市场空间预计达到5亿/2.3亿美元;当前虽然还没有HBM 应用混合键合,随着堆叠层数增加、集成度要求更高,2028年混合键合工艺预计将占据HBM所用工艺的36%。根据隐冠半导体引用Besi预测中性假设下,2030年对混合键合系统需求将达到1400台,以200万欧元测算,设备市场累计总空间为28亿 欧元。混合键合已成为全球半导体设备厂重点布局方向,包括AMAT、ASMPT、Shibaura、TEL、SUSS等纷纷入局,国内大陆公司包括拓荆科技、华卓精科等。

TCB Micro-bump C2W Vs. Hybrid Bonding

TCB Micro-bump C2W

TCB C2W适用于低密度、性能要求较低

的应用,例如CoW中介层组装

**Hybrid Bonding**

在前端晶圆制造工艺中创建3D IC的

最高性能互连

| TCB Micro-bump C2W | Performance Factor | Hybrid Bonding |

|--------------------|--------------------|----------------|

| 1X                 | 互连密度               | 15X            |

| 1X                 | 速度                 | 11.9X          |

| 1X                 | 带宽密度               | 191X           |

| 1X                 | 节能性能 (EEP)         | >100X          |

| 10X                | 单个互联成本             | 1X             |

### 混合键合设备公司进展(部分)

| 厂商          | 布局进展                                                                                                                  |

|-------------|-----------------------------------------------------------------------------------------------------------------------|

| 拓荆科技        | 1、首台 W2W 产品(Dione 300)顺利通过客户验证,复购设备再次通过验证,实现了产业化应用。<br>2、D2W 混合键合前预处理产品(Propus)通过客户端验证,实现<br>产业化应用。                   |

| 芯慧联         | 1、晶圆混合键合设备-3DSIXI 适用于 12 寸晶圆,可广泛应用于CIS、3D NAND、DRAM、先进封装及其他市场。<br>2、晶圆熔断键合设备适用于 8 寸/12 寸晶圆,可广泛应用于 BSI、<br>半导体光学及其他市场。 |

| 华卓精科        | 以超精密测控技术为基础,开发 HBS 系列全自动晶圆混合键合系统,可实现室温直接键合。                                                                           |

| BESLUDZWI   | 全球 D2W 键合核心玩家, 21 年起获得客户验证订单, 22Q2 产品量产,目前已成为供货台积电 SolC 方案。                                                           |

| ASMPT (D2W) | 2021 年与 EVG 联合开发 D2W 混合键合机 LithoBolt™。                                                                                |

# 4.4先进互连与再布线设备

# 4.4.1电镀设备:制造铜柱/TSV/TGV等金属化结构

华 发 集 团 控 股 公 司

- ◆ 半导体电镀设备在晶圆上沉积一层致密、无孔洞、无缝隙等其他缺陷,并且分布均匀的铜,目前半导体电镀已经不限于铜线的沉积,还有锡、锡银合金、镍、金等金属,但是金属铜的沉积依然占据主导地位。铜导线可以降低互联阻抗,降低器件的功耗和成本,提高芯片的速度、集成度、器件密度等。

- ◆ 半导体电镀随着晶圆级封装工艺的发展,在三维硅通孔、重布线、凸块工艺中都需要金属化薄膜沉积工艺,使用电镀工艺进行金属铜、镍、锡、银、金等金属的沉积。

# 芯片制造后道先进封装电镀工艺示意图

### 盛美上海先进封装电镀设备

盛美上海先进封装电镀设备可应用于多通道 先进封装关键电镀步骤,包括pillar、bump 和RDL。该电镀设备也可运用于fan-out、 TSV和TMV工艺。

- - 化控制

高速电镀铜同时实现更好的均匀

- 水平式电镀腔体,无交叉污染

- 可单腔体维护,提高设备正常运 行时间(up time)

- Rubber Seal 技术, 更好的密封 性能

- 第二阳极技术,更好地控制均一性

- 灵活的工序控制

## 4.4.1电镀设备: 2030年电镀设备有望超8.5亿美元,头部集中效应明显

华发集团控股公司

◆ 根据半导体产业研究引用QYResearch数据,2023年全球半导体电镀设备市场规模大约为5.59亿美元,预计2030年将达到8.55亿美元,2024-2030期间年复合增长率(CAGR)为6.0%;全球半导体电镀设备核心厂商有泛林集团、应用材料、盛美上海、ASMPT和TKC等,前五大厂商占有全球大约73%的份额;美国是最大的市场,占有大约68%份额;产品类型而言,全自动电镀设备是最大的细分,占有大约76%的份额;同时就下游来说,后道先进封装是最大的下游领域,占有64%份额。

| 企业    | 主要应用                                     | 市场竞争力             |                                                                                                                                                                                      |

|-------|------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 泛林    | bumps, pillars, pads,<br>RDL, TGV, FLI 等 | 全球 ECD 龙头         | 主要产品包括Kallisto系列、Phoenix系列、SABRE系列、Triton系列,Kallisto系列适用于300x300毫米至51代 (1100x1300毫米)基板的湿法化学处理,可在各种材料(包括有机玻璃和玻璃核心技术)上对小于10微米的结构进行精细线路电镀;                                              |

| 应用材料  | Fan-Out, TSV 等                           | 半导体设备超市           | 主要产品包括Nokota系统,可支持各种封装方案中采用的所有电镀工序,从而扩展了应用材料公司的电化学沉积系统的产品线,系统可以用于铜、锡/银合金、镍、金、锡和钯等最常用的金属;                                                                                             |

| ASMPT | Fan-Out, UBM, RDL 等                      | 全球最大半导体<br>封装设备商  | 主要产品包括Stratus系列,可实现200-300mm的晶圆处理任务,最多可配置六种不同的电镀材料。                                                                                                                                  |

| TKC   | Bump, RDL, Cu Pillar,<br>TSV 等           | 韩国半导体电镀<br>设备领先企业 | 主要产品包括AEGIS系列,应用于先进封装,可实现4-12英寸晶圆处理任务,支持多种晶圆搬运方式;                                                                                                                                    |

| 盛美上海  | Fan-Out, TSV, TMV 等                      | 国产半导体电镀<br>设备领先企业 | 电镀技术包括前道双大马士革电镀Ultra ECP map、TSV 深孔电镀 Ultra ECP 3d、先进封装电镀 Ultra ECP ap和第三代半导体电镀设备 Ultra ECP GIII,其中TSV深孔电镀和前端大马士革电镀技术均采用多阳极技术。在针对高密度封装的电镀领域可以实现2μm超细RDL线的电镀以及包 括铜、镍、锡、银和金在内的各种金属层电镀。 |

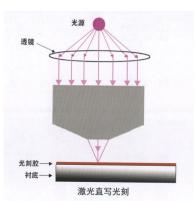

## 4.4.2光刻机:用于再分布层(RDL)、TSV等图形化工艺

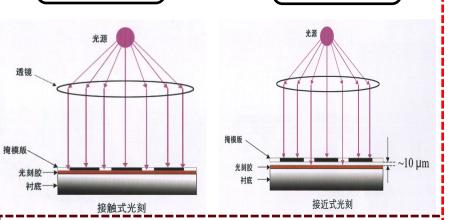

学发集团控股公司 利用掩膜来遮挡和透射光线, 通过聚焦和投射光源在光敏材料上形成图案。掩膜光刻机具 有成熟技术和广泛应用领域,

是芯片制造行业基础设备。

其特点是灵活性高,可柔性制作集成电路。但生产效率很低,一般用于集成电路器件原型的研制验证制作、光刻掩膜版的制作等。

光刻机

在半导体封装(FOWLP、WLCSP、TSV等)过程中,光刻机 主要功能是在芯片封装阶段将精密的电路图案转移到封装基板 或芯片表面,以实现高密度和高性能的电子器件。

有掩膜光刻机

掩膜版与机台距离

电子束直写 光刻机

离子束直写 光刻机

无掩膜光刻机

辐射源不同

acceleration

激光直写光 刻机

接触式光刻机

接近式光刻机

近场菲涅尔衍射成像

远场傅里叶光学成像

投影光刻机

利用计算机输入的地址和图形数据,控制聚焦电子束在涂敷有电子束光刻胶的衬底上直写曝光。该技术最细线条光刻图案可达到2nm。

电子束光刻

象散校正装置 🖂

离子的质量要远大于电子,它能有效地避免电子束散射的问题离子束光刻能获得比电子束光刻更高的分辨率,其最小的分辨率能达到5nm。

利用聚焦激光束直接在涂覆有光刻胶的衬底上描绘图形的光刻技术,通常采用旋转反射镜阵列来实现大量激光束同时扫描的功能,分辨率为500nm到100nm。

调整掩膜版和衬底相对位置和角度实现对准曝光的曝光方式。其理论分辨率可达到0.5um,但由于掩膜版和衬底接触,沾污严重,因此工业生产中一般只在3um以上的情况下采用此方式。目前在研发领域仍然有大规模的应用,在工业领域则集中在LED、MEMS和先进封装等不需要高分辨率的领域。

通过光学投影成像系统,将中间 掩膜版图形按照所需要的倍率缩 小,通过缩小透镜在涂有光刻胶 的衬底表面曝光成像。该类曝光 技术是目前IC生产领域的主流。

# 4.4.2光刻机: 2030年全球先进封装光刻机或突破30亿元,市场集中度高

华发集团控股公司

◆ 根据恒州诚思数据,2023年全球半导体先进封装光刻机市场规模约18.4亿元,预计未来将持续保持平稳增长的态势,到 2030年市场规模将接近30.9亿元,未来六年CAGR为8.3%。全球范围内,先进封装光刻机市场主要集中在头部几家企业手中, 比如K&S、Onto、Ushio、Canon等, Top5份额超过了75%。

上海微电子先进封装光刻机——SSB500系列

SSB500系列步进投 影光刻机主要应用于 集成电路先进封装领 域,包括Flip Chip、 Fan-In、Fan-Out WLP/PLP和2.5D/3D 等先进封装形式,可 满足Bumping、RDL 和TSV等制程的晶圆 级/方板级光刻工艺 需求。

## ①出色的污染防护

全折射式投影物镜提供了超长工作距,以及封闭式的物镜和照明系统,避免光刻胶等有机物挥发造成光路污染。

### ②工艺适应性强

厚胶曝光时可通过调整NA来获得更大焦深,支持高深宽比图形曝光。拥有独特的晶圆传输系统、垂向大行程工件台系统和精密调焦调平系统,可支持Fan-Out制程中的大翘曲片、键合片和厚片曝光工艺。可选配红外或可见光背面对准方式,支持TSV和MEMS等制程所需的背面对准。支持拓展至600mm×600mm方板曝光制程。

### ③高精度

SSB500系列光刻机提供多种投影物镜和曝光光源配置,分辨率可达到0.8~2μm,并具有高线宽均匀性。配置高精度MVS对准系统和低畸变投影物镜,支持特征图形标记和光栅标记,保证了高精度套刻性能。

### ④高产率

SSB500系列光刻机配置了高照度照明系统、高速传输系统、高速高精度运动台系统和大曝光视场,实现高产率,显著降低客户拥有成本。

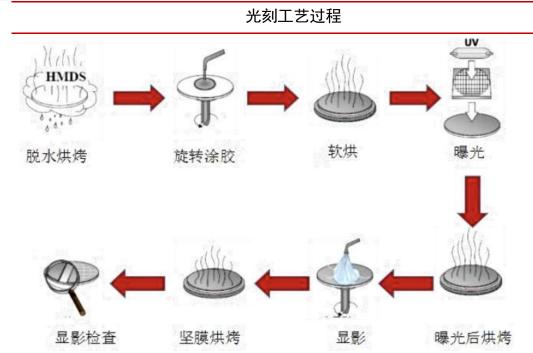

## 4.4.3涂胶显影: 曝光前光刻胶涂覆,输出曝光后图形的显影

华发集团控股公司

- ◆ 涂胶/显影机作为光刻机的输入(曝光前光刻胶涂覆)和输出(曝光后图形的显影),主要通过机械手使晶圆在各系统之间传输和处理,从而完成晶圆的光刻胶涂覆、固化、显影、坚膜等工艺过程,其不仅直接影响到光刻工序细微曝光图案的形成,显影工艺的图形质量对后续蚀刻和离子注入等工艺中图形转移的结果也有着深刻的影响,是集成电路制造过程中不可或缺的关键处理设备。

- ◆ 前道晶圆加工主要与光刻机配合完成晶圆加工过程中的精细光刻工艺流程,对设备精度要求极高,后道先进封装主要用于 Bump、WLCSP、Fanout等后道先进封装技术的涂胶、显影等工序,对设备精度的要求低于前道晶圆加工。

东京电子涂胶显影设备

CLEAN TRACKTM LITHIUS ProTMZ

## 4.4.3涂胶显影: 23年涂胶显影设备规模约40亿美元,东京电子一家独大

Huajin Securities

华发集团控股公司

◆ 国外企业在全球涂胶显影设备市场上仍占据绝对优势。根据鲸芯投资数据,东京电子目前占据全球90%的市场份额,DNS、SUSS、SEMES等企业共同占据全球市场的9%份额,中国企业如芯源微、芯达等占据剩下1%的市场份额。在中国大陆的先进制程生产线中,东京电子一家独大,占据90%以上市场份额。国内成熟工艺生产线,通常使用日本东京电子和迪恩士的早期产品,近年来国内扩产能的晶圆厂也是主要采用这两家公司的二手设备。除了两家日本巨头,德国苏斯、中国台湾省亿力鑫、韩国CND也有少量供应涂胶显影设备;2023年涂胶显影设备的市场规模约为40亿美元。

### 涉及涂胶显影设备企业 (不完全统计)

| 竞争对手         | 公司介绍                                                                                                             |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------|--|--|

| 日本东京电子 (TEL) | <ul><li>领域:前道晶圆加工</li><li>产品:涂胶/显影设备、干法刻蚀设备、湿法清洗设备</li><li>应用:产品系列完整,可用于PI、BARC、SOC、In-line、KRF、ARF等工艺</li></ul> |  |  |

| 日本迪恩士 (DNS)  | <ul><li>领域:前道晶圆加工</li><li>产品:清洗设备、涂胶显影设备、退火设备等</li><li>应用:系列较为完整,可用于PI、BARC、SOC、In-line、KRF、ARF等工艺</li></ul>     |  |  |

| 德国苏斯微 (SUSS) | <ul><li>领域:后道</li><li>产品:高精度光刻设备(如光刻机、旋涂机等)及大规模封装市场用键合机等</li><li>应用:集成电路后道封装、MEMS、OLED、化合物半导体等</li></ul>         |  |  |

| (FLS)        | <ul><li>专注于制造小尺寸全自动黄光制程量产设备</li><li>领域/应用: LED</li><li>产品: 光阻涂布设备、曝光设备、光源清洗设备、显影设备</li></ul>                     |  |  |

| 韩国CND        | <ul><li>专注于设计制造全自动黄光设备</li><li>领域/应用: LED</li><li>产品: 涂胶/显影设备、喷胶设备等</li></ul>                                    |  |  |

| 国内企业  | 产品进度                                            |

|-------|-------------------------------------------------|

| 沈阳芯源微 | 6/8英寸成熟制程设备已大规模出货<br>28nm以下12英寸设备验证中            |

| 上海盛美  | 6/8英寸成熟制程设备已大规模出货<br>2022年首台ArF设备出机             |

| 厦门芯米  | 6/8英寸成熟制程设备已大规模出货<br>12英寸设备首台出货                 |

| 上海众鸿  | 6/8英寸成熟制程设备已大规模出货<br>二手设备起家,目前在自研设备<br>12英寸设备样机 |

| 南京迈瑞捷 | 6英寸设备已出货                                        |

| 苏州容道社 | 6英寸设备已出货<br>二手设备起家,目前在自研设备                      |

| 沈阳芯达  | 6/8英寸成熟制程设备已大规模出货<br>12英寸设备已出货                  |

## 4.4.4刻蚀设备:刻蚀TSV、RDL等结构

半 发 集 团 控 股 公 司

- ◆ **深孔刻蚀是TSV的关键工艺,目前首选技术是基于Bosch工艺的干法刻蚀**。Bosch刻蚀是一种典型的深反应离子刻蚀(Deep reactive ion etching, DRIE)工艺,分为刻蚀和钝化两个循环周期,通常选择ICP刻蚀设备。ICP刻蚀设备通过特设计的双等离子体源实现对腔室内等离子体密度的均匀控制,满足硅高深宽比刻蚀工艺的要求。

- ◆ 该工艺交替使用短步骤的六氟化硫(SF<sub>6</sub>)等离子体来快速且各向同性地消除硅、短步骤的八氟环丁烷(C<sub>4</sub>F<sub>8</sub>)等离子体沉积来保护侧壁。在用SF<sub>6</sub>进行下个刻蚀步骤的第一步时,聚合物层将在特征底部被移除。由于使用"F"自由基进行硅刻蚀,该工艺能提供非常高的刻蚀选择比和蚀刻速率。除了SF<sub>6</sub>和C<sub>4</sub>F<sub>8</sub>以外,硅刻蚀过程的因素如偏置比频率、压强、气流量、温度和占空比等参数,也会影响刻蚀形貌。

Bosch刻蚀工艺示意图

## **Bosch Process**

· Etching, Deep RIE

1. PR patterning

A plasma etching process. (2→3→4)

2. Isotropic etching

- The SF<sub>6</sub> plasma cycle etches silicon (2)

- The C<sub>4</sub>F<sub>8</sub> plasma cycle creates a protection layer. (3→4)

(Plasma : C4 Fe)

4. Passivation etching 5. Isotropic etching (Plasma : SF<sub>e</sub>)

ICP刻蚀设备结构图

ICP刻蚀设备中的射频电源将射频电流导入线圈中,射频电流通过线圈时会产生一个电磁场,引导腔体内部的电子加速运动,加速ssel在英真空容器。速运动的电子与刻蚀工艺气体的分子产生碰撞产生等离子体

产生一个负的偏置电极,吸引带正电的离子

## 4.4.4刻蚀设备:国际巨头主导干法刻蚀,25年规模有望超180亿美元

◆ 根据Gartner数据,2025年全球集成电路制造干法刻蚀设备市场规模预计将增长至181.85亿美元。全球集成电路制造干法 (等离子体)刻蚀设备市场由国际巨头主导。由于刻蚀工艺复杂、技术壁垒高,早期进入市场的国际巨头如泛林半导体、东 京电子、应用材料等拥有领先的技术工艺及客户资源,预计短期内较难被其他竞争对手超越。根据Gartner数据,2020年,

前三大厂商泛林半导体、东京电子及应用材料合计占有全球干法刻蚀设备领域90.24%的市场份额,市场格局高度集中,寡

头垄断现状较难打破。相比之下,国内厂商起步较晚,如中微公司、北方华创、屹唐半导体等企业尚处于追赶阶段,国内集成电路制造厂商及国产刻蚀设备仍有较大的发展空间。

### 北方华创先进封装用刻蚀设

| 刻蚀机类别        | 型号         | 晶圆尺寸               | 适用材料               | 适用工艺                           |

|--------------|------------|--------------------|--------------------|--------------------------------|

| 深硅刻蚀机        | PSE V300   | 8/12 英寸兼容          | 硅、氧化硅、氮化硅          | 2.5D&3D TSV刻蚀、深槽隔离/电容刻蚀、MEMS刻蚀 |

| 封装钝化层刻蚀机     | PSE V300Di | 12英寸               | 氧化硅、氮化硅、PI等有机物、玻璃等 | 掩膜刻蚀、Spacer、有机物刻蚀、大马士革刻蚀等      |

| 等离子体切割刻蚀机    | HSE D300   | 380mm Frame及以<br>下 | 硅                  | 深硅等离子切割                        |

| 深硅刻蚀机        | HSE P300   | 8/12英寸兼容           | 硅、氧化硅、氮化硅          | 深槽刻蚀、深孔刻蚀、扇出型封装硅载体刻蚀、露铜刻蚀等     |

| 微波等离子体表面处理系统 | BMD P300   | 8/12英寸兼容           | PR, PI, PBO, BCB等  | 等离子体表面处理、残渣去除、金属离子去除           |

# 4.4.5薄膜沉积:沉积绝缘介质、导电金属等多层薄膜

半 发 集 团 控 股 公 司

◆ 薄膜沉积设备在先进封装中用于沉积导电层、绝缘层和绝缘层,常用的设备包括原子层沉积(ALD)、化学气相沉积(CVD)和物理气相沉积(PVD)。先进封装(如2.5D/3D封装、晶圆级封装等)需要实现多芯片的垂直堆叠和高密度互连,涉及凸点制造、再分布层(RDL)、硅通孔(TSV)等工艺。这些步骤需要沉积绝缘介质、导电金属等多层薄膜,例如TSV中的绝缘层填充和金属化需要高深宽比的薄膜沉积技术。

### TSV中各层的沉积技术及其特点

| 层类型 | 常见材料             | 沉积技术     | 优势                   | 挑战                          |

|-----|------------------|----------|----------------------|-----------------------------|

| 绝缘层 | 硅氧化物、氧化<br>铝、氮化硅 | CVD, ALD | 提供电气隔离,ALD<br>适合高深宽比 | C V D 覆 盖 性 差,<br>ALD 沉积速度慢 |

| 屏障层 | 氮化钽、氮化钛          | PVD(溅射)  | 防止扩散,覆盖性好            | 高深宽比下步进覆<br>盖率需优化           |

| 种子层 | 铜                | PVD(溅射)  | 提供电镀基础,附着<br>力强      | 高深宽比下覆盖性<br>不足              |

ALD:通过交替的自限化学反应逐原子层沉积,特别适合高深宽比结构如TSV和TGV;

CVD: 通过气相前驱体在关键结构表面反应沉积薄膜,用于沉积关键绝缘层,如隔离和

保护;

PVD:通过物理过程将目标材料蒸发或溅射到基板上,用于沉积金属互连、重分布层 (RDL)和某些种子层。

# 4.4.5薄膜沉积: 24年全球规模约230亿美元,市场被国际知名企业垄断

- ◆ 由于不同芯片结构所需要的薄膜材料种类不同、沉积工序不同、性能指标不同,相应产生巨大的薄膜沉积设备市场,2024 年晶圆制造设备销售额达到约1,042亿美元,约占总体半导体设备销售额的90%。根据历史年度统计,薄膜沉积设备市场规模约占晶圆制造设备市场的22%,由此推算,2024年全球薄膜沉积设备市场规模约为230亿美元。

- ◆ 行业基本由美国的应用材料(AMAT)和泛林半导体(Lam),日本的东京电子(TEL)和迪恩仕(DNS),荷兰的ASML和先晶半导体(ASMI)等为代表的国际知名企业垄断。国际巨头经过几十年发展,凭借资金、技术、客户资源、品牌等方面的优势,占据了薄膜沉积设备市场的大部分份额。在PVD市场,AMAT是绝对龙头;在CVD市场,AMAT、LAM、TEL三家几乎平分秋色;在ALD市场,实现产业化应用的主要为TEL和ASM。

北方华创Polaris Series 硅通孔物理气相沉积系统

适用材料:铜、钛、氮化钛、钽、

氮化钽

适用工艺: 2.5D/3D TSV沉积

### 设备特点

- 专业的磁控溅射源和腔室结构设计有效提高靶材利用率

- 高离化率的磁控溅射源设计带来良好的台阶覆盖率表现

- 针对先进封装领域优化的稳定的传输系统,兼容多种类型的基片

- 专业的偏压基座设计,良好的冷却性能

- 优化的工艺流程带来大产能表现,低运营成本

北方华创Polaris Series 12英寸背面金属物理气相沉积系统

## 设备特点

- 专业的磁控溅射源和腔室结构的设计 有效提高靶材利用率

- · 灵活的腔室配置,优化的工艺流程带 来大产能表现,低运营成本

- 稳定的传输系统,兼容翘曲片、键合 片、薄片等多种类型基片传输

- 良好的颗粒和应力控制能力

适用材料:铝、镍钒、银、钛;适用工艺:背面金属化工艺

适用领域: 功率半导体、先进封装

先进封装:尖端先进封装需求持续增长,AI相关仍为主要驱动

基础技术: 凸块/重布线层/硅通孔/混合键合构建先进封装基底

堆叠互联: FC/WLP/2.5D/3D四大方案助力封装技术迭代结构升维

设备: 传统工艺升级&先进技术促前道设备增量

相关标的

风险提示

# 5.1 ASMPT: 全球领先芯片封装设备制造商

华发集团控股公司

- ◆ ASMPT解决方案范围,从晶圆沉积和激光开槽到其他将精密电子和光学元件成型、组装和封装到范围广泛的最终用户设备中的解决方案,其中包括电子、移动通信、电脑、汽车、工业和 LED(显示器)。ASMPT半导体解决方案分部提供多元化产品如:固晶系统、焊线系统、塑封系统、切筋成型系统及全方位生产线设备。集团的半导体解决方案分部 (SEMI) 还包括: 奥芯明、ALSI、AMICRA、NEXX及AEi团队,以提供客户更广泛的解决方案。

- ◆ 在半导体解决方案(SEMI)业务下,集团推出多项技术创新实例,例如全球首部具有50µm焊垫间距能力的金线焊机 AB339、业界首部可实现35µm超微间距焊线机(Eagle 60焊线机)及TCB(热压式固晶)焊机在细间距高I/O覆晶固晶方面 取得突破。

FIREBIRD TCB 系列——全自动热压式固晶系统

- 并存晶圆及卷带送料

- 可处理框条式基板/单一式基板/晶圆

- 特宽载具处理,适用于单一式基板

- 选配 SlimFEM 系统直接处理晶圆及玻璃基板

可靠的安装基础

• > 250 台已在客户厂房进行量产

创新工艺处理

- 惰性环境, 实现独有的 LPC 制程及高产能

- 实时主动尖端位置倾斜控制

LITHOBOLT™——超高精度混合键合式固晶

ASMPT 的下一代 IC 互连解决方案——LithoBolt™——用于芯片到晶圆 (D2W) 混合键合的混合键合机,使异构集成的整体互连解决方案更臻完善。

- 与前端制程兼容的工具设计

- 为 Chiplet 集成而设计

- D2W 混合键合的灵活工艺能力

# 5.2北方华创:多设备应用于先进封装领域

12 发 集 闭 控 股 公 司

◆ 在先进封装领域,针对Flip chip Bumping、Fan-Out、WLCSP、2.5D/3D TSV等技术,北方华创为客户量身打造的刻蚀设备、沉积设备、炉管设备等已经实现了在主流先进封装企业的批量生产,并不断获得客户的重复采购订单。且公司在HBM 芯片制造和先进封装领域可提供刻蚀、薄膜沉积、热处理、湿法、电镀等多款核心设备。

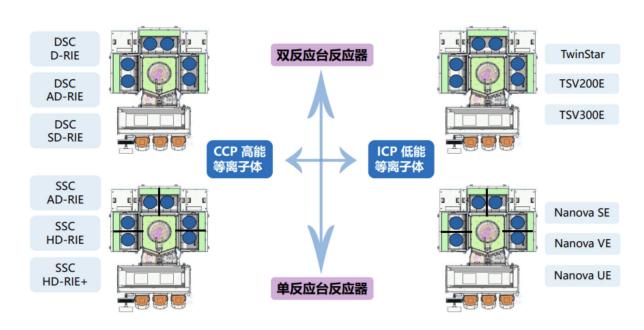

# 5.3中微公司:深硅刻蚀设备在晶圆级/2.5D封装取得重复订单

2024年,公司ICP技术设备类中的8英寸和12英寸深硅刻蚀设备Primo TSV 200E、PrimoTSV 300E在晶圆级先进封装、 2.5D 封装和微机电系统芯片生产线等成熟市场继续获得重复订单的同时,在12英寸的3D芯片的硅通孔刻蚀工艺上得到成功 验证,并在欧洲客户 2英寸微机电系统芯片产线上获得认证的机会,这些新工艺的验证为公司Primo TSV 300E刻蚀设备拓 展了新的市场。公司的等离子体刻蚀设备已应用在国际一线客户从65至5纳米及其他先进的集成电路加工制造生产线及先进 封装生产线。

### 中微公司ICP及TSV设备

ICP 设备

内功率器件、逻辑芯片、储存芯片和新型光 P元件等应用提供高性价比的刻蚀解决方案

## Primo Twin-Star 200

• 双反应台腔体设计

· 低电容耦合 3D 线圈设计

高抽速大容量涡轮泵

可配置 12 路工艺气体

和玻璃品圆加工

• 可选的集成除胶反应腔

精密的腔体及抽气路径温控

• 13 兆赫或 400 干赫脉冲偏压系统

先进的高致密性、耐等离子体侵蚀涂层工艺

双区冷却 9000V 高压静电吸盘:可同时支持硅晶圆

- 双反应台腔体设计

- 多区细分的高动态范围温控静电吸盘

- · 阻抗可调聚焦环设计 AEIT

- 切換式双频偏压系统

· 低电容耦合 3D 线圈设计

• 高抽速大容量涡轮泵

• 可选的集成除胶反应腔

• 轴对称腔体设计

可选的 Durga ESC

- 离子浓度和离子能量独立可控

- 高排气量和更宏的工艺窗口

- 优异的高深宽比刻蚀性能 · 高生产效率, 低生产成本 (CoO)

- 超凡的刻蚀均匀性

## Primo Twin-Star

- · 低电容耦合 3D 线圈设计

- 高抽速大容量涡轮泵

- · 精密的腔体温控和 RF 窗口温控系统

- 先进的高致密性、耐等离子体侵蚀涂层工艺 多区动态温控静电吸盘

- 高排气量和更宽的工艺窗口

· 优异的高深宽比刻蚀性能

· 高生产效率, 低生产成本(CoO)

- 13 兆赫或 400 干赫脉冲偏压系统

- 可选的集成除胶反应腔

超凡的刻蚀均匀性

### 竞争优势

- · 离子浓度和离子能量独立可控 - 离子浓度和离子能量独立可控

- 高排气量和更宏的工艺窗口

- 超凡的刻蚀均匀性

- 优异的高深宽比刻蚀性能 · 高生产效率, 低生产成本 (CoO)

### TSV 设备

### Primo revenue Primo revenue

- 电感式耦合高密度等离子体源的双反应台刻蚀腔 高功率射频等离子体源,并具有连续或脉冲的射

- 具有快速气体转换的内置气箱

- 晶圆边缘保护环

- 制程终端光学控制系统

- 可调节的双发射天线

- 具有适合不同应用的工艺调整性

- 高生产力的主机使每台系统的产能最大化

- 同一反应腔内融合了 Bosch 以及恒稳态制程的工艺性能

中微公司开发CCP单台机和双台机、ICP单台机和双台机可覆盖90%刻蚀应用

# 5.4芯源微: 涉及涂胶显影/临时键合/解键合/湿法设备

坐发集闭控股公司

◆ 公司后道先进封装用涂胶显影设备、单片式湿法设备已连续多年作为主流机型批量应用于台积电、盛合晶微、长电科技、华 天科技、通富微电、珠海天成等一线大厂,已经成为众多知名客户的首选品牌。

| 产品名称 | 后道先进封装涂胶显影机                                                                                                          |  |  |

|------|----------------------------------------------------------------------------------------------------------------------|--|--|

| 产品描述 | ■ 适用于先进封装BGA、Filp-Chip、WLCSP、CSP、2.5D、3D涂胶及显影工艺 ■ 可实现高粘度PR、PI涂胶及多种显影工艺                                               |  |  |

| 产品特点 | <ul> <li>渐进式烘焙,实现温度阶梯控制</li> <li>适用于超厚胶涂覆、显影及烘烤工艺</li> <li>实现超薄晶圆翘曲片传送加工</li> <li>整体已达到国际先进水平,部分指标已实现国际领先</li> </ul> |  |  |

###

| 产品名称 | 临时键合机                                                                                                                                                |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 产品描述 | ■ 适用于三维集成 、2.5D/3D 封装领域, 晶圆减薄过程中超薄晶圆、预减薄晶圆等易碎器件的支撑与保护工艺                                                                                              |  |

| 产品特点 | <ul> <li>■ 业内领先的键合胶旋涂均匀性指标</li> <li>■ 业内领先的键合TTV工艺指标</li> <li>■ 集成高精视觉校准功能/真空传送的键合腔体</li> <li>■ TTV检测技术,实现键合片组闭环检测</li> <li>■ 整体已达到国际先进水平</li> </ul> |  |

| 产品名称 | 解键合机                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------|

| 产品描述 | ■ 适用于三维集成 、2.5D/3D 封装领域,减薄工艺后,器件与玻璃载片的无应力分离及清洗 ■ 可提供激光、机械等多种解键合方案                                       |

| 产品特点 | <ul><li>■ 叠层布置,占地面积小</li><li>■ 平顶化矩形光斑,能量分布均匀</li><li>■ 精确的药液温度、压力、流量控制</li><li>■ 整体已达到国际先进水平</li></ul> |

# 5.5拓荆科技:积极布局三维集成领域的半导体设备

上 发 集 团 控 股 公 司

◆ 公司积极布局并成功进军高端半导体设备的前沿技术领域,研发并推出了应用于三维集成领域的先进键合设备(包括混合键合、熔融键合设备)及配套使用的量检测设备。2024年公司在应用于三维集成领域的先进键合设备及配套量检测设备方面,实现产品销售收入0.96亿元,同比增长48.78%,其中: 晶圆对晶圆混合键合设备、芯片对晶圆键合前表面预处理设备获得重复订单并扩大产业化应用,新推出的键合套准精度量测设备及键合强度检测设备通过客户验证。

### 在三维集成领域的主要应用图示

高帯宽存储器 (HBM) (芯片堆叠≥16层)

# ● 键合: 芯片对晶圆混合键合; 晶圆对晶圆熔融键合;键合精度量测: 晶圆激光剥离

- 键合:晶圆对晶圆混合键合、熔融键合;芯片对晶圆混合键合;键合精度量测:晶圆激光剥离

- 混合键合键合界面: PECVD SiO2、SiCN

- 芯片中间介质层: PECVD SiO,

- 硅通孔: ALD SiO<sub>2</sub>、TiN; SACVD PESAF、SiO<sub>2</sub>

- 应力技术: PECVD Backside SiO<sub>2</sub>、SiN

- 重分布层中介层: PECVD SiO<sub>2</sub>、SiN、SiCN

### 拓荆科技三维集成领域的半导体设备布局

| 产品系列                | 主要产品型号      | 主要应用                 |

|---------------------|-------------|----------------------|

| 晶圆对晶圆混合键合产品         | Dione 300   | 晶圆对晶圆混合键合            |

| 晶圆对晶圆熔融键合产品         | Dione 300F  | 晶圆对晶圆熔融键合            |

| 芯片对晶圆键合前表面预处理产<br>品 | Propus      | 晶圆及切割后芯片的表面活化和清<br>洗 |

| 芯片对晶圆混合键合产品         | Peione      | 芯片对晶圆混合键合            |

| 键合套准精度量测产品          | Crux 300    | 混合键合后的键合套准精度量测       |

| 键合强度检测产品            | Ascella 300 | 晶圆键合后的强度检测           |

重分布层中介层

基底

# 5.6盛美上海:清洗基本盘,积极布局电镀/板级等先进封装领域

盛美上海先进封装设备

除清洗设备外,公司亦积极扩大产品组合,在半 导体电镀设备、半导体抛铜设备、先进封装湿法 设备、立式炉管设备、前道涂胶显影 Track 设备、 等离子体增强化学气相沉积PECVD设备等领域扩 大布局。公司目前三维堆叠电镀设备为主要应用 干填充3D硅通孔TSV的UltraECP3d和2.5D转接板 的UltraECPap。基于盛美半导体电镀设备的平台, 该设备可为高深宽比(深宽比大于10:1)铜应用 提供高性能、无孔洞的镀铜功能。该设备为提高 产能而设计了堆叠式腔体,能减少消耗品的使用, 降低成本,节省设备使用面积。上述设备整体销 量良好。目前、TSV工艺方面、上下游设备及相 关耗材已全部实现国产化,公司的设备能够满足 中国客户的需求,已在中国大陆大部分客户端获 得商业验证并取得重复订单。

电镀设备 应用于晶圆级封装

涂胶设备 应用于晶圆级封装

无应力抛光设备

应用于双大马士革和晶圆级封装

应用于晶圆级封装

面板级先进封装边缘湿法刻蚀设备 应用于PLP面板级边缘刻蚀

面板级先进封装负压清洗设备

湿法去胶设备 应用于晶圆级封装 双管齐下的高效率清洗

面板级先讲封装电镀设备

形成以清洗设备为轴向外拓展,形成"清洗+电镀+先进封装 湿法+立式炉管+涂胶显影Track设备+PECVD+面板级封装" 的七大产品系列,可覆盖前道半导体制造、后道先进封装、 硅片制造三大类工艺设备应用领域, 致力于为全球集成电路 行业提供先进的设备及工艺解决方案。

# 5.7华海清科: CMP/减薄/划切/边缘抛光等多设备入局先进封

华金证券 Huaiin Securities

华发集团控股公司

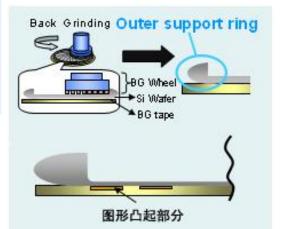

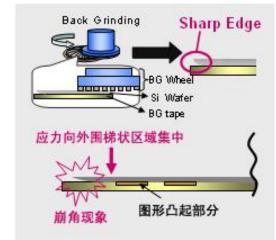

- ◆ (1)CMP:公司高度重视 CMP 产品的技术和性能升级,推出了满足更多材质工艺和更先进制程、先进封装工艺要求的新技术、新模块和新产品,推出的全新抛光系统架构 CMP 机台Universal-H300已经获得批量重复订单,并实现规模化出货;

- (2) 减薄: 12 英寸超精密晶圆减薄机Versatile-GP300已实现多台验收,满足客户批量化生产需求; 12 英寸晶圆减薄贴膜一体机 Versatile-GM300 验证进展顺利。目前公司减薄装备已覆盖存储、CIS、先进封装等多种工艺客户。(3)切划: 研

发出满足集成电路、先进封装等制造工艺的12英寸晶圆边缘切割装备,以解决存储芯片、CIS、先进封装等多种工艺晶圆减

薄时边缘崩边问题,已发往多家客户进行验证。(4)边缘抛光:公司12英寸晶圆边缘抛光装备满足半导体制造领域对高精

度边缘处理的技术要求,已发往多家客户进行验证,并已在存储芯片、先进封装等关键制程中得到应用。

Versatile-GM300

- 可实现全流程自 动化作业

- 卓越的厚度偏差与表面缺陷控制技术

- 高精度、高刚性、 工艺开发灵活

Universal-H300

- 创新抛光系统架构实 现更高效率、更高产 能

- 更加卓越的清洗性能

- 先进控制系统更稳定 可靠

# 5.8芯碁微装:布局直写光刻设备+晶圆对准机+晶圆键合

- 公司晶圆级封装设备在再布线、智能纠偏等核心环节持续优化,通过数字掩模技术与高良品率工艺,全面满足高算力芯片 的制程需求。同时,公司在PLP 板级封装设备领域加速布局,相关产品已应用于模组、光芯片及功率器件封装,技术适配 性获得市场认可。2024年,公司进一步提升封装设备产能效率,针对大面积芯片曝光环节开发的新一代工艺,实现了产能 效率与成品率的双重突破。公司封装设备已获大陆头部客户的连续重复订单,产品的稳定性和功能已经得到验证。

- 2024年4月,公司重磅推出了键合制程解决方案,成功研制新品WA 8晶圆对准机与WB 8晶圆键合机,此两款设备均为半导 体加工过程中的关键设备,可用于先进封装、MEMS生产和需要亚微米级精确对准的应用场景。

### -WI P 2000 WLP 系列-

用于12inch/8inch 集成电路先 进封装领域,包括FlipChip、 Fan-In WLP Fan-OutWLP 和2.5D/3D 等先进封装形式。 该系统采用多光学引擎并行扫 描技术, 具备自动套刻、背部 对准、智能纠偏、WEE/WEP 功能,在RDL、Bumping、 TSV及SOW 等制程工艺中优

### PLP 系列— —PLP 3000/PLP 4000

主要应用干面板级先进封装领 域、包括FC CSP、FCBGA、 Fan-In PLP、Fan-OutPLP和 2.5D/3D 等先进封装形式。可 支持覆铜板,复合材料,玻璃 基板, 该系统采用多光学引擎 并行扫描技术, 具备自动寻边 对准、自动追焦、智能纠偏、 涨缩补偿,在RDL、Bumping、 TSV等制程工艺中优势明显。

### 键合设备--WB 8

晶圆键合机能够实现所有 类型的键合,如阳极键合、 热压键合等。搭载公司核 心技术, 采用半自动化操 作,全系统电气化驱动, 无油污污染,极大提高键 合稳定性和品质。支持最 大晶圆尺寸为8 英寸,可 运用于先进封装、MEMS 等多种半导体应用领域。

势明显。

# 5.9新益昌: 高精度固晶机可用于CoWoS/HBM等封装产品

华 发 集 团 控 股 公 司

- ◆ 公司目前已推出半导体固晶机、焊线机和测试包装设备,封测业务涵盖汽车电子、通信领域、存储、MEMS、模拟、数模混合、分立器件等领域,目前推出的多款先进封装设备也很受市场和客户欢迎。

- ◆ 公司在不断巩固自身现有市场地位的基础上,也通过收购开玖自动化和设立新益昌飞鸿科技,研发生产半导体焊线设备和测试包装设备,实现覆盖半导体封测领域主要节点设备市场,助力公司开辟第二增长曲线,同时公司也在积极推进战略升级,聚焦新型显示及半导体封装领域,加快构建差异化竞争优势。

半导体高精度固晶机(HAD8212advanced)

适用于NAND、DRAM、GPU、CPU、CoWoS、HBM等产品封装。

满足12"wafer,自动导入导出,360°旋转修正;自研高精度直线驱动Bond head,音圈扭力环精确控制Bond force;中转平台图像识别精准校正和UP LOOK二次识别精准校正;

高精度图像视觉定位系统,满足2.5D、3D 叠晶工艺要求;具备MES系统、SECS/GEM。大幅提升精度及稳定性;DieThickness 可达到50um;位置精度±3um,角度±0.1°;Bondforce±5g以内(Force: 30g-3000g)。

### Flip chip 固晶机(HAD812FC)

适用于Flip Chip 封装。

满足12" wafer,自动导入导出,360° 旋转修正;自研高精度直线驱动双Bond head,音圈扭力环精确控制Bond force;中转平台图像识别精准校正和UPLOOK二次识别精准校正;高精度图像视觉定位系统,满足2.5D、3D叠晶工艺要求;具备MES系统、SECS/GEM。

突破性大幅提高FlipChip封装效率、精度;位置精度±5um,角度±0.3°; Bond force±5g以内(Force: 30g-3000g)。

# 5.10光力科技: 国产高端划片切割机第一品牌

- ▶ 自2016年开始进入高端半导体封测装备领域,通过国际并购实现了对英国LP(世界首台半导体划片机的发明者)、LPB

- (国际领先的空气主轴供应商)、以色列ADT(世界第三的先进半导体划片机和软刀供应商)的并购,形成了半导体封测装备板块的初步布局。通过技术引进、消化吸收再创造,完成了先进半导体划片切割机的国产化,打破了国外企业的垄断。公

- 司研发生产的划片切割机可广泛应用在各类半导体产品的封装过程中,现已成为国产高端划片切割机第一品牌。

- ◆ 主要封装设备产品包括:国内基地研发生产的12英寸全自动双轴晶圆切割划片机-8230、8231,以及8230系列高端应用延展机型,例如82WT、8230CF、8230CIS、8230IR等;12英寸半自动双轴晶圆切割划片机-6230、6231、JQ261;用于第三代半导体切割的6英寸半自动单轴切割划片机-6110;用于基板切割的JIG SAW 7260;用于Low-K开槽的激光划片机9130以及12英寸全自动减薄机3230等。

8230 12英寸双轴全自动划片机

8230是一款高精度、高性能的双轴(对向式分布) 12寸全自动划片机,结合全新设计的操作系统,提 供高效,低使用成本的切割体验。

- 设备功能全新升级,品质、效率、操作体验口碑 极佳

- 半导体TOP10封测厂晶圆划片机国产替代首选机型

- 整机核心部件自主可控,不受全球经济政治变化影响

### 6231 12英寸双轴半自动划片机

6231是一款高精度,高效率的双轴划片机,最大加工尺寸可达12寸,在同类型机器中占地面积最小。

- 自动图像识别

- 多种对准模式满足不同需求

- 开发使用最小二乘法算法,保证线弧产品对准

- 支持多片定位全自动对准

- 支持切割序列自主设定

# 5.11华封科技(未上市):聚焦先进封装领域高端装备制造商 📜 ե 료 🛄

华封科技是聚焦先进封装设备领域的高端装备制造商,成熟的设备产品线已获得国际知名半导体封测厂商认可。公司针对半 导体后道工序提供全新一代半导体装嵌及封装设备,如倒装贴片机、晶圆级贴片机,POP封装机,层叠半贴片机,面板级贴 片机,多晶片贴片机等。服务的客户有台积电、日月光、矽品、长电科技、通富微电、DeeTee等。公司主要产品具备高精 度、高速度、高稳定性的特点。产品模块化定制可灵活满足客户定制化需求。产品对先进封装贴片工艺实现了全面覆盖,包 括FOWLP(Face Up/Down)、POP、MCM、EMCP、Stack Die、SIP、2.5D/3D、FCCSP、FCBGA等。

### Capcon AvantGo L6

该设备可前后机同时作业, 最大支持 700mmx750mm载盘冷、熟焊接: 拥 有高精度(±5μm@3σ, ±0.005°@3σ)、高速度(12k UPH)双动梁多键合头;支持最大 100mm×100mm芯片正反贴装;独 立双晶圆台同时处理多种芯片:占地 面积最小至1480x2020x1870mm。 这些指标在很大程度上满足了面板级 封装增大载板尺寸,提高工作效率, 保证一致稳定、提升精度等要求。

Capcon AvantGo L6(机器内部)

→ 基础技术: 凸块/重布线层/硅通孔/混合键合构建先进封装基底

♂ 堆叠互联: FC/WLP/2.5D/3D四大方案助力封装技术迭代结构升维

OA 设备: 传统工艺升级&先进技术促前道设备增量

05 相关标的

# 风险提示

- ◆ 新技术、新工艺、新产品无法如期产业化风险:集成电路封装测试行业属于技术密集型行业,需要紧跟整个行业的发展趋势,及时、高效地研究开发符合市场和客户需求的新技术、新工艺及新产品并实现产业化。如果在技术研发上出现一些波折,不能及时加大资本投入进行新技术的研发,将面临新技术、新工艺、新产品无法如期产业化风险。

- ◆ 市场需求波动风险: 消费电子市场周期性调整可能导致下游需求暂时减缓,叠加行业产能扩张,存在阶段性供过于求风险。设备公司将持续开发新的产品品类,优化产品结构,加强与新能源、AI芯片等新兴领域客户合作,不断提升产品工艺覆盖度和市场占有率。

- ◆ **国际贸易摩擦风险:**伴随全球产业格局深度调整,国际贸易摩擦不断,集成电路产业成为贸易冲突的重点领域,也对中国相关产业的发展造成了客观不利影响。2022年8月以来,美国推出多项贸易管制政策通过限制产品、设备以及技术等项目的出口以限制中国半导体行业的发展。

- ◆ **供应链风险**: 半导体行业依赖复杂的全球供应链。关税和技术出口管制等外部形势的不确定性导致全球供应链风险增加。进口零部件、原材料、耗材采购或周期延长且成本上涨。

# 华金证券研究所电子团队简介

熊军:电子行业首席分析师,东南大学集成电路专业本硕,10年证券行业研究经验,曾就职于国联民生证券、华西证券、东北证券,曾获2022年choice电子最佳分析师,2019年中国证券分析师金翼奖通信行业第一名。产业背景+研究经验丰富,曾就职于Nvidia从事半导体研发工作和赛迪顾问从事半导体行业研究。

王臣复:电子行业高级分析师,北京航空航天大学工学学士和管理学硕士,曾就职于华西证券研究所、欧菲光集团投资部、平安基金等,2023年2月入职华金证券研究所。

宋鹏:电子行业分析师,莫纳什大学硕士,曾就职于头豹研究院TMT组,2023年3月入职华金证券研究所。

吴晟昊: 电子行业分析师, 曾就职于致同会计事务所、华西证券研究所, 2023年3月入职华金证券研究所。

# 评级说明

## 公司投资评级:

买入 — 未来6-12个月内相对同期相关证券市场代表性指数涨幅大于15%;

增持 — 未来6-12个月内相对同期相关证券市场代表性指数涨幅在5%至15%之间;

中性 — 未来6-12个月内相对同期相关证券市场代表性指数涨幅在-5%至5%之间;

减持 — 未来6-12个月内相对同期相关证券市场代表性指数跌幅在5%至15%之间;

卖出 — 未来6-12个月内相对同期相关证券市场代表性指数跌幅大于15%。

## 行业投资评级:

领先大市 — 未来6-12个月内相对同期相关证券市场代表性指数领先10%以上;

同步大市 — 未来6-12个月内相对同期相关证券市场代表性指数涨跌幅介于-10%至10%;

落后大市 — 未来6-12个月内相对同期相关证券市场代表性指数落后10%以上。

## 基准指数说明:

A股市场以沪深300指数为基准;新三板市场以三板成指(针对协议转让标的)或三板做市指数(针对做市转让标的)为基准;香港市场以恒生指数为基准,美股市场以标普500指数为基准。

# 法律声明

## 分析师声明

熊军、宋鹏声明,本人具有中国证券业协会授予的证券投资咨询执业资格,勤勉尽责、诚实守信。本人对本报告的内容和观点负责,保证信息来源合法合规、研究方法专业审慎、研究观点独立公正、分析结论具有合理依据,特此声明。

## 本公司具备证券投资咨询业务资格的说明

华金证券股份有限公司(以下简称"本公司")经中国证券监督管理委员会核准,取得证券投资咨询业务许可。本公司及其投资咨询人员可以为证券投资人或客户提供证券投资分析、预测或者建议等直接或间接的有偿咨询服务。发布证券研究报告,是证券投资咨询业务的一种基本形式,本公司可以对证券及证券相关产品的价值、市场走势或者相关影响因素进行分析,形成证券估值、投资评级等投资分析意见、制作证券研究报告、并向本公司的客户发布。

# 法律声明

## 免责声明:

本报告仅供华金证券股份有限公司(以下简称"本公司")的客户使用。本公司不会因为任何机构或个人接收到本报告而视其为本公司的当然客户。

本报告基于已公开的资料或信息撰写,但本公司不保证该等信息及资料的完整性、准确性。本报告所载的信息、资料、建议及推测仅反映本公司于本报告发布当日的判断,本报告中的证券或投资标的价格、价值及投资带来的收入可能会波动。在不同时期,本公司可能撰写并发布与本报告所载资料、建议及推测不一致的报告。本公司不保证本报告所含信息及资料保持在最新状态,本公司将随时补充、更新和修订有关信息及资料,但不保证及时公开发布。同时,本公司有权对本报告所含信息在不发出通知的情形下做出修改,投资者应当自行关注相应的更新或修改。任何有关本报告的摘要或节选都不代表本报告正式完整的观点,一切须以本公司向客户发布的本报告完整版本为准。

在法律许可的情况下,本公司及所属关联机构可能会持有报告中提到的公司所发行的证券或期权并进行证券或期权交易,也可能为这些公司提供或者争取提供投资银行、财务顾问或者金融产品等相关服务,提请客户充分注意。客户不应将本报告为作出 其投资决策的惟一参考因素,亦不应认为本报告可以取代客户自身的投资判断与决策。在任何情况下,本报告中的信息或所表述的意见均不构成对任何人的投资建议,无论是否已经明示或暗示,本报告不能作为道义的、责任的和法律的依据或者凭证。 在任何情况下,本公司亦不对任何人因使用本报告中的任何内容所引致的任何损失负任何责任。

本报告版权仅为本公司所有,未经事先书面许可,任何机构和个人不得以任何形式翻版、复制、发表、转发、篡改或引用本报告的任何部分。如征得本公司同意进行引用、刊发的,需在允许的范围内使用,并注明出处为"华金证券股份有限公司研究所",且不得对本报告进行任何有悖原意的引用、删节和修改。

华金证券股份有限公司对本声明条款具有惟一修改权和最终解释权。

# 法律声明

## 风险提示: